### EVAL6206Q

### Dual full bridge with programmable overcurrent

Data brief

### **Features**

- Voltage range from 8 to 52 V

- Phase current up to 2.5 A<sub>r.m.s.</sub>

- Adjustable overcurrent threshold

- · Logic inputs 5 V / 3.3 V compliant

- Small application footprint with high thermal performance

- Suitable for use in combination with PractiSPIN™ 2 software

### **Description**

The EVAL6206Q demonstration board allows the user to test the L6206Q functions. The dual full bridges integrated into the L6206Q device can be used to drive a single 2-phase stepper motor or up to four DC motors (unidirectional). The bridges can also operate in parallel mode. The board can be driven using the STEVAL-PCC009V2 demonstration board and the PractiSPIN 2 evaluation software.

Contents EVAL6206Q

## **Contents**

| 1 | Board description                | 3 |

|---|----------------------------------|---|

| 2 | Schematic                        | 5 |

| 3 | Bill of material                 | 6 |

| 4 | Layout                           | 7 |

| 5 | Overcurrent threshold regulation | D |

| 6 | Revision history                 | 1 |

EVAL6206Q Board description

## 1 Board description

**Table 1. Electrical specifications**

| Parameter                                     | Value                      |

|-----------------------------------------------|----------------------------|

| Supply voltage (VS)                           | 8 to 52 V                  |

| Maximum output current (each phase)           | 2.5 A <sub>r.m.s.</sub>    |

| Low level logic input voltage                 | 0 V                        |

| High level logic input voltage                | 5 V / 3.3 V <sup>(1)</sup> |

| Switching frequency                           | Up to 100 kHz              |

| Operating temperature                         | - 25 to +125 °C            |

| L6206Q thermal resistance junction-to-ambient | 17 °C/W                    |

<sup>1.</sup> Logic inputs are 3.3 V and 5 V compliant.

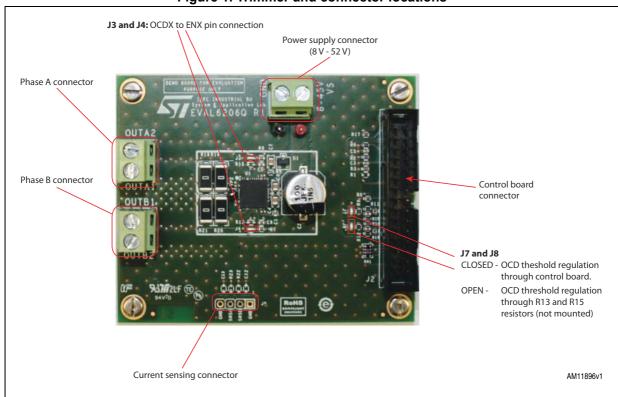

Figure 1. Trimmer and connector locations

Board description EVAL6206Q

Table 2. Control board connector pinout (J2)

| Pin    | Туре           | Function                                          |  |

|--------|----------------|---------------------------------------------------|--|

| 2      | Ground         | Ground                                            |  |

| 3      | Logic input    | Input IN1A of L6206Q                              |  |

| 4      | Logic input    | Input IN2A of L6206Q                              |  |

| 5      | Logic input    | Input IN1B of L6206Q                              |  |

| 6      | Logic input    | Input IN2B of L6206Q                              |  |

| 11     | Analog input   | Overcurrent threshold regulation for A bridge     |  |

| 12     | Analog input   | Overcurrent threshold regulation for B bridge     |  |

| 13     | Ground         | Ground                                            |  |

| 14     | Supply voltage | 3.3 V supply voltage                              |  |

| 16     | Logic input    | Input ENA of L6206Q                               |  |

| 23     | Ground         | Ground                                            |  |

| 24     | Analog output  | Board identification system ID0                   |  |

| 25     | Analog output  | Board identification system ID1                   |  |

| 27     | Logic output   | Fault output for A bridge (OCDA output of L6206Q) |  |

| 28     | Ground         | Ground                                            |  |

| 29     | Logic output   | Fault output for B bridge (OCDB output of L6206Q) |  |

| 30     | Logic input    | Input ENB of L6206Q                               |  |

| Others | Unconnected    |                                                   |  |

Table 3. Current sensing connector (J9)

| Pin | Туре          | Function                            |

|-----|---------------|-------------------------------------|

| 1   | Ground        | Ground                              |

| 2   | Analog output | SENSEA pin of L6206Q <sup>(1)</sup> |

| 3   | Analog output | SENSEB pin of L6206Q <sup>(1)</sup> |

| 4   | Ground        | Ground                              |

The R22/23 resistor and C12/13 capacitor must be added when output is used. The value of the RC network should be chosen according to the target low-pass frequency of the filter.

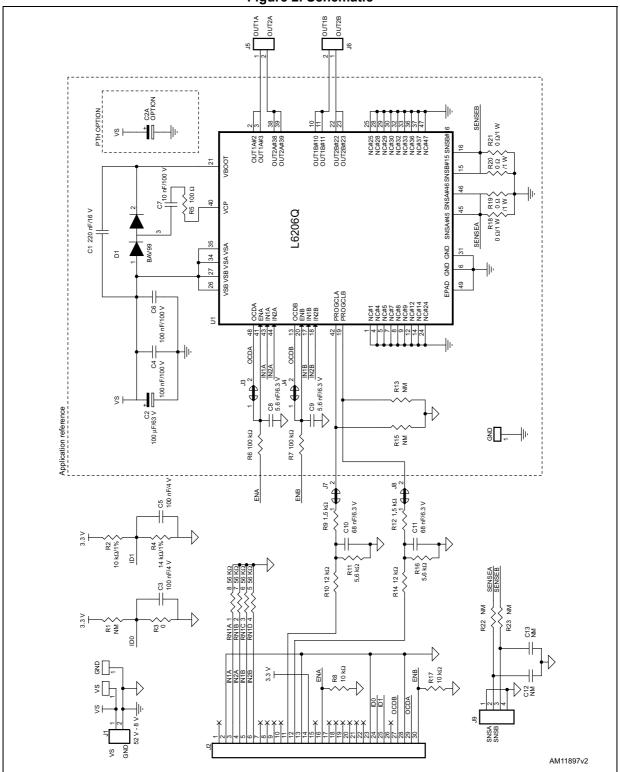

EVAL6206Q **Schematic**

#### **Schematic** 2

Figure 2. Schematic

Bill of material EVAL6206Q

## 3 Bill of material

Table 4. Bill of material

| Index | Quantity | Reference Value           |                                        | Package            |

|-------|----------|---------------------------|----------------------------------------|--------------------|

| 1     | 1        | C1                        | 220 nF / 16 V                          | CAPC-0603          |

| 2     | 1        | C2                        | 100 μF / 63 V                          | CAPES-R10HXX       |

| 3     | 1        | C2A                       | 100 μF / 63 V (OPTION)                 | CAPE-R8H12-P35     |

| 4     | 2        | C3, C5                    | 100 nF / 4 V                           | CAPC-0603          |

| 5     | 2        | C4, C6                    | 100 nF / 100 V                         | CAPC-0805          |

| 6     | 1        | C7                        | 10 nF / 100 V                          | CAPC-0805          |

| 7     | 2        | C8, C9                    | 5.6 nF / 6.3 V                         | CAPC-0603          |

| 8     | 2        | C10, C11                  | 68 nF / 6.3 V                          | CAPC-0603          |

| 9     | 2        | C12, C13                  | NM                                     | CAPC-0603          |

| 10    | 1        | D1                        | BAV99                                  | SOT-23             |

| 11    | 3        | J1, J5, J6                | Screw connector 2 poles                | MORSV-508-2P       |

| 12    | 1        | J2                        | Pol. IDC male header vertical 30 poles | CON-FLAT-15X2-180M |

| 13    | 4        | J3, J4, J7, J8            | Jumper - CLOSE                         | JP2SO              |

| 14    | 1        | J9                        | NM                                     | STRIP254P-M-4      |

| 15    | 1        | RN1                       | 56 kΩ                                  | RESN-CAY16         |

| 16    | 5        | R1, R13, R15, R22,<br>R23 | NM                                     | RESC-0603          |

| 17    | 1        | R2                        | 10 kΩ / 1%                             | RESC-0603          |

| 18    | 1        | R3                        | 0 Ω                                    | RESC-0603          |

| 19    | 1        | R4                        | 14 kΩ / 1%                             | RESC-0603          |

| 20    | 1        | R5                        | 100 Ω                                  | RESC-0603          |

| 21    | 2 R6, R7 |                           | 100 kΩ                                 | RESC-0603          |

| 22    | 2        | R8, R17                   | 10 kΩ                                  | RESC-0603          |

| 23    | 2        | R9, R12                   | 1.5 kΩ                                 | RESC-0603          |

| 24    | 2        | R10, R14                  | 12 kΩ                                  | RESC-0603          |

| 25    | 2        | R11, R16                  | 5.6 kΩ                                 | RESC-0603          |

| 26    | 4        | R18, R19, R20, R21        | 0 Ω / 1 W                              | RESC-2512          |

| 27    | 1        | TP1 TPTH-RING-1MM RED     |                                        | TH                 |

| 28    | 2        | TP2,TP3 TPTH-RING-1MM TH  |                                        | TH                 |

| 29    | 1        | U1 L6206Q                 |                                        | QFN (7x7_48)       |

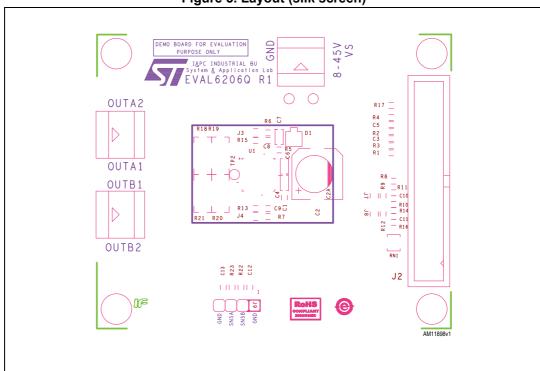

EVAL6206Q Layout

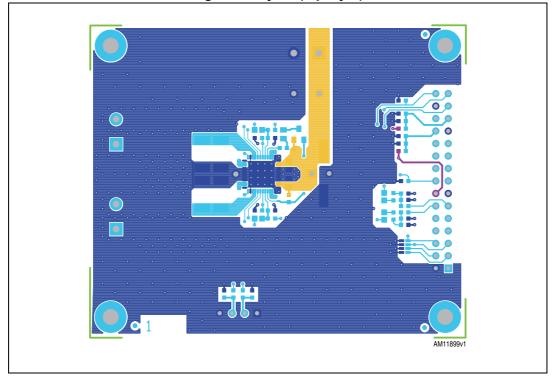

## 4 Layout

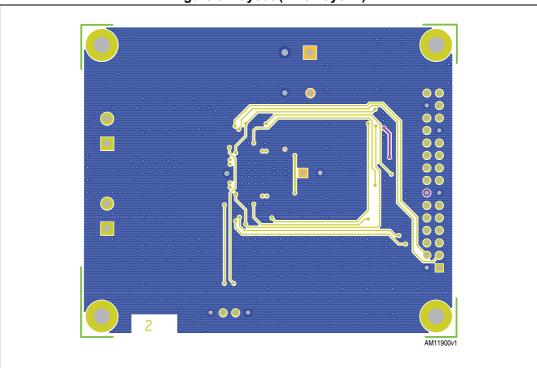

Figure 3. Layout (silk screen)

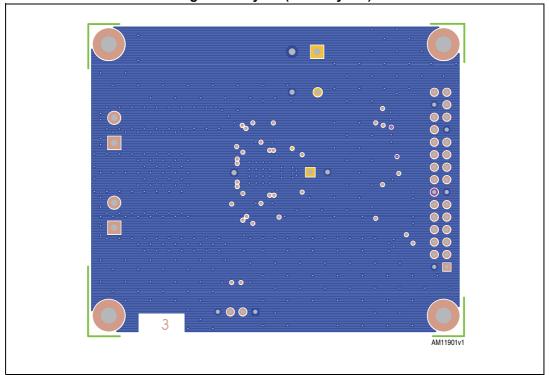

Figure 4. Layout (top layer)

Layout EVAL6206Q

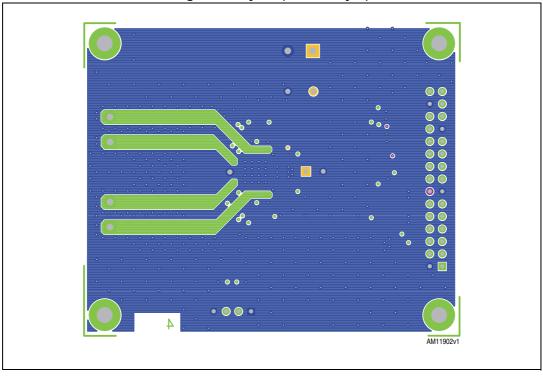

Figure 5. Layout (inner layer 2)

Figure 6. Layout (inner layer 3)

EVAL6206Q Layout

Figure 7. Layout (bottom layer)

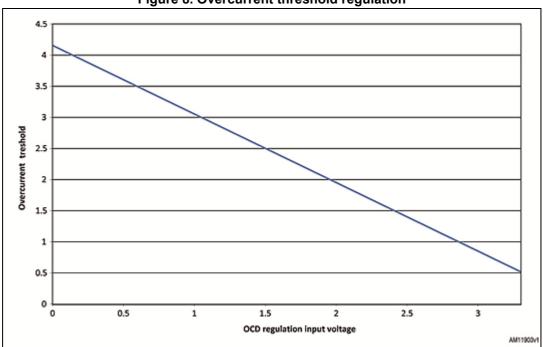

# 5 Overcurrent threshold regulation

Figure 8. Overcurrent threshold regulation

4

EVAL6206Q Revision history

# 6 Revision history

**Table 5. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Apr-2012 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 07-Jun-2013 | 2        | Updated <i>Description on page 1</i> (replaced "communication board" by "demonstration board").  Added <i>Contents</i> on page 2.  Added titles to <i>Section 2: Schematic</i> to <i>Section 5: Overcurrent threshold regulation</i> .  Updated <i>Table 1</i> (added value and unit to "thermal resistance junction-to-ambient", removed superfluous "EVAL6206Q" from title).  Updated <i>Figure 2</i> (removed "EVAL6206Q" from title, completed units, minor modifications).  Updated <i>Table 4</i> (removed "EVAL6206Q" from title, corrected unit in row 26).  Updated <i>Figure 3</i> to <i>Figure 7</i> (removed "EVAL6206Q" from titles).  Minor corrections throughout document. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

12/12 DocID023042 Rev 2