**Monolithic Linear IC**

# PWM Constant-Current Control Stepper Motor Driver

http://onsemi.com

#### Overview

The LV8732V is a 2-channel H-bridge driver IC that can switch a stepper motor driver, which supports micro-step drive with 1/8-step resolution, and two channels of a brushed motor driver, which supports forward, reverse, brake, and standby of a motor. It is ideally suited for driving brushed DC motors and stepper motors used in office equipment and amusement applications.

#### **Function**

- Single-channel PWM current control stepper motor driver (selectable with DC motor driver channel 2) incorporated.

- BiCDMOS process IC

- Low on resistance (upper side :  $0.3\Omega$ ; lower side :  $0.25\Omega$ ; total of upper and lower :  $0.55\Omega$ ; Ta = 25°C, IO = 2A)

- Micro-step mode can be set to Full-step, Half-step, Quarter-step, or 1/8-step

- Excitation step proceeds only by step signal input

- Motor current selectable in four steps

- Output short-circuit protection circuit (selectable from latch-type or auto-reset-type) incorporated

- Unusual condition warning output pins

- No control power supply required

#### **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol              | Conditions                                                                                 | Ratings     | Unit |

|-----------------------------|---------------------|--------------------------------------------------------------------------------------------|-------------|------|

| Supply voltage              | VM max              | VM , VM1 , VM2                                                                             | 36          | V    |

| Output peak current         | I <sub>O</sub> peak | tw ≤ 10ms , duty 20% , Per 1ch                                                             | 2.5         | Α    |

| Output current              | I <sub>O</sub> max  | Per 1ch                                                                                    | 2           | Α    |

| Logic input voltage         | V <sub>IN</sub>     | ATT1 , ATT2 , EMM , RST/BLK , STEP/DC22<br>FR/DC21 , MD2/DC12 , MD1/DC11 , DM , OE ,<br>ST | -0.3 to +6  | V    |

| MONI/EMO input voltage      | Vmoni/Vemo          |                                                                                            | -0.3 to +6  | V    |

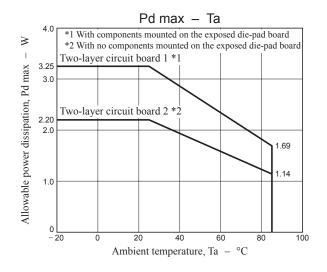

| Allowable power dissipation | Pd max              | *                                                                                          | 3.25        | W    |

| Operating temperature       | Topr                |                                                                                            | -20 to +85  | °C   |

| Storage temperature         | Tstg                |                                                                                            | -55 to +150 | °C   |

<sup>\*</sup> Specified circuit board : 90.0mm×90.0mm×1.6mm, glass epoxy 2-layer board, with backside mounting.

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Allowable Operating Ratings at Ta = 25°C

| Parameter                | Symbol          | Conditions                                                                             | Ratings  | Unit |

|--------------------------|-----------------|----------------------------------------------------------------------------------------|----------|------|

| Supply voltage range     | VM              | VM , VM1 , VM2                                                                         | 9 to 32  | V    |

| Logic input voltage      | V <sub>IN</sub> | ATT1 , ATT2 , EMM , RST/BLK , STEP/DC22 , FR/DC21 , MD2/DC12 , MD1/DC11 , DM , OE , ST | 0 to 5.5 | V    |

| VREF input voltage range | VREF            |                                                                                        | 0 to 3   | V    |

## **Electrical Characteristics** at Ta = 25°C, VM = 24V, VREF = 1.5V

| Paramet                      | ter                  | Symbol                | Conditions                                                                                                            |                                                   | Ratings |       | Unit |

|------------------------------|----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------|-------|------|

|                              |                      |                       |                                                                                                                       | min                                               | typ     | max   |      |

| Standby mode current drain   |                      | IMst                  | ST = "L" , I(VM)+I(VM1)+I(VM2)                                                                                        |                                                   | 100     | 400   | μА   |

| Current drain                |                      | IM                    | ST = "H", OE = "L", with no load ,                                                                                    |                                                   | 3.2     | 5     | mA   |

| VREG5 output voltage         | 10                   | Vreg5                 | $I(VM)+I(VM1)+I(VM2)$ $I_{O} = -1m\Delta$                                                                             | 4.5                                               | 5       | 5.5   | V    |

|                              |                      |                       | I <sub>O</sub> = -1mA                                                                                                 | +                                                 |         |       | °C   |

| Thermal shutdown to          | •                    | TSD                   | Design guarantee                                                                                                      | 150                                               | 180     | 200   |      |

| Thermal hysteresis w         | viatn                | ΔTSD                  | Design guarantee                                                                                                      |                                                   | 40      |       | °C   |

| Motor driver                 |                      | I p                   | L. OA Harrista and statement                                                                                          | 1                                                 | 0.0     | 0.4   |      |

| Output on resistance         |                      | Ronu                  | I <sub>O</sub> = 2A, Upper-side on resistance                                                                         |                                                   | 0.3     | 0.4   | Ω    |

| 0.1: 11: 1.:                 | -1                   | Rond                  | I <sub>O</sub> = 2A, Lower-side on resistance                                                                         |                                                   | 0.25    | 0.33  | Ω    |

| Output leakage curre         |                      | I <sub>O</sub> leak   |                                                                                                                       |                                                   |         | 50    | μA   |

| Diode forward voltag         |                      | VD                    | ID = -2A                                                                                                              |                                                   | 1.2     | 1.4   | V    |

| Logic pin input currer       | nt                   | I <sub>IN</sub> L     | ATT1 , ATT2 , EMM , RST/BLK ,<br>STEP/DC22 , FR/DC21 , MD2/DC12 ,<br>MD1/DC11 , DM , OE , ST , V <sub>IN</sub> = 0.8V | 4                                                 | 8       | 12    | μА   |

|                              |                      | I <sub>IN</sub> H     | V <sub>IN</sub> = 5V                                                                                                  | 30                                                | 50      | 70    | μА   |

| Logic input voltage          | High                 | V <sub>IN</sub> h     | ATT1, ATT2, EMM, RST/BLK,                                                                                             | 2.0                                               |         | 5.5   | V    |

|                              | Low                  | V <sub>IN</sub> I     | STEP/DC22 , FR/DC21 , MD2/DC12 ,<br>MD1/DC11 , DM , OE , ST                                                           | 0                                                 |         | 0.8   | V    |

| Current setting comparator   | 1/8 step resolution  | Vtdac0_2W             | Step 0 (When initialized : channel 1 comparator level)                                                                | 0.291                                             | 0.3     | 0.309 | V    |

| threshold voltage            |                      | Vtdac1_2W             | Step 1 (Initial state+1)                                                                                              | 0.285                                             | 0.294   | 0.303 | V    |

| (current step                |                      | Vtdac2_2W             | Step 2 (Initial state+2)                                                                                              | 0.267                                             | 0.276   | 0.285 | V    |

| switching)                   |                      | Vtdac3_2W             | Step 3 (Initial state+3)                                                                                              | 0.240                                             | 0.249   | 0.258 | V    |

|                              |                      | Vtdac4 2W             | Step 4 (Initial state+4)                                                                                              | 0.201                                             | 0.21    | 0.219 | V    |

|                              |                      | Vtdac5 2W             | Step 5 (Initial state+5)                                                                                              | 0.157                                             | 0.165   | 0.173 | V    |

|                              |                      | Vtdac6 2W             | Step 6 (Initial state+6)                                                                                              | 0.107                                             | 0.114   | 0.121 | V    |

|                              |                      | Vtdac7_2W             | Step 7 (Initial state+7)                                                                                              | 0.053                                             | 0.06    | 0.067 | V    |

|                              | Quarter step         | Vtdac0_W              | Step 0 (When initialized : channel 1                                                                                  | 0.291                                             | 0.3     | 0.309 | V    |

|                              | resolution           | Vtdac2_W              | comparator level)  Step 2 (Initial state+1)                                                                           | 0.267                                             | 0.276   | 0.285 | V    |

|                              |                      | Vtdac2_vv<br>Vtdac4_W | Step 4 (Initial state+2)                                                                                              | 0.201                                             | 0.21    | 0.219 |      |

|                              |                      | Vtdac4_VV<br>Vtdac6 W | Step 6 (Initial state+3)                                                                                              | 0.201                                             | 0.21    | 0.121 |      |

|                              | Half step            | Vtdac0_vv             | Step 0 (When initialized : channel 1                                                                                  | 0.107                                             | 0.114   | 0.309 |      |

|                              | resolution           | _                     | comparator level)                                                                                                     |                                                   |         |       |      |

|                              |                      | Vtdac4_H              | Step 4 (Initial state+1)                                                                                              | 0.201                                             | 0.21    | 0.219 | V    |

|                              | Full step resolution | Vtdac4_F              | Step 4' (When initialized : channel 1 comparator level)                                                               | 0.291                                             | 0.3     | 0.309 | V    |

| Current setting comp         | parator              | Vtatt00               | ATT1 = L, ATT2 = L                                                                                                    | 0.291                                             | 0.3     | 0.309 | V    |

| threshold voltage            |                      | Vtatt01               | ATT1 = H, ATT2 = L                                                                                                    | 0.232                                             | 0.24    | 0.248 | V    |

| (current attenuation r       | rate switching)      | Vtatt10               | ATT1 = L, ATT2 = H                                                                                                    | 0.143                                             | 0.15    | 0.157 | V    |

|                              |                      | Vtatt11               | ATT1 = H, ATT2 = H                                                                                                    | 0.053                                             | 0.06    | 0.067 | V    |

| Chopping frequency           |                      | Fchop                 | Cchop = 200pF                                                                                                         | 40                                                | 50      | 60    | kHz  |

| CHOP pin charge/dis          | scharge current      | Ichop                 |                                                                                                                       | 7                                                 | 10      | 13    | μΑ   |

| Chopping oscillation circuit |                      | Vtup                  |                                                                                                                       | 0.8                                               | 1       | 1.2   | V    |

| threshold voltage            |                      | Vtdown                |                                                                                                                       | 0.4                                               | 0.5     | 0.6   |      |

| VREF pin input current       |                      | Iref                  | VREF = 1.5V                                                                                                           | -0.5                                              |         |       | μА   |

| MONI pin saturation          | voltage              | Vsatmon               | Imoni = 1mA                                                                                                           |                                                   |         | 400   | mV   |

| Charge pump                  |                      | 1                     | T                                                                                                                     | <del>, , , , , , , , , , , , , , , , , , , </del> | П       | 1     |      |

| VG output voltage            |                      | VG                    |                                                                                                                       | 28                                                | 28.7    | 29.8  | V    |

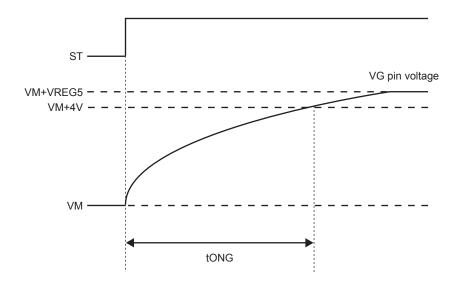

| Rise time                    |                      | tONG                  | $VG = 0.1 \mu F$ , Between CP1-CP2 0.1u F ,<br>ST="H" $\rightarrow$ VG=VM+4V                                          |                                                   | 200     | 500   | μS   |

| Oscillator frequency         |                      | Fosc                  |                                                                                                                       | 90                                                | 125     | 150   | kHz  |

Continued on next page.

Continued from preceding page.

| Description                     | O. made al | Out III    | Ratings |     |     | 11.2 |

|---------------------------------|------------|------------|---------|-----|-----|------|

| Parameter                       | Symbol     | Conditions | min     | typ | max | Unit |

| Output short-circuit protection |            |            |         |     |     |      |

| EMO pin saturation voltage      | Vsatemo    | Iemo = 1mA |         |     | 400 | mV   |

| CEM pin charge current          | Icem       | Vcem = 0V  |         | 10  | 13  | μА   |

| CEM pin threshold voltage       | Vtcem      |            | 0.8     | 1   | 1.2 | V    |

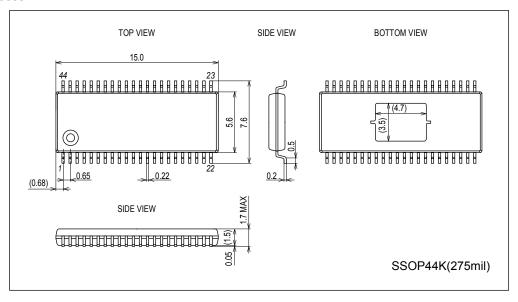

## **Package Dimensions**

unit: mm (typ)

3333A

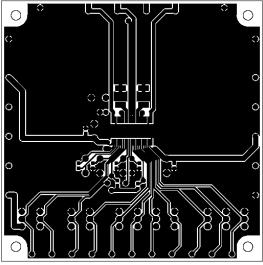

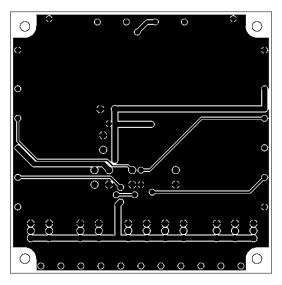

#### Substrate Specifications (Substrate recommended for operation of LV8732V)

Size :  $90\text{mm} \times 90\text{mm} \times 1.6\text{mm}$  (two-layer substrate [2S0P])

Material : Glass epoxy

Copper wiring density : L1 = 85% / L2 = 90%

L2: Copper wiring pattern diagram

#### **Cautions**

- 1) The data for the case with the Exposed Die-Pad substrate mounted shows the values when 90% or more of the Exposed Die-Pad is wet.

- 2) For the set design, employ the derating design with sufficient margin.

Stresses to be derated include the voltage, current, junction temperature, power loss, and mechanical stresses such as vibration, impact, and tension.

Accordingly, the design must ensure these stresses to be as low or small as possible.

The guideline for ordinary derating is shown below:

- (1)Maximum value 80% or less for the voltage rating

- (2)Maximum value 80% or less for the current rating

- (3)Maximum value 80% or less for the temperature rating

- 3) After the set design, be sure to verify the design with the actual product.

Confirm the solder joint state and verify also the reliability of solder joint for the Exposed Die-Pad, etc. Any void or deterioration, if observed in the solder joint of these parts, causes deteriorated thermal conduction, possibly resulting in thermal destruction of IC.

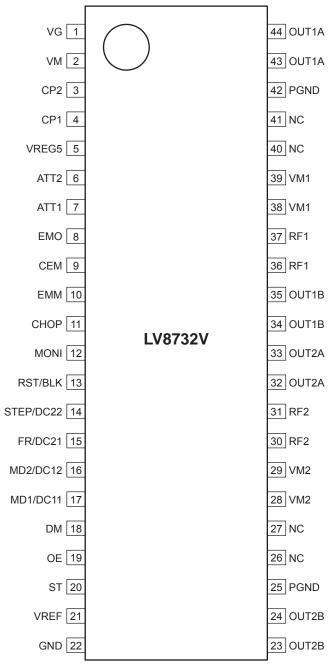

## **Pin Assignment**

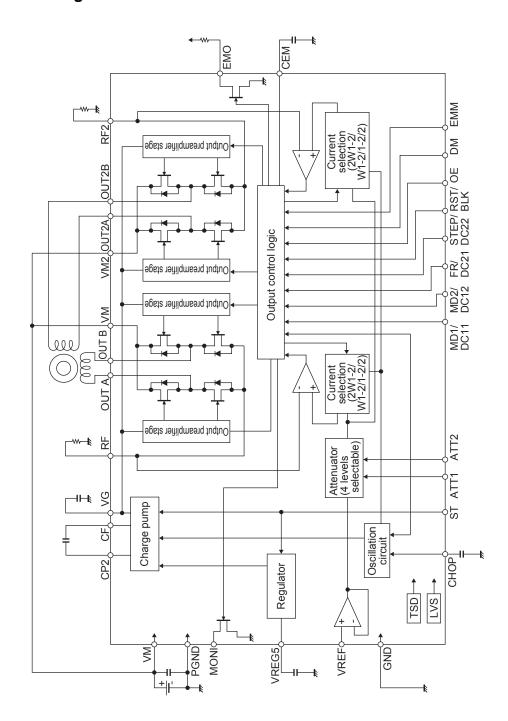

## **Block Diagram**

## **Pin Functions**

| PINFU   | inctions  |                                         |                             |

|---------|-----------|-----------------------------------------|-----------------------------|

| Pin No. | Pin Name  | Pin Function                            | Equivalent Circuit          |

| 6       | ATT2      | Motor holding current switching pin.    |                             |

| 7       | ATT1      | Motor holding current switching pin.    |                             |

| 10      | EMM       | Output short-circuit protection mode    |                             |

|         |           | switching pin.                          | VREG5 O                     |

| 13      | RST/BLK   | RESET input pin (STM) / Blanking time   |                             |

|         |           | switching pin (DCM).                    | <b>★</b>                    |

| 14      | STEP/DC22 | STEP signal input pin (STM) / Channel 2 |                             |

|         | 0.2.72022 | output control input pin 2 (DCM).       | <b>★</b> ••—                |

| 15      | FR/DC21   | CW / CCW signal input pin (STM) /       | 10k0                        |

|         | 1102021   | Channel 2 output control input pin 1    | 10kΩ L                      |

|         |           | (DCM).                                  |                             |

| 16      | MD2/DC12  | Excitation mode switching pin 2 (STM) / |                             |

| 10      | MD2/DC12  | Channel 1 output control input pin 2    | <b>★</b> \$100kΩ            |

|         |           |                                         |                             |

| 17      | MD1/DC11  | (DCM).                                  |                             |

| 17      | MD1/DC11  | Excitation mode switching pin 1 (STM) / |                             |

|         |           | Channel 1 output control input pin 1    | GND O                       |

| 1 40    | DM        | (DCM).                                  |                             |

| 18      | DM        | Drive mode (STM/DCM) switching pin.     |                             |

| 19      | OE        | Output enable signal input pin.         |                             |

| 20      | ST        | Chip enable pin.                        | VREG5 ○                     |

|         |           |                                         |                             |

|         |           |                                         | <b>*</b>                    |

|         |           |                                         | ▼                           |

|         |           |                                         |                             |

|         |           |                                         |                             |

|         |           |                                         |                             |

|         |           |                                         |                             |

|         |           |                                         | 10kΩ<br>                    |

|         |           |                                         | <b>↓</b>                    |

|         |           |                                         | <b>†</b> [                  |

|         |           |                                         | \$80kΩ                      |

|         |           |                                         |                             |

|         |           |                                         | GND O-                      |

| 23, 24  | OUT2B     | Channel 2 OLITP output pin              |                             |

| 25, 42  | PGND      | Channel 2 OUTB output pin.              | 38(39)                      |

|         |           | Power system ground.                    | (28)(29)                    |

| 28, 29  | VM2       | Channel 2 motor power supply            |                             |

| 00.04   | DE0       | connection pin.                         |                             |

| 30, 31  | RF2       | Channel 2 current-sense resistor        |                             |

|         |           | connection pin.                         |                             |

| 32, 33  | OUT2A     | Channel 2 OUTA output pin.              |                             |

| 34, 35  | OUT1B     | Channel 1 OUTB output pin.              | 43(44) 7 34(35)             |

| 36, 37  | RF1       | Channel 1 current-sense resistor        | 32333 + 63324               |

|         |           | connection pin.                         |                             |

| 38, 39  | VM1       | Channel 1 motor power supply pin.       | ▎                           |

| 43, 44  | OUT1A     | Channel 1 OUTA output pin.              |                             |

|         |           |                                         | 10kΩ 500Ω                   |

|         |           |                                         |                             |

|         |           |                                         | 25(42) → 500Ω <sub>II</sub> |

|         |           |                                         |                             |

|         |           |                                         | 30(31)                      |

|         |           |                                         | (30)(31)                    |

|         |           |                                         | GND O +                     |

|         |           |                                         |                             |

Continued on next page.

Continued from preceding page. Pin No. Pin Name Pin Function Equivalent Circuit 1 ۷G Charge pump capacitor connection pin. (3) (4) (1) 2 VM Motor power supply connection pin. VREG5 O-3 CP2 Charge pump capacitor connection pin. Charge pump capacitor connection pin. 4 CP1 GND C 21 VREF Constant current control reference VREG5 Ovoltage input pin.  $500\Omega$ GND ○ 5 VREG5 Internal power supply capacitor VM Oconnection pin. **≷**78kΩ ≶26kΩ GND O-8 EMO Output short-circuit state warning output VREG5 ○ 12 MONI Position detection monitor pin. GND O-

Continued on next page.

|         | from preceding |                                                                                 |                         |

|---------|----------------|---------------------------------------------------------------------------------|-------------------------|

| Pin No. | Pin Name       | Pin Function                                                                    | Equivalent Circuit      |

| 9       | CEM            | Pin to connect the output short-circuit state detection time setting capacitor. | VREG5 0                 |

|         |                |                                                                                 | GND O                   |

| 11      | СНОР           | Chopping frequency setting capacitor connection pin.                            | VREG5 0  500Ω \$ \$500Ω |

| 22      | GND            | Ground.                                                                         |                         |

| 26, 27  | NC             | No Connection                                                                   |                         |

| 40, 41  |                | (No internal connection to the IC)                                              |                         |

#### **Description of operation**

#### 1.Input Pin Function

#### 1-1) Chip enable function

This IC is switched between standby and operating mode by setting the ST pin. In standby mode, the IC is set to power-save mode and all logic is reset. In addition, the internal regulator circuit and charge pump circuit do not operate in standby mode.

| ST          | Mode           | Internal regulator | Charge pump |

|-------------|----------------|--------------------|-------------|

| Low or Open | Standby mode   | Standby            | Standby     |

| High        | Operating mode | Operating          | Operating   |

#### 1-2) Drive mode switching pin function

The IC drive mode is switched by setting the DM pin. In STM mode, stepper motor channel 1 can be controlled by the CLK-IN input. In DCM mode, DC motor channel 2 or stepper motor channel 1 can be controlled by parallel input. Stepper motor control using parallel input is Full-step or Half-step full torque.

| DM          | Drive mode | Application                                              |

|-------------|------------|----------------------------------------------------------|

| Low or Open | STM mode   | Stepper motor channel 1 (CLK-IN)                         |

| High        | DCM mode   | DC motor channel 2 or stepper motor channel 1 (parallel) |

#### 2.STM mode (DM = Low or Open)

#### 2-1) STEP pin function

| Input |          | Operating mode           |

|-------|----------|--------------------------|

| ST    | STP      | 5 p. 2 m. 19 m. 000      |

| Low   | *        | Standby mode             |

| High  |          | Excitation step proceeds |

| High  | <b>—</b> | Excitation step is kept  |

#### 2-2) Excitation mode setting function

| MD1  | MD2  | Micro-step resolution                   | Initial position |           |  |

|------|------|-----------------------------------------|------------------|-----------|--|

|      |      | (Excitation mode)                       | Channel 1        | Channel 2 |  |

| Low  | Low  | Full step(2 phase excitation)           | 100%             | -100%     |  |

| High | Low  | Half step(1-2 phase excitation)         | 100%             | 0%        |  |

| Low  | High | Quarter step<br>(W1-2 phase excitation) | 100%             | 0%        |  |

| High | High | 1/8 step(2W1-2 phase excitation)        | 100%             | 0%        |  |

This is the initial position of each excitation mode in the initial state after power-on and when the counter is reset.

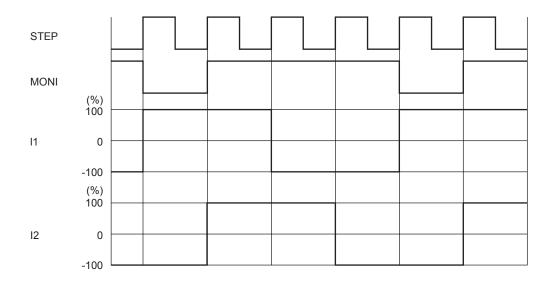

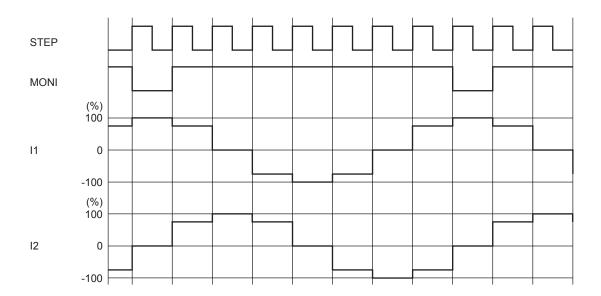

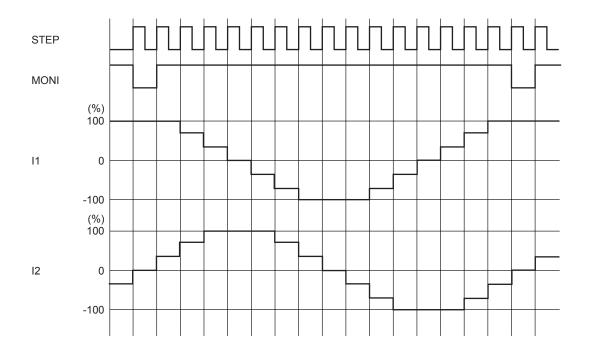

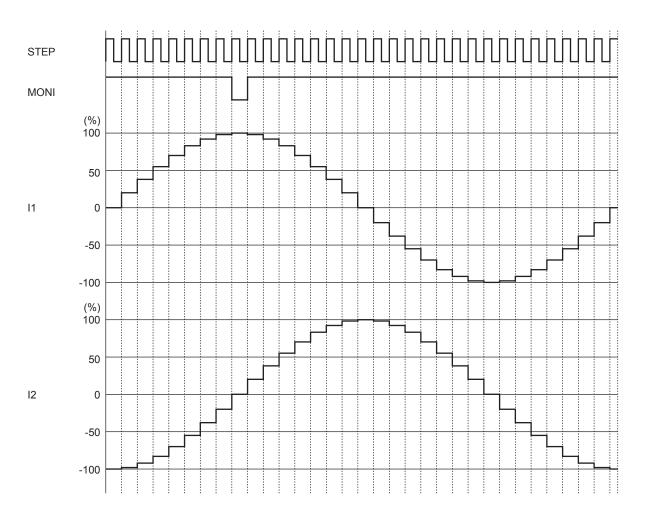

#### 2-3) Position detection monitoring function

The MONI position detection monitoring pin is of an open drain type.

When the excitation position is in the initial position, the MONI output is placed in the ON state.

(Refer to "2-12.Examples of current waveforms in each micro-step mode .")

#### 2-4) Setting constant-current control reference current

This IC is designed to automatically exercise PWM constant-current chopping control for the motor current by setting the output current. Based on the voltage input to the VREF pin and the resistance connected between RF and GND, the output current that is subject to the constant-current control is set using the calculation formula below:

$$I_{OUT} = (VREF/5)/RF$$

resistance

The voltage input to the VREF pin can be switched to four-step settings depending on the statuses of the two inputs, ATT1 and ATT2. This is effective for reducing power consumption when motor holding current is supplied.

Attenuation function for VREF input voltage

| ATT1 | ATT2 | Current setting reference voltage attenuation ratio |

|------|------|-----------------------------------------------------|

| Low  | Low  | 100%                                                |

| High | Low  | 80%                                                 |

| Low  | High | 50%                                                 |

| High | High | 20%                                                 |

The formula used to calculate the output current when using the function for attenuating the VREF input voltage is given below.

$$I_{OUT} = (VREF/5) \times (attenuation ratio)/RF resistance$$

Example : At VREF of 1.5V, a reference voltage setting of 100% [(ATT1, ATT2) = (L, L)] and an RF resistance of  $0.3\Omega$ , the output current is set as shown below.

$$I_{OUT} = 1.5V/5 \times 100\%/0.3\Omega = 1.0A$$

If, in this state, (ATT1, ATT2) is set to (H, H), IOUT will be as follows :

$$I_{OUT} = 1.0A \times 20\% = 200mA$$

In this way, the output current is attenuated when the motor holding current is supplied so that power can be conserved.

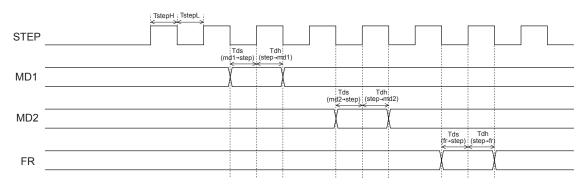

#### 2-5) Input Timing

TstepH/TstepL : Clock H/L pulse width (min 500ns)

Tds: Data set-up time (min 500ns)

Tdh: Data hold time (min 500ns)

#### 2-6) Blanking period

If, when exercising PWM constant-current chopping control over the motor current, the mode is switched from decay to charge, the recovery current of the parasitic diode may flow to the current sensing resistance, causing noise to be carried on the current sensing resistance pin, and this may result in erroneous detection. To prevent this erroneous detection, a blanking period is provided to prevent the noise occurring during mode switching from being received. During this period, the mode is not switched from charge to decay even if noise is carried on the current sensing resistance pin.

In the stepper motor driver mode (DM = Low or Open) of this IC, the blanking time is fixed at approximately  $1\mu$ s. In the DC motor driver mode (DM = High), the blanking time can be switched to one of two levels using the RST/BLK pin. (Refer to "Blanking time switching function.")

<sup>\*</sup> The above setting is the output current at 100% of each excitation mode.

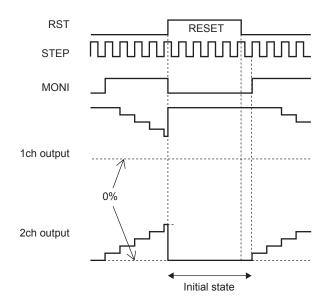

2-7) Reset function

| RST  | Operating mode   |

|------|------------------|

| Low  | Normal operation |

| High | Reset state      |

When the RST pin is set to High, the excitation position of the output is forcibly set to the initial state, and the MONI output is placed in the ON state. When RST is then set to Low, the excitation position is advanced by the next STEP input.

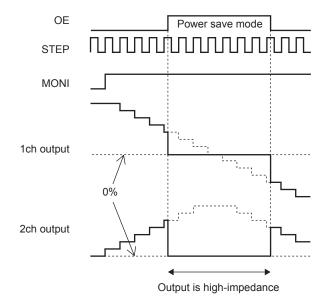

2-8) Output enable function

| OE   | Operating mode |  |  |

|------|----------------|--|--|

| Low  | Output ON      |  |  |

| High | Output OFF     |  |  |

When the OE pin is set High, the output is forced OFF and goes to high impedance.

However, the internal logic circuits are operating, so the excitation position proceeds when the STEP signal is input. Therefore, when OE is returned to Low, the output level conforms to the excitation position proceeded by the STEP input.

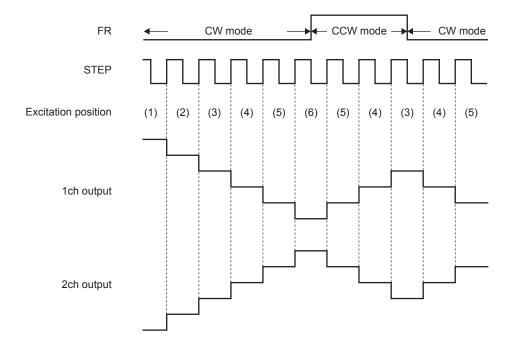

2-9) Forward/reverse switching function

| FR   | Operating mode          |  |  |  |

|------|-------------------------|--|--|--|

| Low  | Clockwise (CW)          |  |  |  |

| High | Counter-clockwise (CCW) |  |  |  |

The internal D/A converter proceeds by one bit at the rising edge of the input STEP pulse.

In addition, CW and CCW mode are switched by setting the FR pin.

In CW mode, the channel 2 current phase is delayed by 90° relative to the channel 1 current.

In CCW mode, the channel 2 current phase is advanced by 90° relative to the channel 1 current.

#### 2-10) Chopping frequency setting

For constant-current control, this IC performs chopping operations at the frequency determined by the capacitor (Cchop) connected between the CHOP pin and GND.

The chopping frequency is set as shown below by the capacitor (Cchop) connected between the CHOP pin and GND.

Fchop = Ichop/ (Cchop

$$\times$$

Vtchop  $\times$  2) (Hz)

Ichop : Capacitor charge/discharge current, typ  $10\mu A$

Vtchop: Charge/discharge hysteresis voltage (Vtup-Vtdown), typ 0.5V

For instance, when Cchop is 200pF, the chopping frequency will be as follows:

Fchop =

$$10\mu A/(200pF \times 0.5V \times 2) = 50kHz$$

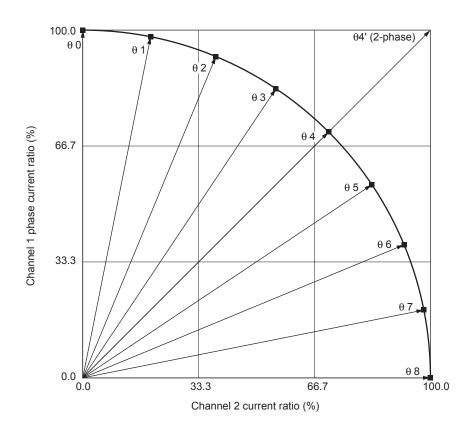

## 2-11) Output current vector locus (one step is normalized to 90 degrees)

## Setting current ration in each micro-step mode

| STEP | 1/8 ste   | ep (%)    | Quarter step (%) |           | Half step (%) |           | Full step (%) |           |

|------|-----------|-----------|------------------|-----------|---------------|-----------|---------------|-----------|

|      | Channel 1 | Channel 2 | Channel 1        | Channel 2 | Channel 1     | Channel 2 | Channel 1     | Channel 2 |

| θ0   | 100       | 0         | 100              | 0         | 100           | 0         |               |           |

| θ1   | 98        | 20        |                  |           |               |           |               |           |

| θ2   | 92        | 38        | 92               | 38        |               |           |               |           |

| θ3   | 83        | 55        |                  |           |               |           |               |           |

| θ4   | 70        | 70        | 70               | 70        | 70            | 70        | 100           | 100       |

| θ5   | 55        | 83        |                  |           |               |           |               |           |

| θ6   | 38        | 92        | 38               | 92        |               |           |               |           |

| θ7   | 20        | 98        |                  |           |               |           |               |           |

| θ8   | 0         | 100       | 0                | 100       | 0             | 100       |               |           |

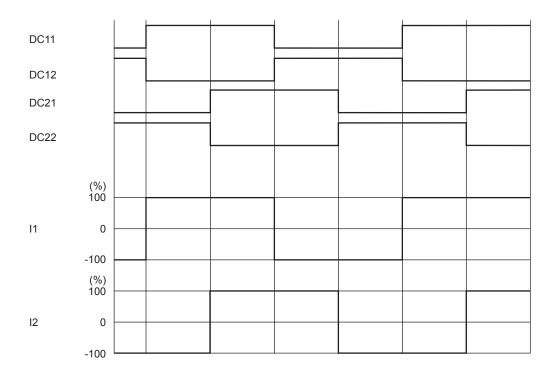

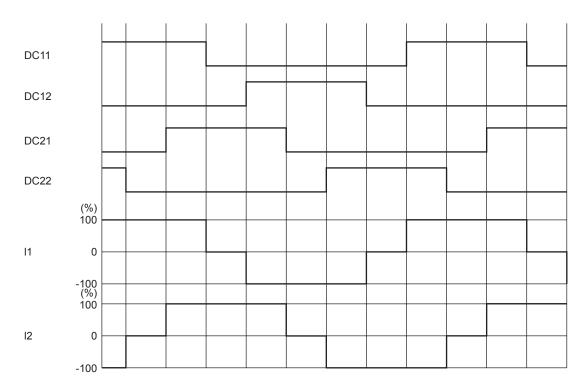

# 2-12) Examples of current waveform in each micro-step mode Full step (CW mode)

## Half step (CW mode)

Quarter step (CW mode)

1/8 step (CW mode)

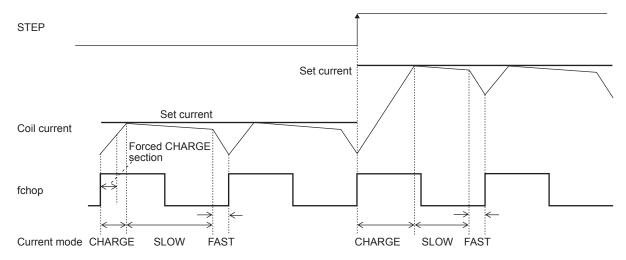

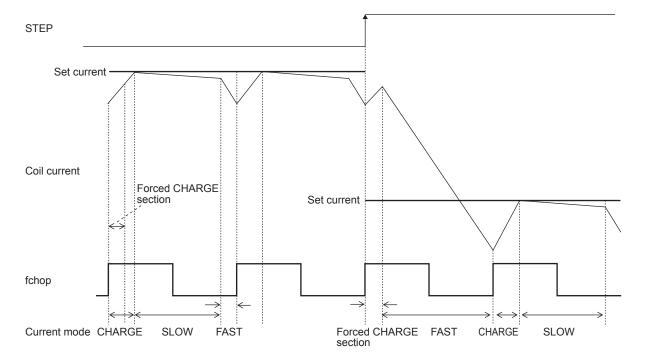

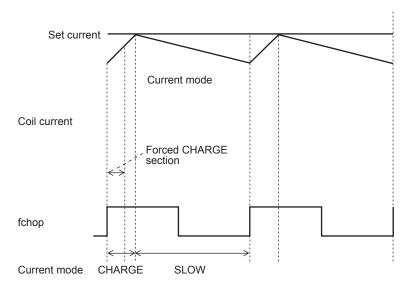

#### 2-13) Current control operation specification

(Sine wave increasing direction)

(Sine wave decreasing direction)

In each current mode, the operation sequence is as described below:

- At rise of chopping frequency, the CHARGE mode begins. (In the time defined as the "blanking time," the CHARGE mode is forced regardless of the magnitude of the coil current (ICOIL) and set current (IREF).)

- The coil current (ICOIL) and set current (IREF) are compared in this blanking time.

When (ICOIL < IREF) state exists;

The CHARGE mode up to ICOIL  $\geq$  IREF, then followed by changeover to the SLOW DECAY mode, and finally by the FAST DECAY mode for approximately 1 $\mu$ s.

When (ICOIL < IREF) state does not exist;

The FAST DECAY mode begins. The coil current is attenuated in the FAST DECAY mode till one cycle of chopping is over.

Above operations are repeated. Normally, the SLOW (+FAST) DECAY mode continues in the sine wave increasing direction, then entering the FAST DECAY mode till the current is attenuated to the set level and followed by the SLOW DECAY mode.

#### 3. DCM Mode (DM-High)

## 3-1) DCM mode output control logic

| Paralle   | el input  | Output     |            | Mode          |

|-----------|-----------|------------|------------|---------------|

| DC11 (21) | DC12 (22) | OUT1 (2) A | OUT1 (2) B |               |

| Low       | Low       | OFF        | OFF        | Standby       |

| High      | Low       | High       | Low        | CW (Forward)  |

| Low       | High      | Low        | High       | CCW (Reverse) |

| High      | High      | Low        | Low        | Brake         |

## 3-2) Blanking time switching function

| BLK  | Blanking time |  |  |

|------|---------------|--|--|

| Low  | 2μs           |  |  |

| High | 3μs           |  |  |

#### 3-3) Output enable function

| OE   | Operating mode |  |  |

|------|----------------|--|--|

| Low  | Output ON      |  |  |

| High | Output OFF     |  |  |

When the OE pin is set High, the output is forced OFF and goes to high impedance. When the OE pin is set Low, output conforms to the control logic.

#### 3-4) Current limit reference voltage setting function

By setting a current limit, this IC automatically exercises short braking control to ensure that when the motor current has reached this limit, the current will not exceed it.

(Current limit control time chart)

The limit current is set as calculated on the basis of the voltage input to the VREF pin and the resistance between the RF pin and GND using the formula given below.

Ilimit =

$$(VREF/5)/RF$$

resistance

The voltage applied to the VREF pin can be switched to any of the four setting levels depending on the statuses of the two inputs, ATT1 and ATT2.

Function for attenuating VREF input voltage

| ATT1 | ATT2 | Current setting reference voltage attenuation ratio |

|------|------|-----------------------------------------------------|

| Low  | Low  | 100%                                                |

| High | Low  | 80%                                                 |

| Low  | High | 50%                                                 |

| High | High | 20%                                                 |

The formula used to calculate the output current when using the function for attenuating the VREF input voltage is given below.

Ilimit =  $(VREF/5) \times (attenuation ratio) / RF resistance$

Example : At VREF of 1.5V, a reference voltage setting of 100% [(ATT1, ATT2) = (L, L)] and an RF resistance of  $0.3\Omega$ , the output current is set as shown below.

Ilimit =

$$1.5V/5 \times 100\%/0.3\Omega = 1.0A$$

If, in this state, (ATT1, ATT2) has been set to (H, H), Ilimit will be as follows :

Ilimit =

$$1.0A \times 20\% = 200mA$$

3-5) Examples of current waveform in each micro-step mode when stepper motor parallel input control Full step (CW mode)

Half step full torque (CW mode)

#### 4. Output short-circuit protection function

This IC incorporates an output short-circuit protection circuit that, when the output has been shorted by an event such as shorting to power or shorting to ground, sets the output to the standby mode and turns on the warning output in order to prevent the IC from being damaged. In the stepping motor driver (STM) mode (DM = Low), this function sets the output to the standby mode for both channels by detecting the short-circuiting in one of the channels. In the DC motor driver mode (DM = High), channels 1 and 2 operate independently. (Even if the output of channel 1 has been short-circuited, channel 2 will operate normally.)

#### 4-1) Output short-circuit protection mode switching function

Output short-circuit protection mode of IC can be switched by the setting of EMM pin .

| EMM         | State             |  |

|-------------|-------------------|--|

| Low or Open | Latch method      |  |

| High        | Auto reset method |  |

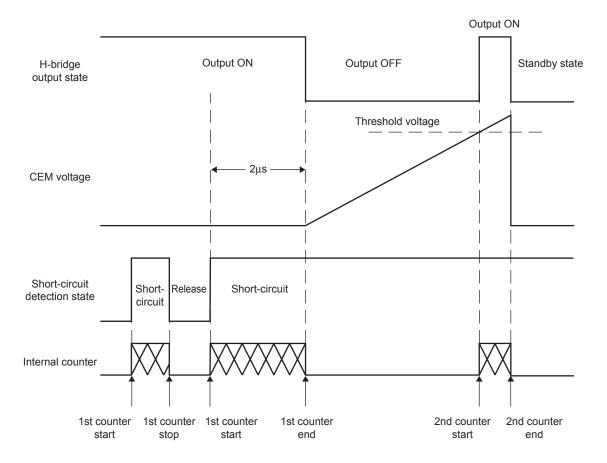

#### 4-2) Latch type

In the latch mode, when the output current exceeds the detection current level, the output is turned OFF, and this state is held.

The detection of the output short-circuited state by the IC causes the output short-circuit protection circuit to be activated.

When the short-circuited state continues for the period of time set using the internal timer (approximately  $2\mu s$ ), the output in which the short-circuiting has been detected is first set to OFF. After this, the output is set to ON again as soon as the timer latch time (Tcem) described later has been exceeded, and if the short-circuited state is still detected, all the outputs of the channel concerned are switched to the standby mode, and this state is held. This state is released by setting ST to low.

#### 4-3) Auto reset type

In the automatic reset mode, when the output current exceeds the detection current level, the output waveform changes to the switching waveform.

As with the latch system, when the output short-circuited state is detected, the short-circuit protection circuit is activated. When the operation of the short-circuit detection circuit exceeds the timer latch time (Tcem) described later, the output is changed over to the standby mode and is reset to the ON mode again in 2ms (typ). In this event, if the over current mode still continues, the switching mode described above is repeated until the over current mode is canceled.

#### 4-4) Unusual condition warning output pins (EMO, MONI)

The LV8731V is provided with the EMO pin which notifies the CPU of an unusual condition if the protection circuit operates by detecting an unusual condition of the IC. This pin is of the open-drain output type and when an unusual condition is detected, the EMO output is placed in the ON (EMO = Low) state.

In the DC motor driver mode (DM = High), the MONI pin also functions as a warning output pin.

The functions of the EMO pin and MONI pin change as shown below depending on the state of the DM pin.

When the DM is low (STM mode):

EMO: Unusual condition warning output pin

MONI: Excitation initial position detection monitoring

When the DM is high (DCM) mode):

EMO : Channel 1 warning output pin MONI : Channel 2 warning output pin

Furthermore, the EMO (MONI) pin is placed in the ON state when one of the following conditions occurs.

- 1. Shorting-to-power, shorting-to-ground, or shorting-to-load occurs at the output pin and the output short-circuit protection circuit is activated.

- 2. The IC junction temperature rises and the thermal protection circuit is activated.

| Unusual condition                | DM = L (STM mode) |      | DM = H (DCM mode) |      |

|----------------------------------|-------------------|------|-------------------|------|

|                                  | EMO               | MONI | EMO               | MONI |

| Channel 1 short-circuit detected | ON                | -    | ON                | -    |

| Channel 2 short-circuit detected | ON                | -    | -                 | ON   |

| Overheating condition detected   | ON                | -    | ON                | ON   |

#### 4-5) Timer latch time (Tcem)

The time taken for the output to be set to OFF when the output has been short-circuited can be set using capacitor Ccem, connected between the CEM pin and GND. The value of capacitor Ccem is determined by the formula given below.

Timer latch : Tcem  $\sim$  Ccem  $\times$  Vtcem/Icem [sec]

Vtcem : Comparator threshold voltage, typ 1V Icem : CEM pin charge current, typ 10μA

#### 5. Thermal shutdown function

The thermal shutdown circuit is included, and the output is turned off when junction temperature Tj exceeds 180°C and the abnormal state warning output is turned on at the same time.

When the temperature falls hysteresis level, output is driven again (automatic restoration)

The thermal shutdown circuit doesn't guarantee protection of the set and the destruction prevention of IC, because it works at the temperature that is higher than rating (Tjmax=150°C) of the junction temperature

$TSD = 180^{\circ}C \text{ (typ)}$

$\Delta$ TSD = 40°C (typ)

#### 6. Charge Pump Circuit

When the ST pin is set High, the charge pump circuit operates and the VG pin voltage is boosted from the VM voltage to the VM + VREG5 voltage.

If the VG pin voltage is not boosted to VM+4V or more, the output pin cannot be turned on. Therefore it is recommended that the drive of motor is started after the time has passed tONG or more.

VG Pin Voltage Schematic View

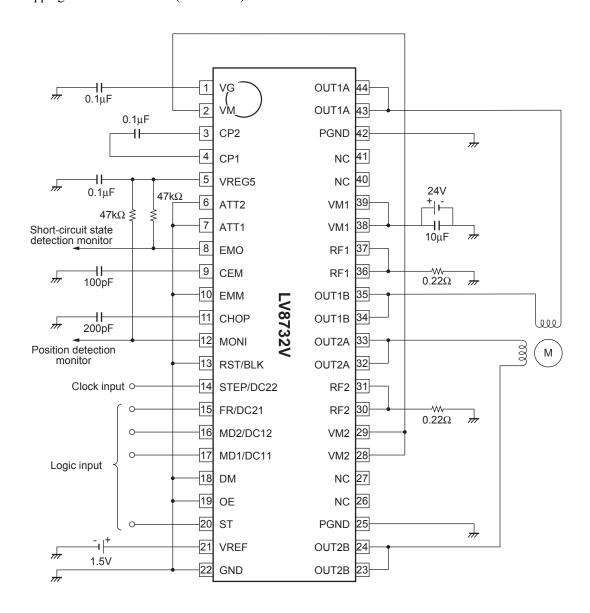

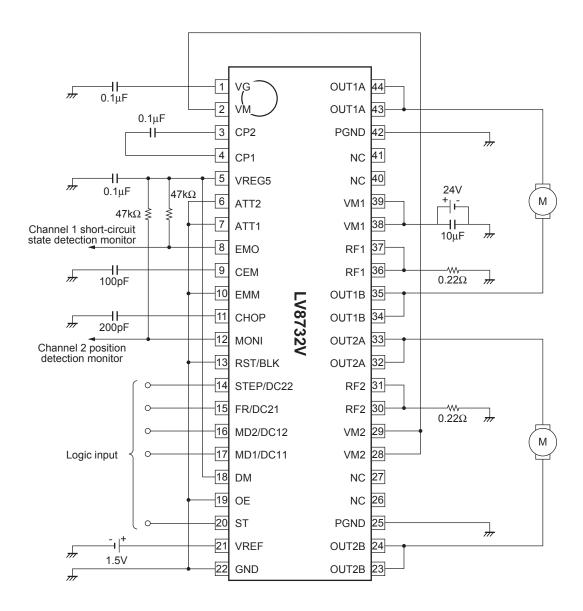

## **Application Circuit Example**

• Stepping motor driver circuit (DM = Low)

The formulae for setting the constants in the examples of the application circuits above are as follows: Constant current (100%) setting

When

$$VREF = 1.5V$$

$$I_{OUT} = VREF/5/RF$$

resistance

= 1.5V/5/0.22 $\Omega$  = 1.36A

Chopping frequency setting

Fchop = Ichop/ (Cchop × Vtchop × 2)

=

$$10\mu$$

A/ (200pF × 0.5V × 2) =  $50k$ Hz

Timer latch time when the output is short-circuited

$$Tcem = Ccem \times Vtcem/Icem$$

$$= 100pF \times 1V/10\mu A = 10\mu s$$

• DC motor driver circuit (DM = High, and the current limit function is in use.)

The formulae for setting the constants in the examples of the application circuits above are as follows: Constant current limit (100%) setting

When

$$VREF = 1.5V$$

$$= 1.5V/5/0.22\Omega = 1.36A$$

Chopping frequency setting

Fchop = Ichop/ (Cchop

$$\times$$

Vtchop  $\times$  2)

$$= 10 \mu A/(200 pF \times 0.5 V \times 2) = 50 kHz$$

Timer latch time when the output is short-circuited

$$Tcem = Ccem \times Vtcem/Icem$$

$$= 100 pF \times 1V/10 \mu A = 10 \mu s$$

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa