# Full-Bridge PWM Gate Driver

#### FEATURES AND BENEFITS

- PHASE/ENABLE/SLEEPn control logic

- Overcurrent indication

- · Adjustable off-time and blank-time

- · Adjustable current limit

- Adjustable gate drive

- · Synchronous rectification

- Internal UVLO

- · Crossover-current protection

- · MOSFET VDS protection

- Voltage output proportional to load current

# PACKAGE:

20-Pin QFN (suffix "ES") with Exposed Thermal Pad

Not to scale

# **DESCRIPTION**

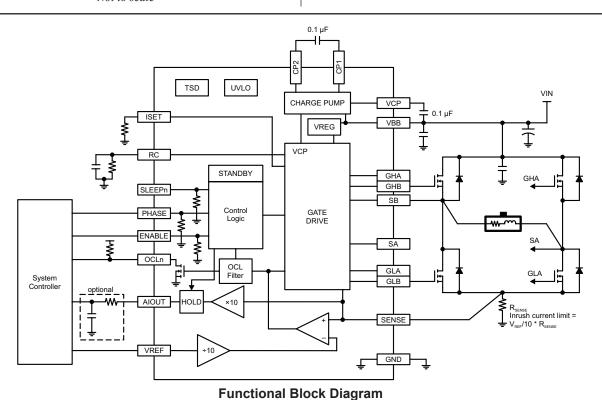

Designed for pulse-width-modulated (PWM) control of DC motors, the A5957 is capable of 50 V operation and provides gate drive for an all n-channel external MOSFET bridge.

Input terminals are provided for use in controlling the speed and direction of a DC motor with externally applied PWM control signals. Internal synchronous rectification control circuitry is provided to lower power dissipation during PWM operation.

Internal circuit protection includes VDS protection, thermal shutdown with hysteresis, undervoltage monitoring of VBB, and crossover-current protection.

The A5957 is supplied in a low-profile, 4×4 mm, 20-contact QFN package (suffix "ES") with exposed thermal pad.

# **SPECIFICATIONS**

# **Selection Guide**

| Part Number  | Ambient Temp Range | Packing                    | Notes |

|--------------|--------------------|----------------------------|-------|

| A5957GESTR-T | -40°C to 105°C     | 1500 pieces per 7-in. reel |       |

#### **Absolute Maximum Ratings**

| Characteristic Symbol       |                    | Notes                   | Rating      | Unit |

|-----------------------------|--------------------|-------------------------|-------------|------|

| Load Supply Voltage         | V <sub>BB</sub>    |                         | 50          | V    |

| Motor Outputs               | Sx                 | Sx – SENSE; VBB – Sx    | -2 to 52    | V    |

| CENICE                      |                    |                         | -0.5 to 0.5 | V    |

| SENSE                       | V <sub>SENSE</sub> | T <sub>W</sub> < 500 ns | -4 to 4     | V    |

| OCLn                        | V <sub>OCLn</sub>  |                         | -0.3 to 5.5 | V    |

| VREF                        | V <sub>REF</sub>   |                         | -0.3 to 5.5 | V    |

| ISET                        | V <sub>ISET</sub>  |                         | -0.3 to 5.5 | V    |

| AIOUT                       | V <sub>AIOUT</sub> |                         | -0.3 to 5.5 | V    |

| Logic Input Voltage Range   | V <sub>IN</sub>    | PHASE, ENABLE, MODE     | -0.3 to 5.5 | V    |

| Junction Temperature        | T <sub>J</sub>     |                         | 150         | °C   |

| Storage Temperature Range   | T <sub>S</sub>     |                         | –55 to 150  | °C   |

| Operating Temperature Range | T <sub>A</sub>     | Range G                 | -40 to 105  | °C   |

# **Thermal Characteristics**

(may require derating at maximum conditions; see application information)

| Characteristic | Symbol          | Test Conditions*                  | Value | Unit |

|----------------|-----------------|-----------------------------------|-------|------|

| ES Package     | $R_{\theta JA}$ | 4-Layer PCB, 1 in <sup>2</sup> Cu | 37    | °C/W |

<sup>\*</sup>Power dissipation and thermal limits must be observed.

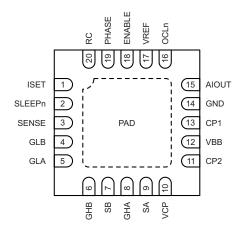

Package ES, 20-Pin QFN Pin-Outs

# **Terminal List Table**

| Terminal List Table |        |                                                  |  |  |  |

|---------------------|--------|--------------------------------------------------|--|--|--|

| Name                | Number | Function                                         |  |  |  |

| ISET                | 1      | Terminal to set gate drive current               |  |  |  |

| SLEEPn              | 2      | Sleep input, active low                          |  |  |  |

| SENSE               | 3      | Sense resistor connection, low-side gate return  |  |  |  |

| GLB                 | 4      | Gate driver                                      |  |  |  |

| GLA                 | 5      | Gate driver                                      |  |  |  |

| GHB                 | 6      | Gate driver                                      |  |  |  |

| SB                  | 7      | High-side bridge reference                       |  |  |  |

| GHA                 | 8      | Gate driver                                      |  |  |  |

| SA                  | 9      | High-side bridge reference                       |  |  |  |

| VCP                 | 10     | Charge pump reservoir cap connection             |  |  |  |

| CP2                 | 11     | Charge pump terminal                             |  |  |  |

| VBB                 | 12     | Supply voltage                                   |  |  |  |

| CP1                 | 13     | Charge pump terminal                             |  |  |  |

| GND                 | 14     | Ground                                           |  |  |  |

| AIOUT               | 15     | Analog output proportional to V <sub>SENSE</sub> |  |  |  |

| OCLn                | 16     | OCP and OVP output flag, open drain              |  |  |  |

| VREF                | 17     | Analog OCP reference input                       |  |  |  |

| ENABLE              | 18     | Digital ENABLE input                             |  |  |  |

| PHASE               | 19     | Digital PHASE input                              |  |  |  |

| RC                  | 20     | Terminal to set blank- and off-time              |  |  |  |

| PAD                 | _      |                                                  |  |  |  |

# Full-Bridge PWM Gate Driver

# ELECTRICAL CHARACTERISTICS: valid for Temperature Range G version at $T_J$ = 25°C and for Temperature Range K version at $T_J$ = -40°C to 150°C, $V_{BB}$ = 5.5 to 50 V, unless otherwise specified

| Characteristics                | Symbol                | Test Conditions                                                           | Min. | Тур. | Max. | Unit  |

|--------------------------------|-----------------------|---------------------------------------------------------------------------|------|------|------|-------|

| VDD Owner to Owner of          | I <sub>BB</sub>       |                                                                           | _    | 6    | 10   | mA    |

| VBB Supply Current             | I <sub>BB</sub>       | SLEEPn = low, Standby Mode                                                | _    | _    | 5    | μΑ    |

| Gate Drive                     | •                     |                                                                           |      |      |      |       |

| Llimb Cida Cata Daiva Ovtavit  | CIT                   | Relative to V <sub>BB</sub> , I <sub>GATE</sub> = 200 μA, VBB = 8 to 50 V | 6.5  | 6.8  | 7.5  |       |

| High-Side Gate Drive Output    | GH                    | Relative to V <sub>BB</sub> , I <sub>GATE</sub> = 200 μA, VBB = 5.5 V     | _    | 5.2  | _    | · V   |

| Law Side Cate Drive Output     | CI                    | I <sub>GATE</sub> = 200 μA, VBB = 8 to 50 V                               | 6.5  | 6.8  | 7.5  | .,    |

| Low-Side Gate Drive Output     | GL                    | I <sub>GATE</sub> = 200 μA, VBB = 5.5 V                                   | _    | 5.4  | _    | V     |

| Gate Drive Pull-Up Current     | I <sub>GPU</sub>      | R <sub>ISET</sub> = 30 kΩ; GH = GL = 4 V                                  | 21   | 30   | 39   | mA    |

| Gate Drive Pull-Down Current   | I <sub>GPD</sub>      | R <sub>ISET</sub> = 30 kΩ; GH = GL = 4 V                                  | 47   | 68   | 89   | mA    |

| Dead-Time                      | t <sub>DT</sub>       |                                                                           | _    | 1000 | _    | ns    |

| Passive Pull-Down Resistance   | R <sub>GPD</sub>      |                                                                           | 30   | 50   | 70   | kΩ    |

| Logic Input and Output         |                       |                                                                           |      |      |      |       |

| Logic Output Voltage           | V <sub>OCLn</sub>     | I = 2 mA, Overcurrent Detected                                            | -    | 0.2  | 0.3  | V     |

| Logic Output Leakage           | I <sub>OCLn</sub>     | V = 5 V, Normal Operation                                                 | -    | -    | 5    | μA    |

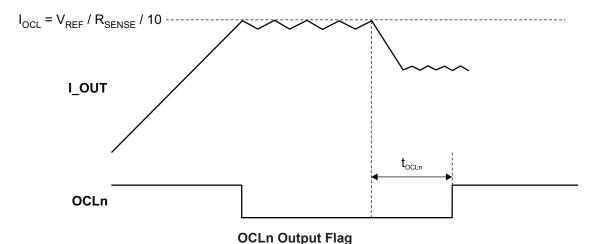

| PWM Current Limit Flag Timer   | t <sub>OCLn</sub>     |                                                                           | 300  | 500  | 600  | us    |

|                                | V <sub>IH</sub>       |                                                                           | 2.0  | _    | _    | V     |

| Logic Input Voltage            | V <sub>IL</sub>       |                                                                           | _    | _    | 0.8  | V     |

|                                | V <sub>ILSLEEPn</sub> | SLEEPn input                                                              | _    | _    | 0.4  | V     |

| Logic Input Hysteresis         | V <sub>HYS</sub>      |                                                                           | _    | 320  | _    | mV    |

| Logic Input Pull-Down Resistor | R <sub>PD</sub>       |                                                                           | 30   | 50   | 70   | kΩ    |

| VREF Input Current             | I <sub>VREF</sub>     | V <sub>REF</sub> = 2.5 V                                                  | -5   | < 1  | 5    | μΑ    |

| VREF Input Range               | $V_{REF}$             |                                                                           | 0    | _    | 2.5  | V     |

| Current Gain                   | A <sub>V</sub>        | VREF/ V <sub>SENSE</sub> , VREF = 2.5 V                                   | 9.5  | _    | 10.5 | V/V   |

| Input Offset, SENSE            | V <sub>OSSENSE</sub>  |                                                                           | -10  | _    | 10   | mV    |

| Fixed Off-Time                 | T <sub>OFF</sub>      | $R_{RC}$ = 30 k $\Omega$ , $C_{RC}$ = 1 nF                                | -    | 30   | _    | μs    |

| Blank-Time                     | T <sub>BLK</sub>      | $R_{RC}$ = 30 k $\Omega$ , $C_{RC}$ = 1 nF                                | 2.1  | 3    | 3.9  | μs    |

| Power-Up Delay                 | Tpu                   | Time until outputs are enabled                                            | _    | 50   | 300  | μs    |

| AIOUT Gain                     | A <sub>IOUT</sub>     | AIOUT/V <sub>SENSE</sub> , V <sub>SENSE</sub> = 50 to 200 mV              | 9    | 10   | 11   | V/V   |

| Input Offset, AIOUT            | V <sub>OSAIOUT</sub>  |                                                                           | -15  | -    | 15   | mV    |

| Sample-and-Hold Accuracy       | SH <sub>ACC</sub>     |                                                                           | -    | 15   | _    | mV    |

| Sample-and-Hold Droop Rate     | V <sub>DROOP</sub>    |                                                                           | -    | _    | 1    | mV/µs |

| AIOUT Output Impedance         | ROUT <sub>AIOUT</sub> |                                                                           | 0.75 | 1.00 | 1.45 | kΩ    |

| Protection Circuits            |                       |                                                                           |      |      |      |       |

| UVLO Enable Threshold          | UVLO <sub>VBB</sub>   | V <sub>BB</sub> rising                                                    | 5.10 | 5.25 | 5.40 | V     |

| UVLO Hysteresis                | UVLO <sub>HYS</sub>   |                                                                           | 200  | 300  | 350  | mV    |

| VDS Threshold                  | VDS <sub>THRES</sub>  |                                                                           | _    | 2    | _    | V     |

| Thermal Shutdown Temperature   | T <sub>JTSD</sub>     | Temperature increasing                                                    | 150  | 165  | 185  | °C    |

| Thermal Shutdown Hysteresis    | ΔT <sub>J</sub>       | Recovery = $T_{JTSD} - \Delta T_{J}$                                      | -    | 30   | _    | °C    |

$<sup>^{1}</sup> Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization \\ ^{2} Target trip level = <math>V_{DSTH} = V_{DRAIN} - Sx$  (High Side On) or  $V_{DSTH} = Sx - SENSE$  (Low Side On)

# **Control Logic**

| SLEEPn | PHASE | ENABLE | 10 × V <sub>SENSE</sub> > V <sub>REF</sub> | OUTA | OUTB | Function                     |

|--------|-------|--------|--------------------------------------------|------|------|------------------------------|

| 0      | Х     | х      | x                                          | Z    | Z    | Standby Mode                 |

| 1      | Х     | 0      | false                                      | L    | L    | EN Chop, Slow Decay SR       |

| 1      | 0     | 1      | false                                      | L    | Н    | Reverse                      |

| 1      | 1     | 1      | false                                      | Н    | L    | Forward                      |

| 1      | Х     | 1      | true                                       | L    | L    | Internal Chop, Slow Decay SR |

<sup>\*</sup> In fast decay, outputs change to high-Z state when load current approaches zero, to prevent reversal of current.

OCLn output function is described in the Functional Description section.

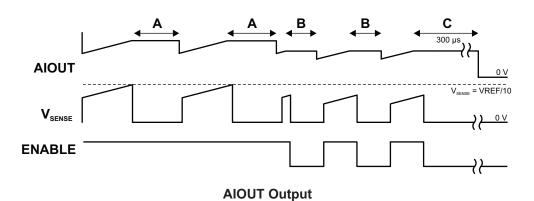

- A. Internal OCL chop. AIOUT holds while SENSE voltage drops to 0 V during the slow-decay off-time.

- B. ENABLE chop. AIOUT holds while SENSE voltage drops to 0 V during slow decay.

- C. Slow-decay timeout. AIOUT is forced to 0 V 300 µs after ENABLE goes low.

# **FUNCTIONAL DESCRIPTION**

# **Device Operation**

The A5957 is designed to operate DC motors. The output drivers are capable of 50 V with gate-driver capability for an all n-channel external MOSFET H-bridge. Control logic includes synchronous rectification to reduce power dissipation. Current limit is regulated by fixed off-time pulse-width-modulated (PWM) control circuitry.

#### Internal PWM Current Control

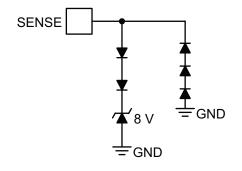

Peak current is regulated by monitoring the voltage on an external sense resistor.

$$I_{PEAK} = \frac{V_{REF}}{(10 \times R_{SENSE})}$$

When the peak current is exceeded, the source driver turns off for a fixed period t<sub>OFF</sub> to chop the current. The outputs operate in mixed-decay mode during t<sub>OFF</sub>. Refer to the Fixed Off-Time Setting section to set t<sub>OFF</sub>.

The internal current-sense circuit is ignored for t<sub>BLANK</sub> after PWM transitions. The comparator output is blanked to prevent false overcurrent detection due to reverse recovery currents of the clamp diodes, or switching transients related to the capacitance of the load, or both. Refer to the Blank-Time Setting section to set  $t_{\rm BLANK}$ .

#### **Brake**

It is important to note that the internal PWM current control circuit will not limit the current when braking, since the current does not flow through the sense resistor. The maximum current can be approximated by  $V_{BEMF}$  /  $R_{MOTOR}$ . Care should be taken to ensure that the maximum ratings of the external MOSFET are not exceeded in worst-case braking situations of high speed and high inertial loads.

# **ISET**

A resistor from ISET terminal to ground sets the magnitude of the gate current. The sink and source current ratios are fixed at approximately 2-to-1 where the pull-down current is approximately two times the pull-up current. R<sub>ISET</sub> should be between 20 and 150 k $\Omega$ .

The formula for determining the gate drive is:

$$I_{GATE\_HS}(mA) = 1.9 + \frac{900}{R_{ISET}(k\Omega)}$$

$$I_{GATE\_LS}(mA) = 3.5 + \frac{1700}{R_{ISET}(k\Omega)}$$

#### **RC**

The RC terminal is used to set both fixed off-time and blank-time for the internal PWM current control. Refer to the following three sections to select RC component values.

# Fixed Off-Time Setting

The internal PWM current-control circuitry uses a one-shot to control the time the drivers remain off. The one-shot off-time (t<sub>OFF</sub>) is determined by the selection of an external resistor and capacitor connected from the RC timing terminal to ground. The off-time, over a range of values of  $C_{RC} = 470$  to 1500 pF and  $R_{RC} = 12$  to 100 k $\Omega$ , is approximated by:

$$t_{OFF} = R_{RC} \times C_{RC} + dead time$$

# Blank-Time Setting

This circuit blanks the output of the current-sense comparator when the outputs are switched by the internal current-control circuitry or by an external PWM chop command. The comparator blanking time, t<sub>BLANK</sub>, is determined by the selection of an external resistor and capacitor connected from the RC timing terminal to ground, and is approximated by:

$$t_{\scriptscriptstyle BLANK} = 2.6~\mu s \times C_{\scriptscriptstyle RC}~(nF) \times e^{(3.6/R_{\scriptscriptstyle RC}(k\Omega))}$$

# Slow Decay

In slow-decay mode, the low-side switch stays on and the high-side switch turns off. Due to the synchronous rectification feature, the complementary low-side switch turns on after a deadtime.

# OCLn Output

An open drain logic output will be driven low to indicate system operation. The OCLn terminal is driven low under two conditions:

- 1. When the system is limiting current to value set by VREF and R<sub>SENSE</sub>. Once overcurrent events are no longer detected, the A5957 will release the indication after a time t<sub>OCLn</sub>.

- 2. When a VDS fault is detected, the OCLn terminal is driven low. It is released when the fault is reset.

The OCLn terminal, in combination with the AIOUT terminal, can provide valuable information about how the system is behaving:

Overcurrent events can indicate a motor stall condition, in which case the system controller can respond to the fault condition by reducing PWM duty. When OCLn is low and the voltage on AIOUT is greater than 0 V, the controller is actively

6

limiting current with the internal, fixed off-time PWM current limiter.

In the case of a VDS fault, the OCLn terminal is also driven low, but the AIOUT voltage will be 0 V, because the bridge has been disabled. This notifies the user that a VDS fault has occurred and the driver has been disabled

# **AIOUT**

An analog output can be used to monitor current through the external sense resistor (if used). The SENSE voltage is gained by a factor of 10 and fed to the AIOUT terminal. A sample-and-hold circuit is used to capture the voltage across the sense resistor and holds it during periods when the voltage is not representative of the current in the motor. The AIOUT Output diagram illustrates when the voltage is held. The held voltage will droop at a rate equal to V<sub>DROOP</sub>. In the case of a VDS fault on the bridge, the AIOUT terminal will be discharged to zero volts.

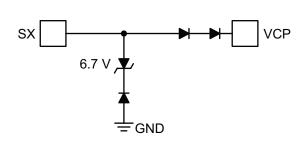

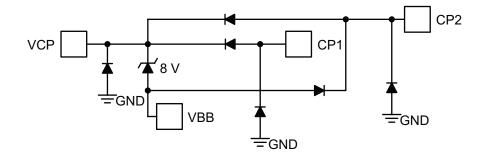

# **Charge Pump**

The Charge Pump is used to generate a supply above VBB to drive the high-side MOSFETs. The VCP voltage is internally monitored and, in the case of a fault condition, the outputs of the device are disabled.

#### **MOSFET VDS Protection**

The drain-to-source voltage is monitored across the MOSFET any time the MOSFET is on. If the voltage across the MOSFET exceeds VDS<sub>THRES</sub>, the bridge is disabled and latched off.

In order to prevent false VDS faults, the VDS monitor is blanked immediately after any MOSFET is turned on. The VDS monitor waits for a blank-time defined by the components on the RC terminal before monitoring the VDS level. During the off-time when SR is active, VDS blanking is fixed at 1 µs.

# **VDS Fault**

When a VDS fault occurs, and the bridge is disabled, and the fault is latched, the OCLn terminal is immediately driven low. The latch can only be reset by going into standby or by dropping VBB below the UVLO threshold.

# Standby Mode

Low power standby mode is activated when SLEEPn is brought low. Standby mode disables most of the internal circuitry, including the charge pump and internal regulator. When coming out of standby mode, the A5957 requires up to 300 µs before the outputs can respond to input commands.

#### **TSD**

If the die temperature increases to approximately  $T_{TSD}$ , the full bridge outputs will be disabled until the internal temperature falls below T<sub>TSD</sub> minus a hysteresis level of T<sub>HYS</sub>.

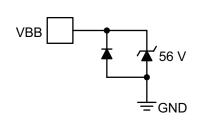

#### Fault Shutdown

In the event of a fault due to excessive junction temperature, or low voltage on VCP or VBB, the outputs of the device are disabled until the fault condition is removed. At power-up, the UVLO circuit disables the drivers until the UVLO thresholds are exceeded.

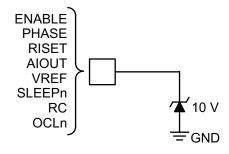

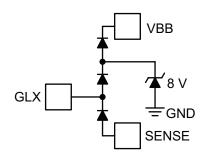

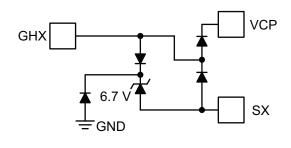

# **TERMINAL CIRCUIT DIAGRAMS**

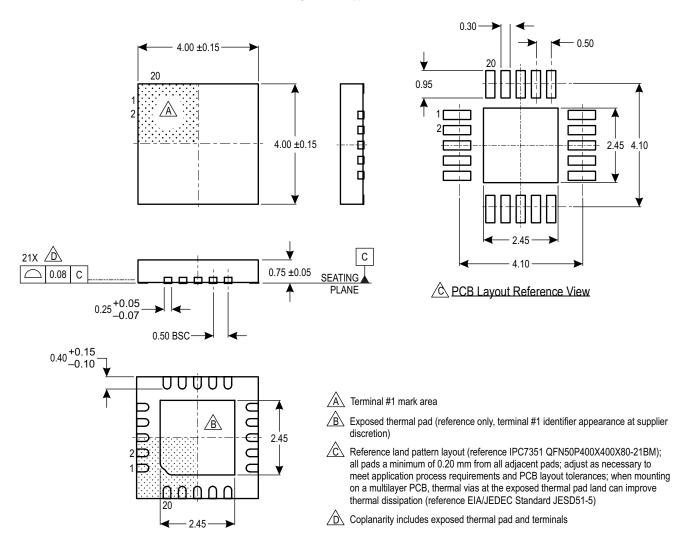

# PACKAGE OUTLINE DRAWINGS

# For Reference Only - Not for Tooling Use

(Reference JEDEC MO-220WGGD)

Dimensions in millimeters

NOT TO SCALE

Exact case and lead configuration at supplier discretion within limits shown

ES Package, 20-Pin QFN with Exposed Thermal Pad

# A5957

# Full-Bridge PWM Gate Driver

# **Revision History**

| Revision | Revision Date     | Description of Revision                                                                                           |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------------|

| _        | February 12, 2015 | Initial Release                                                                                                   |

| 1        | July 14, 2015     | Updated functional block diagram (page 1); added packing information (page 2); changed references to LSS to SENSE |

Copyright ©2015, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com