### **General Description**

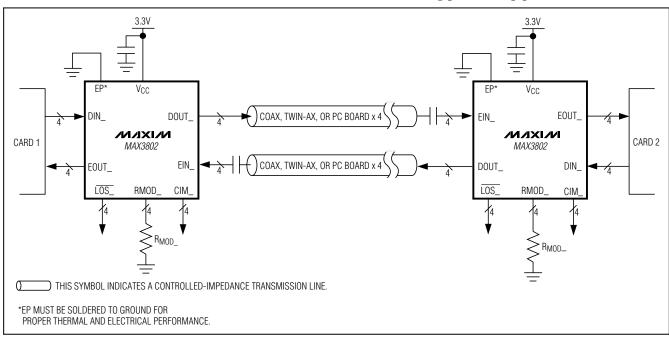

The MAX3802 has four independent adaptive cable equalizers and cable drivers on a single chip. It is designed for coaxial and twin-axial cable point-to-point scrambled-data communication applications. The driver features differential current-mode logic (CML) inputs and outputs. The equalizer includes differential CML data inputs and outputs and a TTL loss-of-signal (LOS) output.

The adaptive cable equalizer can equalize differential or single-ended signals at data rates up to 3.2Gbps. It automatically adjusts to attenuation caused by skineffect losses of 30dB at 1.6GHz. The equalizer effectively extends the usable length of copper cable in high-frequency interconnect applications.

## **Applications**

High-Speed Links in Communications and Data Systems

Backplane and Twin-Axial Cable Interconnects

Category 5 UTP-Based Systems

Digital Video Systems

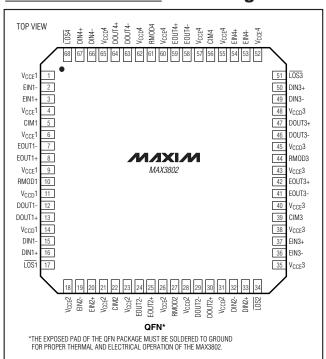

Pin Configuration appears at end of data sheet.

#### **Features**

- ♦ Single 3.3V Operation

- Four Independent Equalizers and Drivers

- ♦ 725mW at 3.3V Typical Power Dissipation

- ♦ Data Rates Up to 3.2Gbps

- **♦** Equalizer Automatically Adjusts for Different Cable Lengths

- ♦ 0 to 30dB Equalization at 1.6GHz (3.2Gbps)

- ♦ Loss-of-Signal (LOS) Indicator

- ♦ On-Chip Input and Output Terminations

- **♦ Low External Component Count**

- ♦ 0°C to +85°C Operating Temperature Range

- ♦ ESD Protection on Cable Inputs and Outputs

### **Ordering Information**

| PART        | TEMP<br>RANGE | PIN-<br>PACKAGE | PACKAGE<br>CODE |  |

|-------------|---------------|-----------------|-----------------|--|

| MAX3802UGK  | 0°C to +85°C  | 68 QFN          | G6800-2         |  |

| MAX3802UTK+ | 0°C to +85°C  | 68 QFN          | T6800-4         |  |

<sup>+</sup>Denotes lead-free package.

# Typical Application Circuit

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VCC             | 0.5V to +6.0V                       |

|---------------------------------|-------------------------------------|

| Voltage at LOS_, CIM_, and RMOD | 0.5V to $(V_{CC} + 0.5V)$           |

| Voltage at EIN_+, EIN,          |                                     |

| DIN_+, and DIN(Vo               | $_{CC}$ - 1V) to ( $V_{CC}$ + 0.5V) |

| Current Out of EOUT_+, EOUT,    |                                     |

| DOUT_+, and DOUT                | 25mA                                |

| Continuous Power Dissipation ( $T_A = +85^{\circ}C$ ) |

|-------------------------------------------------------|

| 68-Pin QFN (derate 44.8mW/°C above +85°C)1.44W        |

| Operating Ambient Temperature Range0°C to +85°C       |

| Storage Ambient Temperature Range55°C to +150°C       |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.14V \text{ to } 3.46V, T_A = 0^{\circ}\text{C to } +85^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = 3.3V \text{ and } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                             | SYMBOL                                   | CONDITIONS                              | MIN                   | TYP  | MAX                   | UNITS             |  |

|---------------------------------------|------------------------------------------|-----------------------------------------|-----------------------|------|-----------------------|-------------------|--|

| Supply Current                        | Icc                                      | Includes external load current (Note 1) |                       | 220  | 345                   | mA                |  |

| CABLE DRIVER INPUT SPECIF             | ICATIONS                                 |                                         |                       |      |                       |                   |  |

| Input Voltage (Single Ended)          | V <sub>DIN</sub> _+,<br>V <sub>DIN</sub> |                                         | V <sub>CC</sub> - 0.6 |      | V <sub>CC</sub> + 0.2 | V                 |  |

| Input Voltage (Differential)          | V <sub>DIN</sub> _                       |                                         | 400                   |      | 1100                  | mV <sub>P-P</sub> |  |

| Input Impedance                       |                                          | Single ended                            | 40                    | 50   | 60                    | Ω                 |  |

| CABLE DRIVER OUTPUT SPEC              | CIFICATIONS                              |                                         |                       |      |                       |                   |  |

| Output Valtage (Differential)         |                                          | RMOD_ = $10k\Omega$ (Note 2)            | 750                   | 825  | 1000                  | ma\/              |  |

| Output Voltage (Differential)         |                                          | RMOD_ = $20k\Omega$ (Note 2)            | 400                   | 445  | 550                   | mV <sub>P-P</sub> |  |

| Output Impedance                      |                                          | Single ended                            | 50                    | 62.5 | 75                    | Ω                 |  |

| CABLE EQUALIZER INPUT SP              | ECIFICATION                              | IS                                      |                       |      |                       |                   |  |

| Minimum Cable Input<br>(Differential) |                                          | 3.2Gbps, 30dB cable loss (Note 3)       |                       |      | 400                   | mV <sub>P-P</sub> |  |

| Maximum Cable Input (Differential)    |                                          |                                         |                       | 600  |                       | mV <sub>P-P</sub> |  |

| Input Impedance                       |                                          |                                         | 40                    | 50   | 60                    | Ω                 |  |

| CABLE EQUALIZER OUTPUT                | SPECIFICATION                            | ONS                                     | •                     |      |                       |                   |  |

| Output Voltage (Differential)         |                                          | (Note 2)                                | 500                   |      | 1000                  | mV <sub>P-P</sub> |  |

| Output Impedance                      |                                          | Single ended                            | 50                    | 62.5 | 75                    | Ω                 |  |

| Voltage at LOS_                       |                                          | Output high (Note 4)                    | 2.4                   |      |                       | V                 |  |

| vollage at LOS_                       |                                          | Output low (Note 4)                     |                       |      | 0.4                   | v                 |  |

#### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.14V \text{ to } 3.46V, T_A = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ . Typical values are at  $V_{CC} = 3.3V$  and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                            | SYMBOL CONDITIONS |                                  | MIN | TYP  | MAX  | UNITS              |

|--------------------------------------|-------------------|----------------------------------|-----|------|------|--------------------|

| Maximum Input Data Rate              |                   |                                  | 3.2 |      |      | Gbps               |

| CABLE DRIVER SPECIFICAT              | IONS              |                                  |     |      |      |                    |

| Random Jitter                        |                   | 3.2Gbps input                    |     | 2.7  | 4    | mUI <sub>RMS</sub> |

| Deterministic Jitter                 |                   | (Notes 6, 9)                     |     | 20   | 60   | mUI <sub>P-P</sub> |

| Output Edge Speed                    |                   | 20% to 80%                       |     | 60   | 90   | ps                 |

| Input Return Loss<br>(Differential)  |                   | ≤ 2.5GHz                         |     | -20  |      | dB                 |

| Output Return Loss<br>(Differential) |                   | ≤ 2.5GHz                         |     | -13  |      | dB                 |

| <b>EQUALIZER SPECIFICATION</b>       | S                 |                                  |     |      |      |                    |

|                                      |                   | 0dB cable loss (Note 8)          |     | 0.10 | 0.24 |                    |

| Residual Jitter (Notes 7, 9)         |                   | 24dB cable loss (Note 8)         |     | 0.11 | 0.20 | UI <sub>P-P</sub>  |

|                                      |                   | 30dB cable loss (Note 8)         |     | 0.08 | 0.20 |                    |

| Output Edge Speed                    |                   | 20% to 80%                       |     | 60   | 90   | ps                 |

| Input Return Loss<br>(Differential)  |                   | ≤ 2.5GHz                         |     | -16  |      | dB                 |

| Output Return Loss<br>(Differential) |                   | ≤ 2.5GHz                         |     | -14  |      | dB                 |

| Equalizer Compensation               |                   | 1.6GHz (skin-effect losses only) | 30  |      |      | dB                 |

| Equalizer Time Constant              |                   | (Note 10)                        |     | 6    |      | μs                 |

- Note 1: Equalizer total currents (equalizer with maximum equalization) and  $R_{MOD} = 10k\Omega$  (maximum driver swing).

- **Note 2:** Input voltage within specification limits,  $50\Omega$  to  $V_{CC}$  at each output.

- **Note 3:** Minimum cable input for  $\overline{LOS}$  to deassert high.

- **Note 4:**  $100k\Omega$  load to ground. The minimum input signal level that turns off the  $\overline{LOS}_{-}$  alarm depends on the data rate and cable length.

- Note 5: AC electrical characteristics are guaranteed by design and characterization.

- Note 6:  $V_{DIN}$  = 400m $V_{P-P}$  to 1100m $V_{P-P}$  (differential),  $10k\Omega \le R_{MOD} \le 20k\Omega$ , 3.2Gbps  $2^{13}$  -1 PRBS plus 100 consecutive ones and 100 consecutive zeros.

- Note 7: Includes random jitter and deterministic jitter for BER of 10<sup>-12</sup>.

- Note 8: Differential cable input voltage = 400mV<sub>P-P</sub>, 3.2Gbps 2<sup>13</sup> -1 PRBS plus 100 consecutive ones and 100 consecutive zeros.

- **Note 9:** Isolation test: three channels driven with identical 3.2Gbps PRBS with maximum input signal to each equalizer and maximum input signal on driver. The measured channel meets the residual and random jitter specifications with an uncorrelated 3.2Gbps PRBS data at minimum input signal level on equalizer and maximum signal level on driver.

- Note 10: Equalizer time constant measured from data on to closed-loop operation.

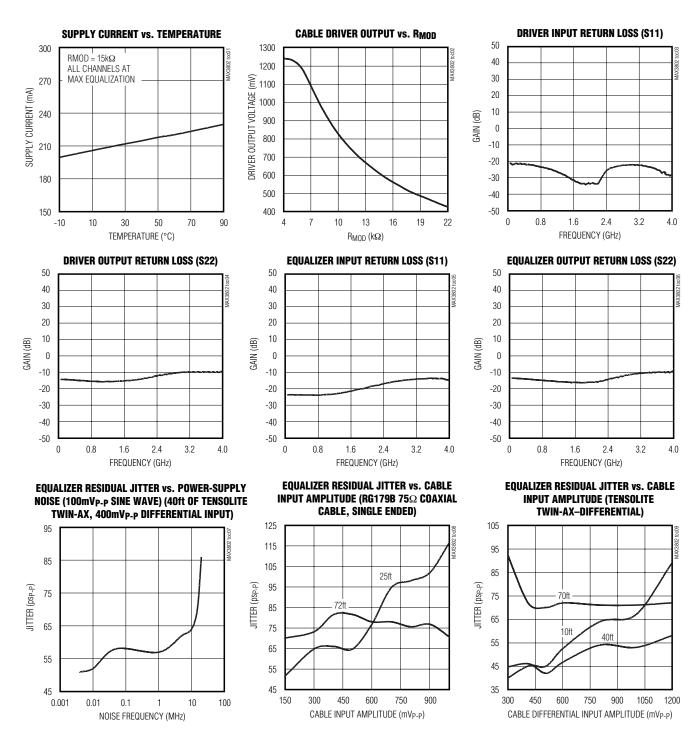

## **Typical Operating Characteristics**

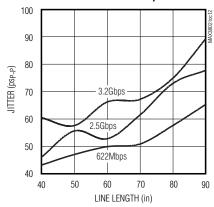

(V<sub>CC</sub> = 3.3V, T<sub>A</sub> = +25°C, all jitter measurements done at 3.2Gbps, 600mV cable input with 2<sup>13</sup> - 1 PRBS pattern with 100 consecutive ones and 100 consecutive zeros substituted. **Note:** Test pattern produces near-worst-case jitter results. Results vary with pattern, unless otherwise noted.)

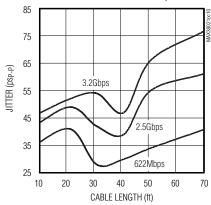

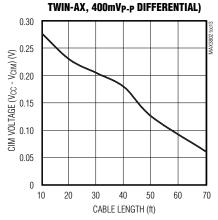

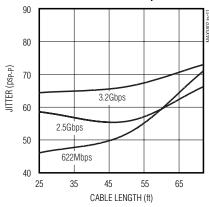

## Typical Operating Characteristics (continued)

(V<sub>CC</sub> = 3.3V, T<sub>A</sub> = +25°C, all jitter measurements done at 3.2Gbps, 600mV cable input with 2<sup>13</sup> - 1 PRBS pattern with 100 consecutive ones and 100 consecutive zeros substituted. Note: Test pattern produces near-worst-case jitter results. Results vary with pattern, unless otherwise noted.)

#### **EQUALIZER RESIDUAL JITTER vs. CABLE** LENGTH (TENSOLITE TWIN-AX, 400mV<sub>P-P</sub> **DIFFERENTIAL INPUT)**

# **CIM VOLTAGE vs. CABLE LENGTH (TENSOLITE**

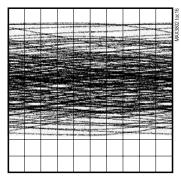

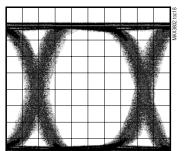

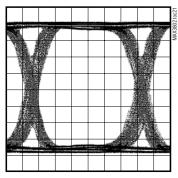

**CABLE OUTPUT EYE DIAGRAM AFTER 70ft** OF TENSOLITE TWIN-AX CABLE (27 - 1 PRBS **NO EQUALIZATION)**

60ps/div (2.5Gbps)

**EQUALIZER RESIDUAL JITTER vs. CABLE** LENGTH (RG179B 75 $\Omega$  COAXIAL, 300mV<sub>P-P</sub> SINGLE ENDED)

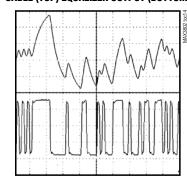

**EQUALIZER INPUT AFTER 115ft OF CABLE (TOP) EQUALIZER OUTPUT (BOTTOM)**

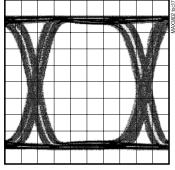

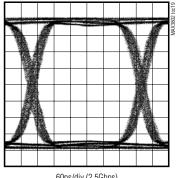

**EQUALIZER OUTPUT EYE DIAGRAM AFTER 70ft** OF TENSOLITE TWIN-AX CABLE (27 - 1 PRBS)

60ps/div (2.5Gbps)

#### **EQUALIZER RESIDUAL JITTER vs. LINE** LENGTH (FR-4 6mil STRIPLINE, 300mV<sub>P-P</sub> SINGLE ENDED)

**EQUALIZER OUTPUT EYE DIAGRAM AFTER** 155ft OF 50Ω GORE-89 CABLE (400mV<sub>P-P</sub>)

#### **EQUALIZER OUTPUT EYE DIAGRAM AFTER 72ft** OF 75 $\Omega$ RG179 CABLE (300mV<sub>P-P</sub> SINGLE ENDED, 2<sup>23</sup> - 1 PRBS)

48ps/div (3.2Gbps)

## Typical Operating Characteristics (continued)

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, all jitter measurements done at 3.2Gbps, 600mV cable input with 2<sup>13</sup> - 1 PRBS pattern with 100 consecutive ones and$ 100 consecutive zeros substituted. Note: Test pattern produces near-worst-case jitter results. Results vary with pattern, unless otherwise noted.)

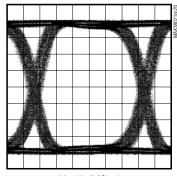

#### **EQUALIZER OUTPUT EYE DIAGRAM AFTER 60in OF** FR-4 6mil STRIPLINE (DIFFERENTIAL, 27 - 1 PRBS)

60ps/div (2.5Gbps)

#### **EQUALIZER OUTPUT EYE DIAGRAM AFTER 288ft** OF RG59 CABLE (300mV<sub>P-P</sub> SINGLE ENDED, 2<sup>23</sup> - 1 PRBS)

60ps/div (2.5Gbps)

#### **EQUALIZER OUTPUT EYE DIAGRAM AFTER 50ft OF MADISON 14887 SHIELDED TWISTED-PAIR** CABLE (27 - 1 PRBS)

60ps/div (2.5Gbps)

## **Pin Description**

|                |                    | •                                           |  |  |  |

|----------------|--------------------|---------------------------------------------|--|--|--|

| PIN            | NAME               | FUNCTION                                    |  |  |  |

| 1, 4, 6, 9     | V <sub>CCE</sub> 1 | 3.3V Supply Voltage for Equalizer 1         |  |  |  |

| 2              | EIN1-              | Negative Equalizer 1 Input, CML             |  |  |  |

| 3              | EIN1+              | Positive Equalizer 1 Input, CML             |  |  |  |

| 5              | CIM1               | Cable Integrity Monitor 1 Output            |  |  |  |

| 7              | EOUT1-             | Negative Equalizer 1 Output, CML            |  |  |  |

| 8              | EOUT1+             | Positive Equalizer 1 Output, CML            |  |  |  |

| 10             | RMOD1              | Driver 1 Output Modulation Adjust           |  |  |  |

| 11, 14         | V <sub>CCD</sub> 1 | 3.3V Supply Voltage for Driver 1            |  |  |  |

| 12             | DOUT1-             | Negative Driver 1 Output, CML               |  |  |  |

| 13             | DOUT1+             | Positive Driver 1 Output, CML               |  |  |  |

| 15             | DIN1-              | Negative Driver 1 Input, CML                |  |  |  |

| 16             | DIN1+              | Positive Driver 1 Input, CML                |  |  |  |

| 17             | LOS1               | Equalizer 1 Loss-of-Signal, TTL, Active Low |  |  |  |

| 18, 21, 23, 26 | V <sub>CCE</sub> 2 | 3.3V Supply Voltage for Equalizer 2         |  |  |  |

| 19             | EIN2-              | Negative Equalizer 2 Input, CML             |  |  |  |

| 20             | EIN2+              | Positive Equalizer 2 Input, CML             |  |  |  |

| 22             | CIM2               | Cable Integrity Monitor 2 Output            |  |  |  |

| 24             | EOUT2-             | Negative Equalizer 2 Output, CML            |  |  |  |

| 25             | EOUT2+             | Positive Equalizer 2 Output, CML            |  |  |  |

| 27             | RMOD2              | Driver 2 Output Modulation Adjust           |  |  |  |

| 28, 31         | V <sub>CCD</sub> 2 | 3.3V Supply Voltage for Driver 2            |  |  |  |

| 29             | DOUT2-             | Negative Driver 2 Output, CML               |  |  |  |

| 30             | DOUT2+             | Positive Driver 2 Output, CML               |  |  |  |

# \_Pin Description (continued)

| PIN            | NAME                        | FUNCTION                                                                                                                     |

|----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 32             | DIN2-                       | Negative Driver 2 Input, CML                                                                                                 |

| 33             | DIN2-                       | Positive Driver 2 Input, CML                                                                                                 |

| 34             | LOS2                        |                                                                                                                              |

| 35, 38, 40, 43 |                             | Equalizer 2 Loss-of-Signal, TTL, Active Low  3.3V Supply Voltage for Equalizer 3                                             |

| 36             | V <sub>CCE</sub> 3<br>EIN3- |                                                                                                                              |

| 37             | EIN3+                       | Negative Equalizer 3 Input, CML                                                                                              |

|                |                             | Positive Equalizer 3 Input, CML                                                                                              |

| 39             | CIM3                        | Cable Integrity Monitor 3 Output                                                                                             |

| 41             | EOUT3-                      | Negative Equalizer 3 Output, CML                                                                                             |

| 42             | EOUT3+                      | Positive Equalizer 3 Output, CML                                                                                             |

| 44             | RMOD3                       | Driver 3 Output Modulation Adjust                                                                                            |

| 45, 48         | V <sub>CCD</sub> 3          | 3.3V Supply Voltage for Driver 3                                                                                             |

| 46             | DOUT3-                      | Negative Driver 3 Output, CML                                                                                                |

| 47             | DOUT3+                      | Positive Driver 3 Output, CML                                                                                                |

| 49             | DIN3-                       | Negative Driver 3 Input, CML                                                                                                 |

| 50             | DIN3+                       | Positive Driver 3 Input, CML                                                                                                 |

| 51             | LOS3                        | Equalizer 3 Loss-of-Signal, TTL, Active Low                                                                                  |

| 52, 55, 57, 60 | V <sub>CCE</sub> 4          | 3.3V Supply Voltage for Equalizer 4                                                                                          |

| 53             | EIN4-                       | Negative Equalizer 4 Input, CML                                                                                              |

| 54             | EIN4+                       | Positive Equalizer 4 Input, CML                                                                                              |

| 56             | CIM4                        | Cable Integrity Monitor 4 Output                                                                                             |

| 58             | EOUT4-                      | Negative Equalizer 4 Output, CML                                                                                             |

| 59             | EOUT4+                      | Positive Equalizer 4 Output, CML                                                                                             |

| 61             | RMOD4                       | Driver 4 Output Modulation Adjust                                                                                            |

| 62, 65         | V <sub>CCD</sub> 4          | 3.3V Supply Voltage for Driver 4                                                                                             |

| 63             | DOUT4-                      | Negative Driver 4 Output, CML                                                                                                |

| 64             | DOUT4+                      | Positive Driver 4 Output, CML                                                                                                |

| 66             | DIN4-                       | Negative Driver 4 Input, CML                                                                                                 |

| 67             | DIN4+                       | Positive Driver 4 Input, CML                                                                                                 |

| 68             | LOS4                        | Equalizer 4 Loss-of-Signal, TTL, Active Low                                                                                  |

| EP             | Exposed<br>Pad              | Ground. Must be soldered to the circuit board ground for proper thermal and electrical performance (see <i>EP Package</i> ). |

### **Detailed Description**

The MAX3802 has four independent adaptive equalizers (receivers) and four independent drivers. Disconnecting the power pins of unused equalizers and drivers lowers the power consumption of the MAX3802. Equalizer and driver descriptions apply to the four identical sections.

#### Cable Driver

The cable driver accepts differential or single-ended CML input data at rates up to 3.2Gbps. The maximum CML output of the driver can be adjusted over a typical range of 445mV to 825mV by changing the value of the  $R_{MOD}$  resistor between  $10k\Omega$  and  $20k\Omega$  (resistor connected between RMOD\_pin and ground).

#### **Adaptive Cable Equalizer**

The adaptive cable equalizer is capable of equalizing differential or single-ended CML input data at rates up

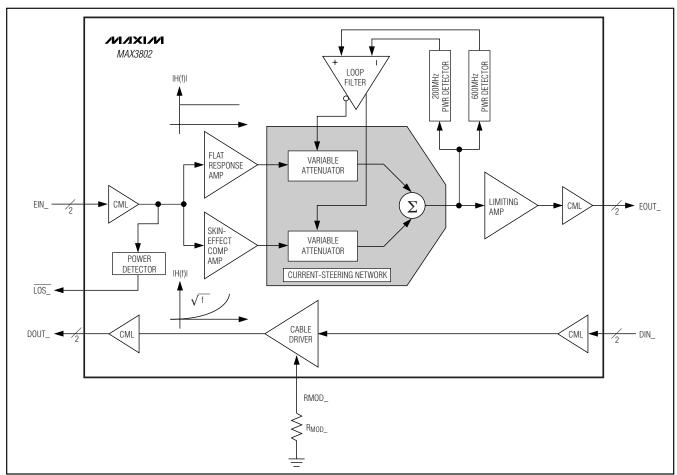

to 3.2Gbps. It automatically adjusts to attenuation levels of 30dB at 1.6GHz (due to skin-effect losses in copper cable). The equalizer consists of a CML input buffer, a flat-response amplifier, a skin-effect compensation amplifier, a current-steering network, a dual power-detector feedback loop, an output limiting amplifier, and a CML output buffer (Figure 1).

#### General Theory of Operation

The shape of the power spectrum of a random bit stream can be described by the square of the well-known sinc function, where  $\mathrm{sinc}(f) = \mathrm{sin}(\pi f)/(\pi f)$  for  $f \neq 0$ . For sufficiently long bit patterns (nonrandom bit stream),  $\mathrm{sinc}^2(f)$  is a good approximation. From the shape of the  $\mathrm{sinc}^2(f)$  function, the ratio of the power densities at any two frequencies can be estimated. The MAX3802 adaptive equalizer employs this principle by incorporating a feedback loop that continuously monitors the power at high- and low-frequency bands and

Figure 1. MAX3802 Functional Diagram

dynamically adjusts the equalizer to maintain the correct power ratio.

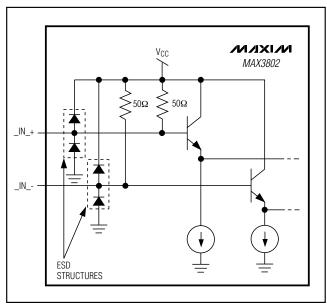

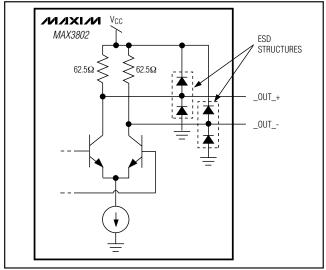

#### CML Input and Output Buffers

The input and output buffers are implemented using CML. Equivalent circuits are shown in Figures 2 and 3. For details on interfacing with CML, refer to Maxim Application Note HFAN-01.0, *Interfacing Between CML, PECL, and LVDS.*

Figure 2. CML Input Structure

Figure 3. CML Output Structure

#### Flat-Response and Skin-Effect Compensation Amplifiers

The buffered input waveform is fed equally to two amplifiers—the flat-response amplifier and the skineffect compensation amplifier. The flat-response amplifier has a constant gain over the entire frequency range of the device, and the skin-effect compensation amplifier has a gain characteristic that approximates the inverse of the skin-effect attenuation in copper cable. The skin-effect attenuation, in dB per unit length, is proportional to the square root of the frequency. The output currents from the amplifiers are supplied to the current-steering network.

#### **Current-Steering Network**

The function of the current-steering network is to combine adjustable quantities of the output currents from the flat-response and skin-effect compensation amplifiers in order to achieve a desired current ratio. The ratio adjustment is controlled by the dual power-detector feedback loop.

The current-steering network is implemented with a pair of variable attenuators that feed into a current-summing node. The variable attenuators are used to attenuate the output currents of the flat-response and skin-effect compensation amplifiers under control of the dual power-detector feedback loop. The outputs of the two attenuators are combined at the summing node and then fed to the output-limiting amplifier and the feedback loop.

#### **Dual Power-Detector Feedback Loop**

The outputs of the current-steering network are applied to the inputs of 200MHz and 600MHz power detectors. The outputs of the power detectors are applied to the loop-filter amplifier. This amplifier controls the variable attenuators in the current-steering network.

#### **Output Limiting Amplifier**

The output limiting amplifier amplifies the signal from the current-steering network to achieve the specified output voltage swing.

### Applications Information

Refer to Maxim Application Note HFDN-10.0, *Equalizing Gigabit Copper Cable Links with the MAX3800* (available at www.maxim-ic.com) for additional application information.

#### **Selecting RMOD**

The cable driver output amplitude can be adjusted by connecting a resistor (R<sub>MOD</sub>) with a value from  $10k\Omega$  to  $20k\Omega$  between the RMOD\_ pin and ground. The exact output amplitude of the driver is dependent on several

factors. See the *Typical Operating Characteristics* Cable Driver Output Voltage vs. R<sub>MOD</sub> for typical values.

#### **Cable Integrity Monitor**

The CIM\_ output voltage is directly proportional to the output current of the loop amplifier (which controls the current-steering network; see *Detailed Description*). This is an analog voltage output that indicates the amount of equalization being applied.

The amount of equalization (and thus the CIM\_ output level) is affected by cable type, cable length, signal bandwidth, etc. See the *Typical Operating Characteristics* CIM Voltage vs. Cable Length for typical values under specific conditions.

### Loss-of-Signal (LOS\_) Output

Loss of signal is indicated by the  $\overline{\text{LOS}}_-$  output. A low level on  $\overline{\text{LOS}}_-$  indicates that the equalizer input power has dropped below a threshold. When there is sufficient input voltage to the channel (typically greater than 250mV),  $\overline{\text{LOS}}_-$  is high. The  $\overline{\text{LOS}}_-$  output is suitable for indicating problems with the transmission link caused by, for example, a broken cable or a defective driver.

#### **Data Spectrum for Equalizer**

The MAX3802 equalizer design requires the data stream be scrambled or coded to provide a rich frequency spectrum for the adaptation algorithm. Scrambled patterns or coded patterns with scrambled content, such as 64b/66b or SONET PRBS, are ideal. Some coded patterns, such as 8b/10b, lack low-frequency energy and can be nonoptimal, requiring the user to characterize the specific application. In the absence of an input signal (nonstandard application), amplified noise may appear at the output due to the large gain of the device.

#### **Single-Ended Operation**

For single-ended operation of the cable driver or equalizer, connect the unused input to ground through a series combination of a capacitor (of equal value to other AC-coupling capacitors) and a  $50\Omega$  resistor. Note that the MAX3802 is specified for differential operation.

#### **Layout Considerations**

The MAX3802's performance can be significantly affected by circuit board layout and design. Use good high-frequency design techniques, including minimizing ground inductance and using controlled-impedance transmission lines for the high-frequency data signals. Power-supply decoupling capacitors should be placed as close as possible to VCC.

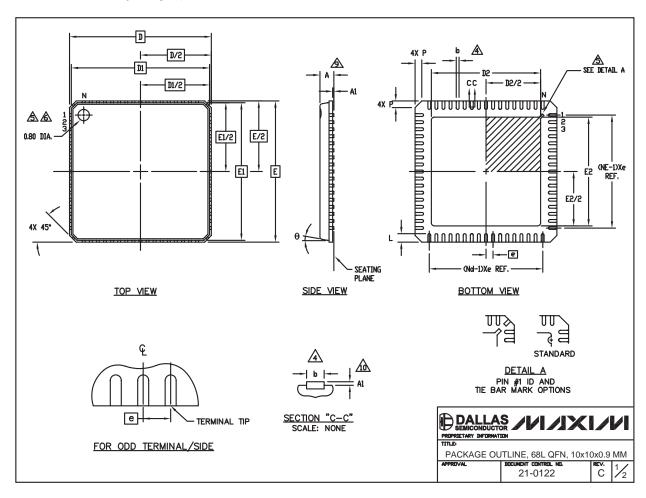

#### **Exposed-Pad Package**

The EP on the 68-pin QFN provides a very low thermal resistance path for heat removal from the IC. The pad is the electrical ground on the MAX3802 and must be soldered to the circuit board ground for proper thermal and electrical performance. Refer to Maxim Application Note HFAN-08.1, *Thermal Considerations for QFN and Other Exposed-Pad Packages* (available at www.maximic.com) for additional application information.

## **Chip Information**

TRANSISTOR COUNT: 5408

PROCESS: Bipolar (silicon germanium)

### Pin Configuration

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| S<br>Y M B O L | COMMON DIMENSIONS |           |      |                  |  |

|----------------|-------------------|-----------|------|------------------|--|

| B              | MIN.              |           |      |                  |  |

| A              | -                 | 0.90      | 1.00 | No <sub>TE</sub> |  |

| A1             | 0.00              | 0.01      | 0.05 | 11               |  |

| ь              | 0.18              | 0.23      | 0.30 | 4                |  |

| D              |                   | 10.00 BSC |      |                  |  |

| D1             | 9.75 BSC          |           |      |                  |  |

| е              | 0.50 BSC          |           |      |                  |  |

| Ε              | 10.00 BSC         |           |      |                  |  |

| E1             | 9.75 BSC          |           |      |                  |  |

| L              | 0.50              | 0.60      | 0.65 |                  |  |

| N              | 68                |           |      |                  |  |

| Nd             | 17                |           |      |                  |  |

| Ne             | 17                |           |      |                  |  |

| θ              | 0 12°             |           |      |                  |  |

| P              | 0 0.42 0.60       |           |      |                  |  |

- 1. DIE THICKNESS ALLOWABLE IS .012 INCHES MAXIMUM.

- DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- ∑5. THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY. DETAILS OF PIN #1 IDENTIFIER IS OPTIONAL, BUT MUST BE LOCATED WITHIN ZONE INDICATED.

- EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- ALL DIMENSIONS ARE IN MILLIMETERS.

- PACKAGE WARPAGE MAX 0.10mm.

- APPLIES TO EXPOSED SURFACE OF PADS AND TERMINALS APPLIES ONLY TO TERMINALS.

- 11. MEETS JEDEC MO-220.

| EXPOSED PAD VARIATIONS                |                         |     |     |     |     |      |  |  |  |  |

|---------------------------------------|-------------------------|-----|-----|-----|-----|------|--|--|--|--|

| D2 E2                                 |                         |     |     |     |     |      |  |  |  |  |

| PKG CODE                              | MIN                     | NDM | MAX | MIN | NDM | MAX  |  |  |  |  |

| G6800-2 7.55 7.70 7.85 7.55 7.70 7.85 |                         |     |     |     |     | 7.85 |  |  |  |  |

| G6800-4                               | 505 500 505 505 500 505 |     |     |     |     |      |  |  |  |  |

**Revision History**

Rev 0; 1/02: Initial data sheet release.

Added package code to Ordering Information table (page 1); updated package outline Rev 1: 5/03:

(pages 11-12).

Rev 2; 11/06: Added lead-free package to Ordering Information table (page 1).

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600