### 6 Channel DC/DC Converters

### **General Description**

The RT9911 is a complete power-supply solution for digital still cameras and other hand-held devices. It integrates one selectable Boost/Buck DC/DC converter, one high efficiency step-down DC/DC converter, one high efficiency main step-up converter, one PWM converter for CCD positive voltage, one inverter for CCD negative voltage and one white LED driver for LCD backlight. The RT9911 is targeted for applications that use either two or three primary cells or a single lithium-ion battery.

RT9911 is available in VQFN-40L 6x6. Each DC-DC converter has independent shutdown input.

### Ordering Information

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Applications**

- Digital Still Camera

- PDA

- Protable Device

#### **Features**

- 1.6V to 5.5V Battery Input Voltage Range

- Synchronous Boost/Buck Selectable DC/DC Converter

- Internal Switches

- → Up to 95% Efficiency

- Syn-Buck DC/DC Converters

- → 0.8V to 5.5V Adjustable Output Voltage

- → Up to 95% Efficiency

- ▶ 100%<sub>(MAX)</sub> Duty Cycle

- Internal Switches

- Main Boost DC/DC Converter

- Adjustable Output Voltage

- Up to 97% Efficiency

- PWM Converter for CCD Positive Voltage

- Inverter for CCD Negative Voltage

- White LED Driver for LCD Panel Backlight

- Up to 1.4MHz Adjustable Switching Frequency

- 1µA Supply Current in Shutdown Mode

- External Compensation Network for all Converters

- Independent Enable Pin to Shutdown Each Channel.

- 40-Lead VQFN Package

- RoHS Compliant and 100% Lead (Pb)-Free

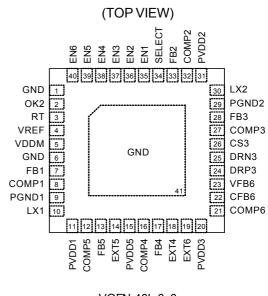

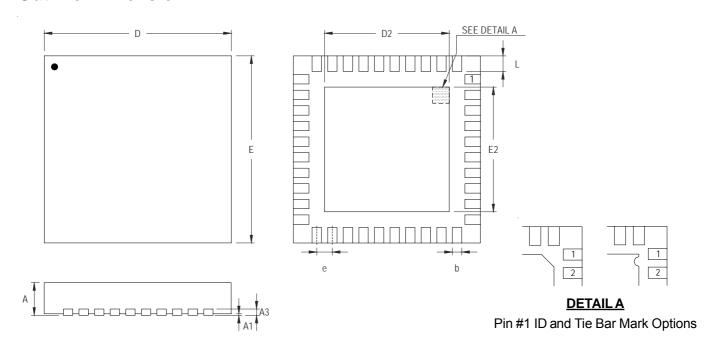

# **Pin Configurations**

VQFN-40L 6x6

## **Typical Application Circuit**

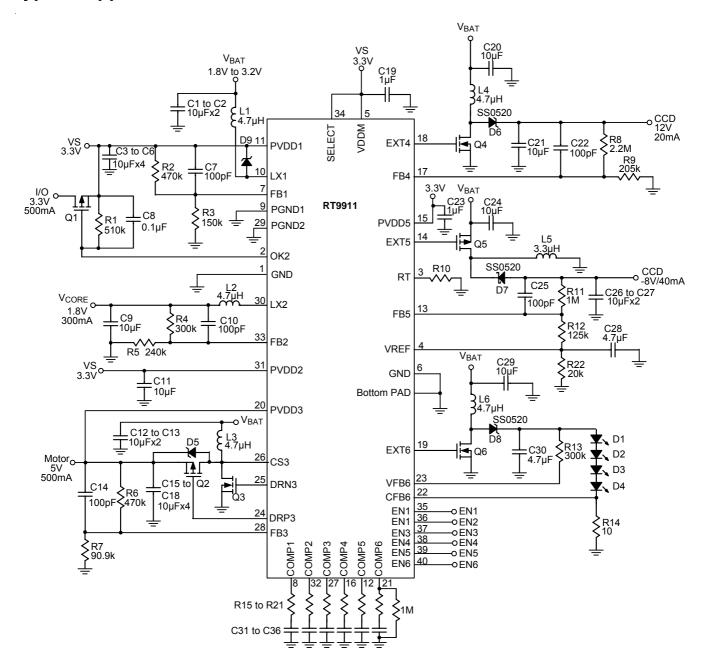

Figure 1. Application Circuit for 2-Cells Battery Supply

#### Note:

- Bottom pad is GND pad, can be short to pin 6 (GND).

- Please remove Q2 when use Async Boost and remove D5 when use Sync Boost.

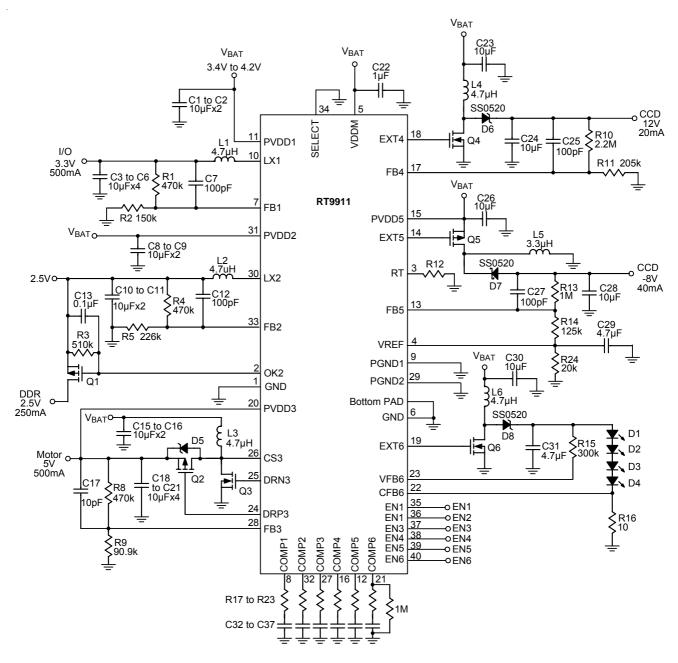

Figure 2. Application Circuit for Li-ion Battery Supply

#### Note:

- Bottom pad is GND pad, can be short to pin 6 (GND).

- Please remove Q2 when use Async Boost and remove D5 when use Sync Boost.

- · Output voltage setting

CH1: 0.8Vx(1+R1/R2) ex: I/O 3.3V = 0.8x(1+470k/150k)

CH2: 0.8Vx(1+R4/R5) ex: DDR 2.5V = 0.8x(1+470k/226k)

CH3: 0.8Vx(1+R8/R9) ex: MOTOR 5V = 0.8x(1+470k/90.9k)

CH4: 1.0Vx(1+R10/R11) ex: CCD 12V = 1.0x(1+2.2M/205k)

CH5: -1.0Vx(R13/R14) ex: CCD -8V = -1.0x(1M/125k)

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                        | I/O | Internal State at<br>Shut Down | I/O Configuration       |

|---------|----------|---------------------------------------------------------------------|-----|--------------------------------|-------------------------|

| 1       | GND      | Analog Ground Pin                                                   |     | _                              | OK2                     |

| 2       | OK2      | External Switch Control.                                            | OUT | High Impedance                 | GNDo                    |

| 3       | RT       | Frequency Setting Pin. Frequency is 500kHz if RT pin not connected. | OUT | Pull Low                       | VDDM•                   |

| 5       | VDDM     | Device Input Power Pin                                              | IN  | _                              |                         |

| 6       | GND      | Analog Ground Pin                                                   |     | -                              | GND RT                  |

| 4       | VREF     | 1.0V Reference Pin                                                  | OUT | High Impedance                 | 1.0V0 VREF              |

| 7       | FB1      | Feedback Input Pin of CH1.                                          | IN  | High Impedance                 | 0.8V 0 + COMP1          |

| 8       | COMP1    | Feedback Compensation Pin of CH1.                                   | OUT | Pull Low                       | FB10—                   |

| 9       | PGND1    | Power Ground Pin of CH1.                                            |     | -                              | PVDD1<br>►              |

| 10      | LX1      | Switch Node of CH1.                                                 | OUT | High Impedance                 | DLX1                    |

| 11      | PVDD1    | Power Input Pin of CH1.                                             | IN  | -                              | PGND1                   |

| 12      | COMP5    | Feedback Compensation Pin of CH5.                                   | OUT | Pull Low                       | FB50 + COMP5            |

| 13      | FB5      | Feedback Input Pin of CH5.                                          | IN  | High Impedance                 | <u> </u>                |

| 14      | EXT5     | External Power Switch of CH5.                                       | OUT | Pull High                      | PVDD5                   |

| 15      | PVDD5    | Power Input Pin of CH4, CH5 and CH6.                                | IN  | _                              | EXT5                    |

| 16      | COMP4    | Feedback Compensation Pin of CH4.                                   | OUT | Pull Low                       | 1.0V 0 + COMP4<br>FB4 0 |

| 17      | FB4      | Feedback Input Pin of CH4.                                          | IN  | High Impedance                 | ·                       |

To be continued

| Pin No. | Pin Name | Pin Function                            | I/O                                    | Internal State at<br>Shut Down | I/O Configuration                                |  |

|---------|----------|-----------------------------------------|----------------------------------------|--------------------------------|--------------------------------------------------|--|

| 18      | EXT4     | External Power Switch of CH4.           | OUT                                    | Pull Low                       | PVDD5  EXT4                                      |  |

| 19      | EXT6     | 6 External Power Switch of CH6.         |                                        | Pull Low                       | PVDD5  EXT6                                      |  |

| 20      | PVDD3    | Power Input Pin of CH3.                 | IN                                     |                                | PVDD3<br>Q                                       |  |

| 24      | DRP3     | External PMOS Switch Pin for CH3.       | OUT                                    | Pull High                      | DRP3                                             |  |

| 21      | COMP6    | COMP6 Feedback Compensation Pin of CH6. |                                        | Pull Low                       | 0.2Vo + COMP6                                    |  |

| 22      | CFB6     | Current Feedback Input Pin for CH6.     | edback Input Pin for IN High Impedance |                                | CFB6o—                                           |  |

| 23      | VFB6     | Voltage Feedback Input Pin for CH6.     | IN                                     | High Impedance                 | VFB6  1.0V ○ + + + + + + + + + + + + + + + + + + |  |

| 25      | DRN3     | External NMOS Switch Pin for CH3.       | OUT                                    | Pull Low                       | PVDD3  DRN3                                      |  |

| 26      | CS3      | Current Sense Input Pin for CH3         | IN                                     | High Impedance                 | VDDM<br>CS30                                     |  |

To be continued

| Pin No. | Pin Name | Pin Function                                                                 | I/O               | Internal State at<br>Shut Down | I/O Configuration        |

|---------|----------|------------------------------------------------------------------------------|-------------------|--------------------------------|--------------------------|

| 27      | COMP3    | Feedback Compensation Pin of CH3                                             | IOUI IPUILOW      |                                | 0.8V0 + COMP3<br>FB3 0 - |

| 28      | FB3      | Feedback Input Pin of CH3.                                                   | IN High Impedance |                                | •                        |

| 29      | PGND2    | Power Ground Pin of CH2                                                      |                   |                                | PVDD2<br>↓⊢              |

| 30      | LX2      | Switch Node of CH2                                                           | OUT               | High Impedance                 | LX2                      |

| 31      | PVDD2    | Power Input Pin of CH2.                                                      | IN                |                                | PGND2                    |

| 32      | COMP2    | Feedback Compensation Pin of CH2.                                            | OUT               | Pull Low                       | 0.8Vo + COMP2<br>FB2 o - |

| 33      | FB2      | Feedback Input Pin of CH2.                                                   | IN                | High Impedance                 |                          |

| 34      | SELECT   | CH1 Boost/Buck Selection Pin. Logic state can't be changed during operation. | IN                | Pull Low                       | SELECT 2uA               |

| 35      | EN1      | Enable Input Pin of CH1.                                                     | IN                | Pull Low                       | VDDM<br>EN1<br>2uA       |

| 36      | EN2      | Enable Input Pin of CH2.                                                     | IN                | Pull Low                       | VDDM  EN2  2uA           |

To be continued

| Pin No.             | Pin Name | Pin Function                                                                                        | I/O | Internal State at<br>Shut Down | I/O Configuration   |

|---------------------|----------|-----------------------------------------------------------------------------------------------------|-----|--------------------------------|---------------------|

| 37                  | EN3      | Enable Input Pin of CH3.                                                                            | IN  | Pull Low                       | VDDM<br>EN3<br>2uA  |

| 38                  | EN4      | Enable Input Pin of CH4.                                                                            | IN  | Pull Low                       | VDDM<br>EN4<br>2uA  |

| 39                  | EN5      | Enable Input Pin of CH5.                                                                            | IN  | Pull Low                       | VDDM<br>EN5<br>2uA  |

| 40                  | EN6      | Enable Input Pin of CH6.                                                                            | IN  | Pull Low                       | VDDM<br>VDDM<br>EN6 |

| Exposed<br>Pad (41) | GND      | The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation. |     |                                |                     |

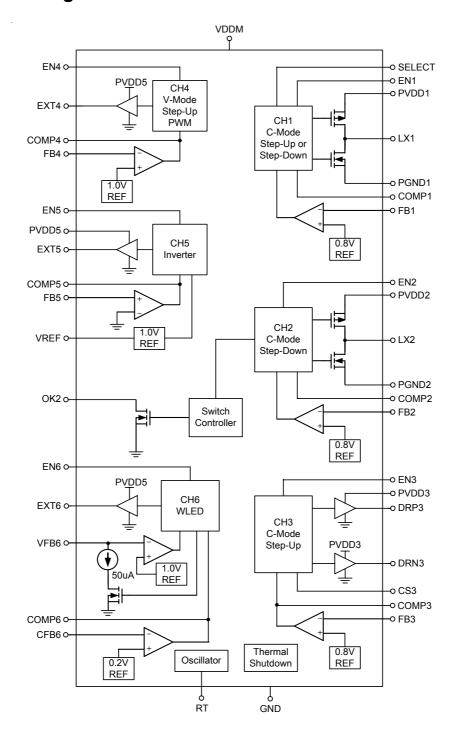

# **Function Block Diagram**

## Absolute Maximum Ratings (Note 1)

| Supply Voltage, V <sub>DDM</sub> Power Switch      The Other Pins      Power Discipation R- @ T. = 25°C                                        | 0.3V to (V <sub>DD</sub> + 0.3V) |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> <li>VQFN-40L 6x6</li> <li>Package Thermal Resistance (Note 2)</li> </ul> | 2.778W                           |

| VQFN-40L 6x6, θ <sub>JA</sub>                                                                                                                  | 36°C/W                           |

| Junction Temperature                                                                                                                           | 150°C                            |

| • Lead Temperature (Soldering, 10 sec.)                                                                                                        | 260°C                            |

| Storage Temperature Range                                                                                                                      | –65°C to 150°C                   |

| ESD Susceptibility (Note 3)                                                                                                                    |                                  |

| HBM (Human Body Mode)                                                                                                                          | 2kV                              |

| MM (Machine Mode)                                                                                                                              | 200V                             |

| Recommended Operating Conditions (Note 4)                                                                                                      |                                  |

| Dimming Control Frequency Range, CH6                                                                                                           | 300Hz to 900Hz                   |

| Supply Voltage, V <sub>DDM</sub>                                                                                                               | 2.4V to 5.5V                     |

# **Electrical Characteristics**

$(V_{DDM} = 3.3V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                                             | Symbol           | Test Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------------------------|------------------|-------------------------------------------|-----|-----|-----|------|

| Supply Voltage                                        |                  |                                           |     |     |     |      |

| VDDM Minimum Startup Voltage                          | V <sub>ST</sub>  | (Note 5)                                  |     |     | 1.6 | ٧    |

| VDDM Operating Voltage                                | $V_{DDM}$        | VDDM Pin Voltage                          | 2.4 |     | 5.5 | V    |

| VDDM Over Voltage Protection                          |                  |                                           | 5.9 | 6.5 |     | V    |

| Supply Current                                        |                  |                                           |     |     |     |      |

| Shutdown Supply Current into VDDM                     | I <sub>OFF</sub> | EN1 = EN2 = EN3 = EN4 = EN5<br>= EN6 = 0V |     | 1   | 10  | μΑ   |

| CH1 (Sync-Boost or Syn-Buck) Supply Current into VDDM | I <sub>Q1</sub>  | V <sub>DDM</sub> = 3.3V, Non-Switching    | -   |     | 430 | μА   |

| CH2 (Sync-Buck) Supply Current into VDDM              | I <sub>Q2</sub>  | V <sub>DDM</sub> = 3.3V, Non-Switching    | -   |     | 350 | μА   |

| CH3 (Sync-Boost) Supply Current into VDDM             | I <sub>Q3</sub>  | V <sub>DDM</sub> = 3.3V, Non-Switching    | -   |     | 350 | μА   |

| CH4 (Asyn-Boost) Supply Current into VDDM             | I <sub>Q4</sub>  | V <sub>DDM</sub> = 3.3V, Non-Switching    |     |     | 300 | μΑ   |

| CH5 (Asyn-Inverter) Supply Current into VDDM          | $I_{Q5}$         | V <sub>DDM</sub> = 3.3V, Non-Switching    |     |     | 300 | μΑ   |

| CH6 (Asyn-Boost) Supply Current into VDDM             | I <sub>Q6</sub>  | V <sub>DDM</sub> = 3.3V, Non-Switching    |     |     | 350 | μА   |

To be continued

| Parameter                             | Symbol                 | Test Conditions                                    | Min   | Тур | Max   | Unit      |

|---------------------------------------|------------------------|----------------------------------------------------|-------|-----|-------|-----------|

| Oscillator                            |                        |                                                    |       |     |       |           |

| Operation Frequency                   | fosc                   | RT Open                                            | 450   | 550 | 650   | kHz       |

| CH1 Maximum Duty Cycle (Boost)        | D <sub>MAX1</sub>      | SELECT = 3.3V, V <sub>FB1</sub> = 0.7V             | 80    | 85  | 90    | %         |

| CH1 Maximum Duty Cycle (Buck)         | D <sub>MAX1</sub>      | SELECT = 0V, V <sub>FB1</sub> = 0.7V               | 100   |     |       | %         |

| CH2 Maximum Duty Cycle                | D <sub>MAX2</sub>      | V <sub>FB2</sub> = 0.7V                            | 100   |     |       | %         |

| CH3 Maximum Duty Cycle                | D <sub>MAX3</sub>      | V <sub>FB3</sub> = 0.7V                            | 75    | 80  | 90    | %         |

| CH4 Maximum Duty Cycle                | D <sub>MAX4</sub>      | V <sub>FB4</sub> = 0.9V                            |       |     |       |           |

| CH5 Maximum Duty Cycle                | D <sub>MAX5</sub>      | V <sub>FB5</sub> = 0.1V                            | 90    | 94  | 98    | %         |

| CH6 Maximum Duty Cycle                | D <sub>MAX6</sub>      | V <sub>CFB6</sub> = 0.18V, V <sub>FB6</sub> = 0.9V |       |     |       |           |

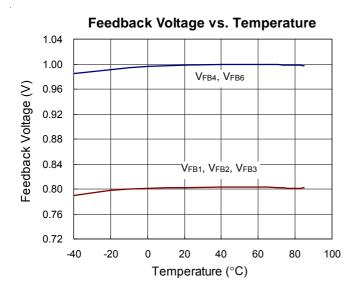

| Feedback Regulation Voltage           |                        |                                                    |       |     |       |           |

| Feedback Regulation Voltage @ FB1,    | \/                     |                                                    | 0.788 | 0.8 | 0.812 | V         |

| FB2, FB3                              | V <sub>FB1, 2,3</sub>  |                                                    | 0.766 | 0.0 | 0.612 | V         |

| Feedback Regulation Voltage @FB4      | $V_{FB4}$              |                                                    | 0.98  | 1   | 1.02  | V         |

| Feedback Regulation Voltage @ FB5     | V <sub>FB5</sub>       |                                                    | -15   |     | +15   | mV        |

| Feedback Regulation Voltage @ VFB6    | V <sub>VFB6</sub>      |                                                    |       | 1   |       | V         |

| Feedback Regulation Voltage @ CFB6    | V <sub>CFB6</sub>      |                                                    | 0.18  | 0.2 | 0.22  | <b>V</b>  |

| Reference                             |                        |                                                    |       |     |       |           |

| VREF Output Voltage                   | $V_{REF}$              |                                                    | 0.984 | 1   | 1.016 | ٧         |

| VREF Load Regulation                  |                        | 0μA < I <sub>REF</sub> < 100μA                     |       |     | 10    | mV        |

| Error Amplifier                       |                        |                                                    |       |     |       |           |

| GM (CH1, CH2, CH3, CH4, CH5, CH6)     |                        |                                                    |       | 0.2 |       | ms        |

| Compensation Source Current (CH1,     |                        |                                                    |       | 22  |       | ^         |

| CH2, CH3, CH4, CH5, CH6)              |                        |                                                    |       | 22  |       | μΑ        |

| Compensation Sink Current (CH1, CH2,  |                        |                                                    |       | 22  |       | μΑ        |

| CH3, CH4, CH5, CH6)                   |                        |                                                    |       |     |       | μΛ        |

| Power Switch                          |                        |                                                    |       |     |       |           |

| OUL O D III MAGGET                    | R <sub>DS(ON)P1</sub>  | P-MOSFET, PV <sub>DD1</sub> = 3.3V                 |       | 200 | 300   | $m\Omega$ |

| CH1 On Resistance of MOSFET           | R <sub>DS(ON)N1</sub>  | N-MOSFET, PV <sub>DD1</sub> = 3.3V                 |       | 200 | 300   | mΩ        |

| CH1 Switch Current Limitation (Buck)  | ,                      | SELECT=0                                           | 1.3   | 2   | 4     | Α         |

| CH1 Switch Current Limitation (Boost) |                        | SELECT=1                                           | 2     | 2.5 | 4     | Α         |

|                                       | R <sub>DS(ON)P2</sub>  | P-MOSFET, PV <sub>DD2</sub> = 3.3V                 |       | 300 | 450   | mΩ        |

| CH2 On Resistance of MOSFET           | RDS(ON)N2              | N-MOSFET, PV <sub>DD2</sub> = 3.3V                 |       | 300 | 450   | mΩ        |

| CH2 Switch Current Limitation         |                        |                                                    | 1.3   | 2   | 4     | Α         |

|                                       | R <sub>DS(ON)NP3</sub> | P-MOSFET, PV <sub>DD3</sub> = 3.3V                 |       | 6   | 15    | Ω         |

| CH3 On Resistance of DRN3             | 1                      | N-MOSFET, PV <sub>DD3</sub> = 3.3V                 |       | 6   | 15    | Ω         |

|                                       | -(-,-                  | P-MOSFET, PV <sub>DD3</sub> = 3.3V                 |       | 6   | 15    | Ω         |

| CH3 On Resistance of DRP3             | R <sub>DS(ON)PN3</sub> | N-MOSFET, PV <sub>DD3</sub> = 3.3V                 |       | 6   | 15    | Ω         |

|                                       | R <sub>DS(ON)P4</sub>  | P-MOSFET, PV <sub>DD3</sub> = 3.3V                 |       | 6   | 15    | Ω         |

| CH4 On Resistance of MOSFET           | ` ′                    | N-MOSFET, PV <sub>DD3</sub> = 3.3V                 |       | 6   | 15    | Ω         |

To be continued

| Parameter                                                  | Symbol                | Test Conditions                    | Min | Тур | Max | Unit |  |  |

|------------------------------------------------------------|-----------------------|------------------------------------|-----|-----|-----|------|--|--|

| Power Switch                                               | Power Switch          |                                    |     |     |     |      |  |  |

|                                                            | RDS(ON)P5             | P-MOSFET, PV <sub>DD5</sub> = 3.3V |     | 6   | 15  | Ω    |  |  |

| CH5 On Resistance of MOSFET                                | R <sub>DS(ON)N5</sub> | N-MOSFET, PV <sub>DD5</sub> = 3.3V |     | 6   | 15  | Ω    |  |  |

| 0100 0 0 11                                                | R <sub>DS(ON)P6</sub> | P-MOSFET, PV <sub>DD5</sub> = 3.3V |     | 6   | 15  | Ω    |  |  |

| CH6 On Resistance of MOSFET                                | R <sub>DS(ON)N6</sub> | N-MOSFET, PV <sub>DD5</sub> = 3.3V |     | 6   | 15  | Ω    |  |  |

| Switch Controller                                          | •                     |                                    | •   |     |     |      |  |  |

| OK2 pin Sink Current                                       |                       | OK2 = 1V                           | 90  |     |     | μА   |  |  |

| External Current Setting (CH3)                             |                       |                                    |     |     |     |      |  |  |

| CS3 Sourcing Current                                       | I <sub>CS3</sub>      |                                    | 5   | 10  | 15  | μА   |  |  |

| VFB6 Sink Current                                          | I <sub>VFB6</sub>     |                                    | 40  | 50  | 60  | μΑ   |  |  |

| Protection                                                 |                       |                                    |     |     |     |      |  |  |

| Under Voltage Protection Threshold                         |                       | SELECT = 0V                        | 0.3 | 0.4 | 0.5 | V    |  |  |

| Voltage @ FB1, FB2                                         | SELECT - 0V           |                                    | 0.5 | 0.4 | 0.5 | V    |  |  |

| Over Voltage Protection @ FB1, FB2                         |                       | SELECT = 0V                        |     | 1   |     | V    |  |  |

| Control                                                    |                       |                                    |     |     |     |      |  |  |

| EN1, EN2, EN3, EN4, EN5, EN6 Input<br>High Level Threshold |                       | V <sub>DDM</sub> = 3.3V            |     |     | 1.3 | V    |  |  |

| EN1, EN2, EN3, EN4, EN5, EN6 Input<br>Low Level Threshold  |                       | V <sub>DDM</sub> = 3.3V            | 0.4 |     |     | V    |  |  |

| EN1, EN2, EN3, EN4, EN5, EN6 Sink<br>Current               |                       | V <sub>DDM</sub> = 3.3V            |     | 2   | 6   | μА   |  |  |

| Select Pin Input High Level Threshold                      |                       |                                    |     |     | 1.3 | V    |  |  |

| Select Pin Input Low Level Threshold                       |                       |                                    | 0.4 |     |     | V    |  |  |

| Select Pin Sink Current                                    | I <sub>SELECT</sub>   |                                    |     | 2   | 6   | μΑ   |  |  |

| Thermal Protection                                         |                       |                                    |     |     |     |      |  |  |

| Thermal Shutdown                                           | $T_{SD}$              |                                    | 125 | 180 |     | °C   |  |  |

| Thermal Shutdown Hysteresis                                | $\DeltaT_{SD}$        |                                    |     | 20  |     | °C   |  |  |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A$  = 25°C on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. A Schottky retifier connected from LX1 to PVDD1 is required for low-voltage startup, refer to Figure 1.

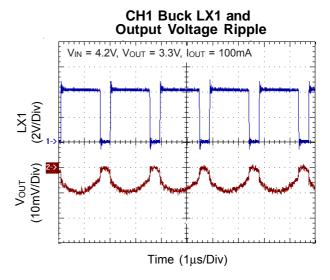

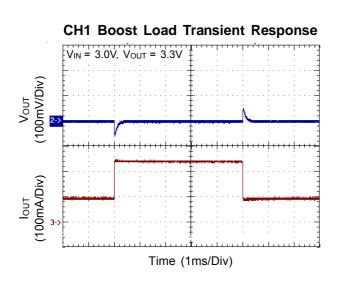

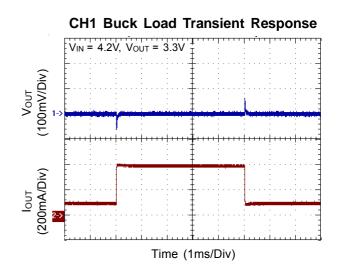

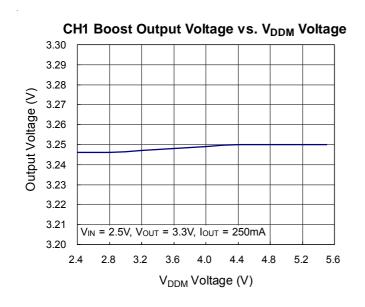

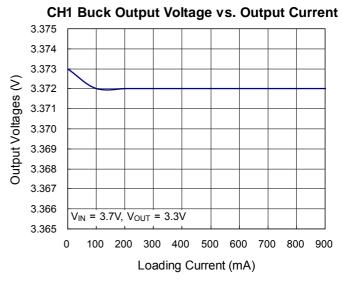

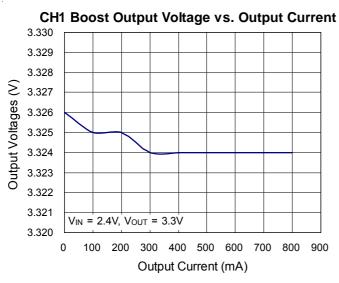

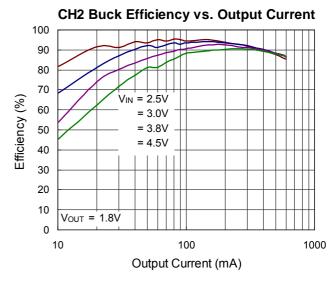

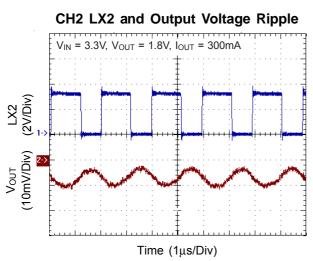

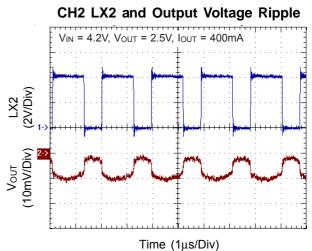

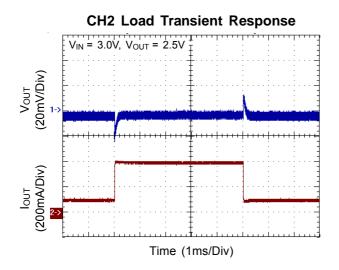

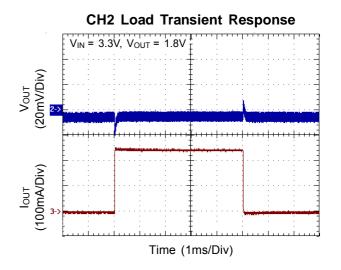

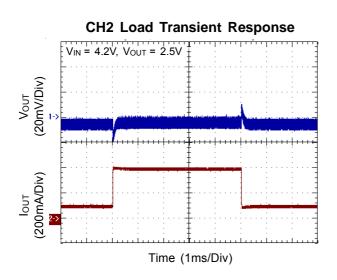

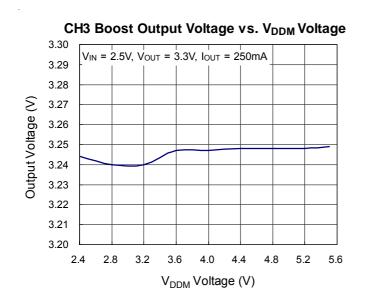

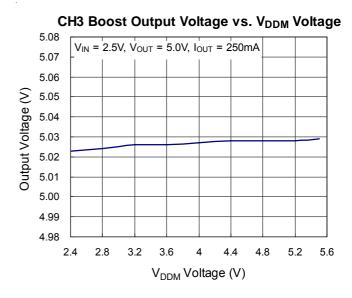

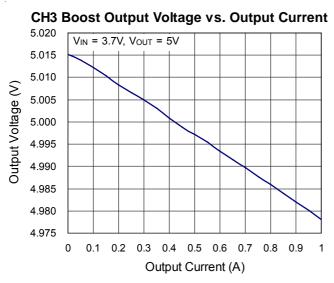

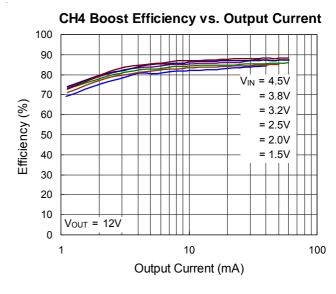

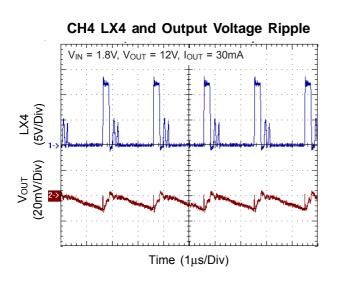

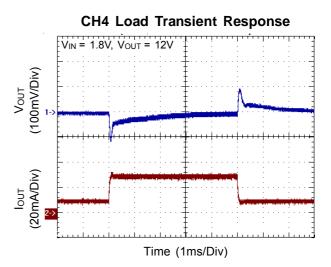

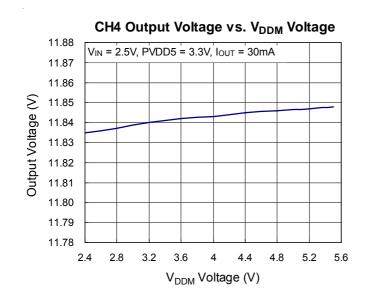

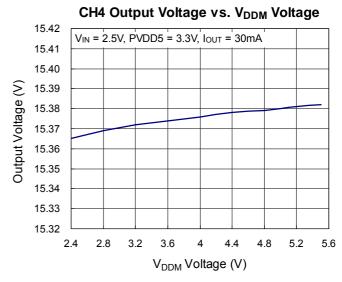

# **Typical Operating Characteristics**

13

www.richtek.com DS9911-05 April 2011

17

### **Applications Information**

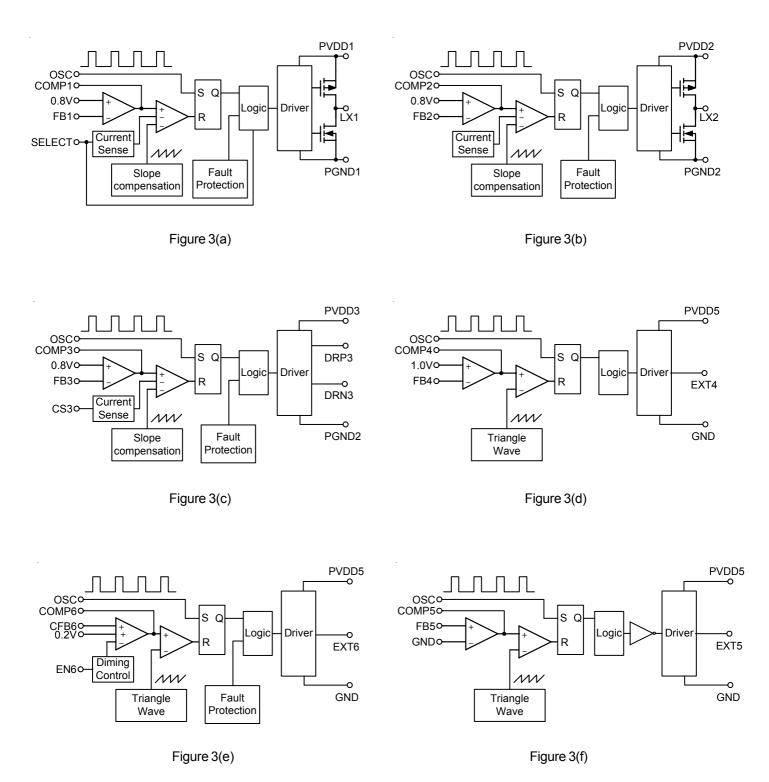

The RT9911 includes the following six DC/DC converter channels to build a multiple-output power-supply system.

**CH1**: Selectable step-up or step-down synchronous current mode DC/DC converter with internal power MOSFETs.

**CH2**: Step-down synchronous current mode DC/DC converter with internal power MOSFETs.

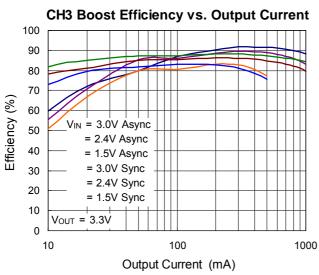

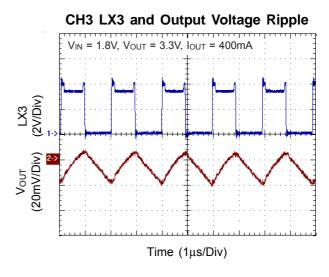

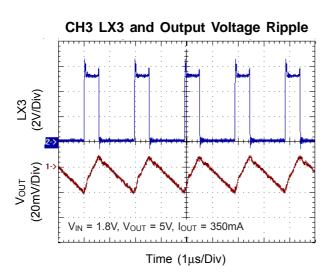

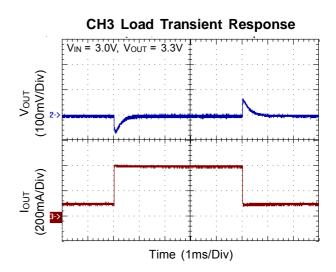

**CH3**: Step-up asynchronous current mode DC/DC controller to drive external power MOSFETs.

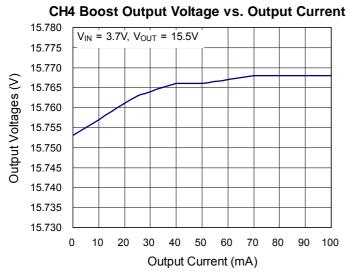

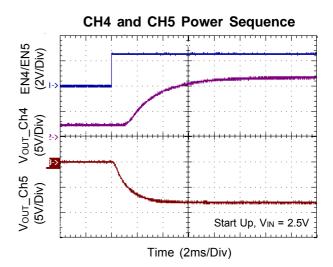

**CH4**: Step-up asynchronous voltage mode DC/DC controller.

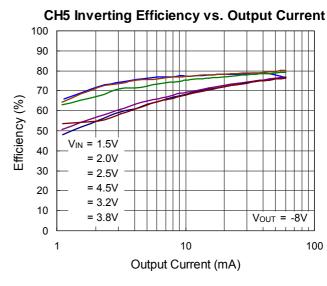

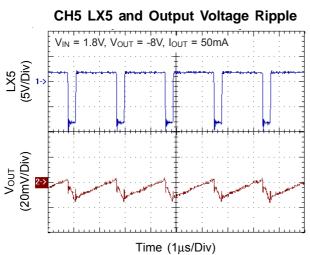

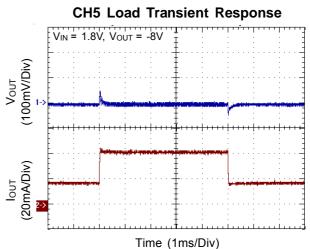

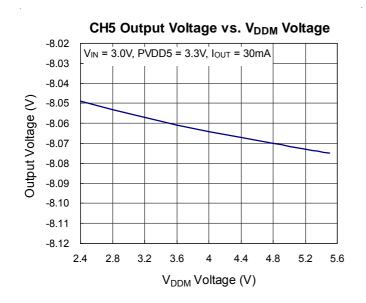

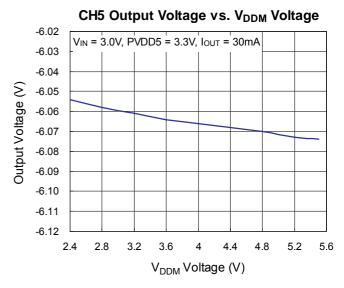

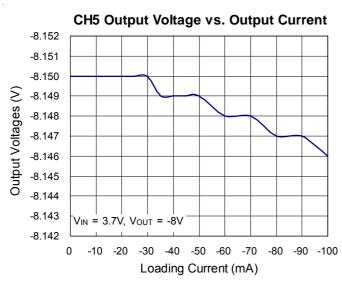

**CH5**: Inverting DC/DC voltage mode controller.

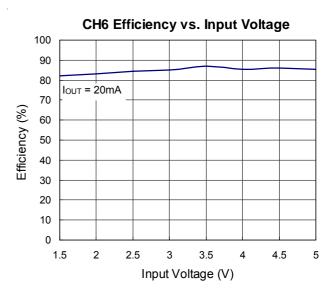

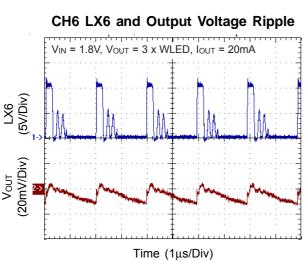

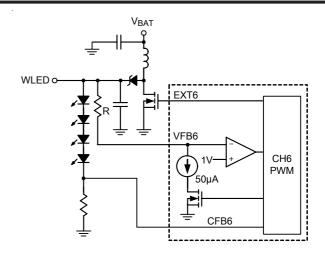

**CH6**: DC/DC voltage mode controller for WLED as well as conventional boost application; provides open LED OVP protection.

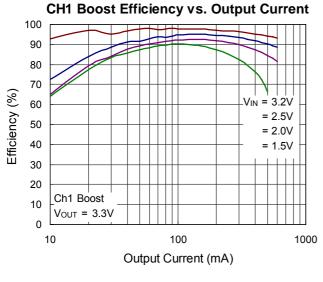

#### CH1: Selectable Step-up or Step-down Converter

CH1 is selectable as step-up (SELECT pin = logic high) or step-down (SELECT pin = logic low).

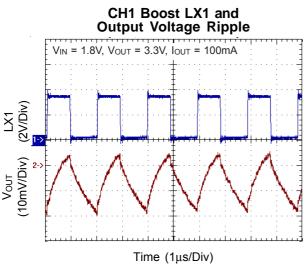

Step-up: With internal MOSFETs and synchronous rectifier, the efficiency is up to 95%. The converter always operates at fixed frequency PWM mode and CCM (continuous current mode).

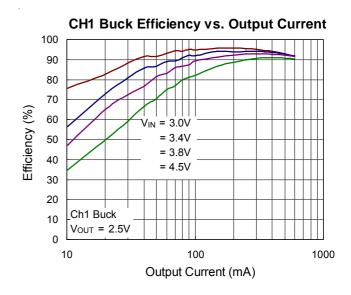

Step-down: With internal MOSFETs and synchronous rectifier, the efficiency is up to 95%. The converter always operates at fixed frequency PWM mode and CCM. While the input voltage is close to output voltage, the converter enters low dropout mode. Duty could be as long as 100% to extend battery life. See Figure 3(a) for detailed functional block.

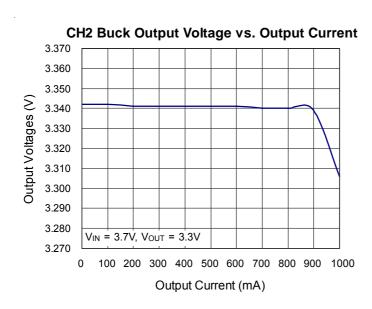

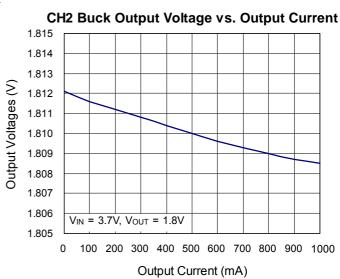

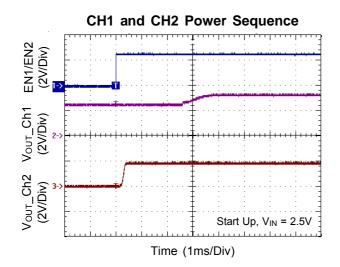

#### CH2: Step-down DC/DC Converter

With internal MOSFETs and synchronous rectifier, the efficiency is up to 95%. The converter always operates at fixed frequency PWM mode and CCM. While the input voltage is close to output voltage, the converter enters low dropout mode. Duty could be as long as 100% to extend battery life. See Figure 3(b) for detailed functional block.

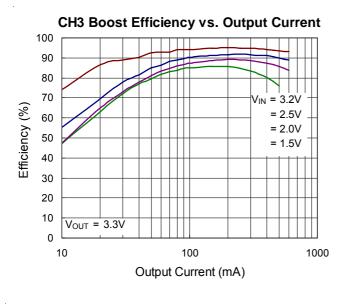

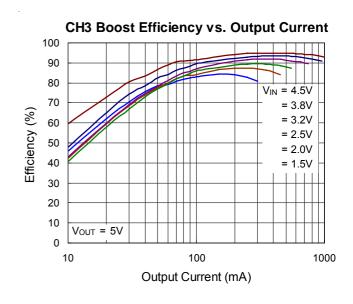

#### CH3: Step-up DC/DC Controller

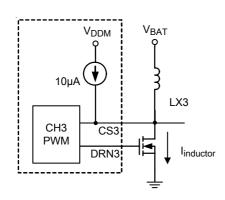

With external MOSFETs and a synchronous rectifier, the efficiency is up to 97%. The converter always operates at fixed frequency PWM mode and CCM. The threshold of current limit is estimated by  $R_{DS(ON)}$  of external NMOS. See **Protections** for detailed information and detailed functional block in Figure 3(c).

#### CH4, CH6: Step-up DC/DC Controller

CH4 and CH6 are fixed frequency voltage mode PWM controllers. EXT4 and EXT6 pins are designed to drive external NMOS switch. CH6 is optimized for WLED application. CFB6 is current-sensing feedback, and VFB6 provides over voltage protection (WLED open circuit). See **Protections** for detailed information and detailed functional block in Figure 3(d for CH4 and e for CH6).

#### **CH5: Inverting Controller**

CH5 is a voltage mode, fixed frequency PWM controller to generate negative output voltage. EXT5 is designed to drive external PMOS switch. To turn off PMOS completely, please note that PVDD5 should not be lower than the source voltage of PMOS. See Figure 3(f) for detailed functional block.

#### Reference Voltage

RT9911 provides a precise 1V reference voltage with souring capability 100 $\mu$ A. Connect a 1 $\mu$ F ceramic capacitor from VREF pin to GND. Reference voltage is enabled by connecting EN5 to logic high.

Figure 3. Detailed Functional Block for each channel

#### Note:

- Please refer to Figure 1 for application Information.

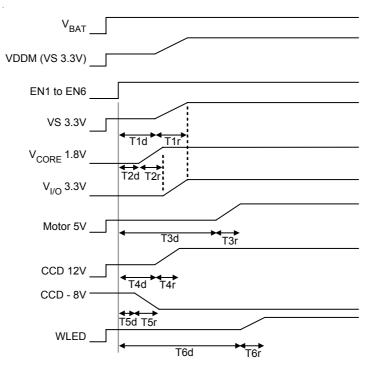

- Timing sequence should be controlled by EN pins.

Figure 4. Timing Diagram

### Calculation method:

| Calculation method:                                                                 |                                                                                   |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Td1 to Td6 are precise value. Tr1 to Tr6 are approximation.                         | $T3r = (0.5V \times D3 + 0.8A \times R_{DS(ON)_N} \times C33 / 3.6\mu A @ No$     |

| Units : T in second, C in Farad, R in Ohm                                           | load                                                                              |

| C31 to C36: Compensation capacitor of CH1 to CH6.                                   | T4r = (1.0V x D4) x C34 / 1μA @ No load                                           |

| T1d = 0.7V x C31 / 2μA (CH1 Boost)                                                  | T5r = $(1.0V \times D5) \times C35 / 1\mu A @ 1mA min. load$                      |

| T1d = $0.7V \times C31 / 2\mu A$ (CH1 Buck)                                         | T6r = (0.25V x D6) x C36 / 2.6μA @ 4 WLEDs                                        |

| T2d = 0.35V x C32 / 2μA                                                             | where                                                                             |

| $T3d = 0.7V \times C33 / 2\mu A$                                                    | $D1 = 1 - (V_{BAT} / V_{VS 3.3V})$ (Boost)                                        |

| T4d = 0.35V x C34 / 2μA                                                             | $D1 = V_{VS 3.3V} / V_{BAT} \qquad (Buck)$                                        |

| T5d = 0.85V x C35 / 2μA                                                             | $D2 = V_{VCORE\ 1.8V} / V_{BAT}$                                                  |

| T6d = 0.85V x C36 / 2μA                                                             | $D3 = 1 - (V_{BAT} / V_{Motor 5V})$                                               |

| T1r = (0.5V x D1 + 0.48A x R <sub>DS(ON) N</sub> x C31 /1.25μA @ No                 | $D4 = 1 - (V_{BAT} / V_{CCD 12V})$                                                |

| load (Boost)                                                                        | $D5 =  V_{CCD-8V}  / (V_{BAT} +  V_{CCD-8V} )$                                    |

| $T1r = (0.33V \times D1 + 0.2A \times R_{DS(ON)_P} \times C31 / 1.25\mu A @ No$     | $D6 = 1 - (V_{BAT} / V_{WLED})$                                                   |

| load (Buck)                                                                         | Example : T1d = 0.7V x 1nF / 2μA = 350μs (Boost)                                  |

| $T2r = (0.33V \times D2 + 0.2A \times R_{DS(ON)_P} \times C32/1.25\mu A @ No $ load | T1r = $(0.5 \times (1-1.8/3.3) + 0.48 \times 0.2) \times 1nF / 1.25\mu A = 258us$ |

258µs

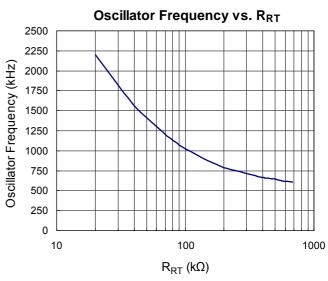

#### Oscillator

The internal oscillator synchronizes CH1 to CH6 with fixed operation frequency. The frequency could be set by connecting resistor between RT pin to GND. See Figure 5 to adjust frequency.

#### **Soft Start**

With internal soft start mechanism, the soft start time of each channel is proportional to the compensation capacitor. Refer to the soft start waveform in Figure 4 for typical application.

#### **Protection**

RT9911 provides versatile protection functions. Protection type, threshold and protection methods are summarized in Table 1.

Figure 5. Adjust Frequency

Table 1

|               | Protection type             | Threshold (typical) Refer to Electrical spec | Protection methods                             | Reset method                        |

|---------------|-----------------------------|----------------------------------------------|------------------------------------------------|-------------------------------------|

| VDDM          | Over Voltage<br>Protection  | VDDM > 6.5V                                  | Disable all channels                           | Restart if VDDM < 6.5V              |

| CH1:<br>Boost | Current Limit               | NMOS current> 2.5A                           | NMOS latched off                               | Automatic reset at next clock cycle |

|               | Current Limit               | PMOS current > 2.0A                          | PMOS latched off and all channels shutdown     | VDDM power reset                    |

| CH1:<br>Buck  | Under Voltage<br>Protection | FB1 < 0.4V                                   | NMOS, PMOS latch off and all channels shutdown | VDDM power reset                    |

|               | Over Voltage<br>Protection  | FB1 > 1.0V                                   | NMOS, PMOS latch off and all channels shutdown | VDDM power reset                    |

|               | Current Limit               | PMOS current > 2.0A                          | PMOS latched off and all channels shutdown     | VDDM power reset                    |

| CH2           | Under Voltage<br>Protection | FB2 < 0.4V                                   | NMOS, PMOS latch off and all channels shutdown | VDDM power reset                    |

|               | Over Voltage<br>Protection  | FB2 > 1.0V                                   | NMOS, PMOS latch off and all channels shutdown | VDDM power reset                    |

| СНЗ           | Current Limit               | CS3 > 0.3V, see below<br>Note                | NMOS latched off                               | Automatic reset at next clock cycle |

| СН6           | Over Voltage<br>Protection  | VFB6 > 1.0V, see<br>Figure 8                 | NMOS off                                       | VFB6 < 1.0V                         |

| Thermal       | Thermal shutdown            | Temperature > 180°C                          | All channels stop switching                    | Temperature < 160°C                 |

**Note :** If  $R_{DS(ON)} x$   $I_{inductor} > 0.3V$ , then current limit happens.

For example, if select NMOS( AOS3402),  $R_{DS(ON)}$  =110m $\Omega$  (at  $V_{GS}$  = 2.5V), then current limt happens if  $I_{inductor}$  > 2.73A.

Figure 6. CH3 Current Limit Setting

#### RT9911 Component Selection for Compensation:

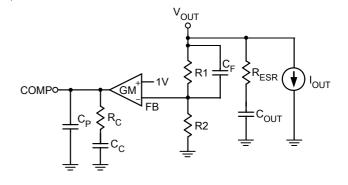

#### CH1 Sync-Boost (Select Pin = High Logic):

CH1 sync-boost converter employs current-mode control to simplify the control loop compensation. There is a RHPZ (Right Hand Plane Zero) appeared in the loop-gain frequency response when a boost converter operates with continuous inductor current (typically the case), we also call it works in CCM (Continuous Current Mode). For stability, cross over frequency ( $f_C$ ), unity gain frequency, must lower than this RHPZ frequency.

The fixed parameters for CH1 boost compensation are as follows:

- Transconductance (from FB to COMP), GM = 200μs

- Current sense transresistance, R<sub>CS</sub> = 0.4V/A

- Feedback voltage, V<sub>FB</sub> = FB = 0.8V

Figure 7

Figure 8. CH6 Over Voltage Protection Method  $(V_{WLED} > 50\mu A \times R+1V, protection happens)$

The input parameters for CH1 boost compensation are as follows:

- $\bullet$  R1, the voltage divider resistor in between  $V_{\text{OUT}}$  and  $\ensuremath{\mathsf{FB}}$

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- F<sub>OSC</sub>, operating frequency

- . L, inductance

- R<sub>ESR</sub>, ESR (Equivalent Series Resistance) of C<sub>OUT</sub> (ceramic output capacitor)

- T<sub>DRP</sub>(%), Transient droop.

The results we will get for CH1 boost compensation are as follows:

- R2, the voltage divider resistor in between FB and ground.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with Rc and connect to ground.

- C<sub>P</sub>, connect in between COMP pin and ground. (Can be ignored if C<sub>P</sub> < 10pF).</li>

- C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

The major steps for getting above results:

1.

$$R2 = R1x \left( \frac{V_{FB}}{(V_{OUT} - V_{FB})} \right)$$

2. Find RHPZ(Right Hand Plan Zero) location.

RHPZ(Boost) = RLOAD x

$$\frac{(1-D)^2}{2\pi L}$$

, Where

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX.)}}, D = Duty Cycle = 1 - \frac{V_{IN}}{V_{OUT}}$$

3. Set f<sub>C</sub> (cross over frequency) sufficiently below RHPZ.

For example:  $f_C = RHPZ/6$

4. Get

$$Cc = \left(\frac{R_{LOAD}}{R_{CS}}\right) \times \frac{GM}{2\pi fc} \times \frac{V_{FB}}{V_{OUT}} \times (1 - D)$$

5. Select Rc based on the allowed transient droop.

$$R_C = dI \times (\frac{1}{(1-D)}) \times \frac{R_{CS}}{GM \times dV_{FB}}$$

6. Get Cout =

$$\frac{\text{Rc x Cc}}{\text{RLOAD}}$$

7. Find ffz, zero and ffp, pole ratio of voltage divider with

$$C_{F.}$$

ratio =  $\frac{\text{ffz}}{\text{ffp}} = \frac{V_{OUT}}{V_{FB}}$

- 8. Get  $C_F$  by placing ffp on  $f_C$  and ffz therefore on  $\frac{f_C}{ratio}$ .  $C_f = \frac{1}{2 \times \pi \times ffz \times R1}, \text{ where } ffz = \frac{f_C}{ratio}$

- 9. Evaluate C<sub>P</sub>. C<sub>P</sub> is for canceling the zero from C<sub>OUT</sub> (ceramic output capacitor).

$$CP = COUT \frac{RESR}{Rc}$$

.  $CP$  can be ignore if  $CP < 10pF$ .

Example : Set R1 =  $470k\Omega$ ,  $V_{IN}$  = 1.8V,  $V_{OUT}$  = 3.3V,

$V_{FB} = 0.8V$ ,  $I_{OUT(MAX.)} = 0.5A$ ,  $f_{OSC} = 500kHz$ ,  $L = 4.7\mu H$ ,

$R_{ESR} = 5m\Omega$ , and half-load transient droop is 5%.

1. R2 = R1

$$\frac{V_{FB}}{V_{OUT} - V_{FB}}$$

= 470k  $\frac{0.8}{3.3 - 0.8}$  = 150k $\Omega$

2. RHPZ(Boost) = RLOAD  $\frac{(1-D)^2}{2\pi L}$  = 66.3kHz, where

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX)}} = 6.6\Omega, (1-D) = \frac{V_{IN}}{V_{OUT}} = 0.54$$

3.

$$fc = \frac{RHPZ}{6} = 11kHz$$

4.

$$Cc = \frac{\frac{R_{LOAD}}{R_{CS}}GM}{2\pi f_C}x\left(\frac{V_{FB}}{V_{OUT}}\right)x(1-D) = 6.3nF.$$

Half-load transient means load from 0.25A to 0.5A transient. So, dI=0.5 - 0.25=0.25A

$$dV_{FB} = T_{DRP}(\%) \times V_{FB} = 5\% \times 0.8 = 0.04V.$$

$$5. Rc = \frac{dI\left(\frac{1}{(1-D)}\right) x Rcs}{GM x dV_{FB}} = 23k\Omega$$

6. Cout =

$$\frac{\text{Rc x Cc}}{\text{RLOAD}} = \frac{23\text{k x } 6.8\text{n}}{6.6} = 22\mu\text{F}$$

.

7. ratio =

$$\frac{\text{ffp}}{\text{ffz}} = \frac{\text{V}_{\text{OUT}}}{\text{V}_{\text{FB}}} = \frac{3.3}{0.8} = 4.1$$

8. C<sub>F</sub> =

$$\frac{1}{2\pi \times \text{ffz} \times \text{R1}}$$

= 126pF, where

ff<sub>Z</sub> =  $\frac{\text{fc}}{\text{ratio}}$  =  $\frac{11\text{k}}{4.1}$  = 2.68kHz

$$\label{eq:Choose CF} \begin{split} &\text{Choose C}_F = 150 \text{pF} \\ &\text{9. CP} = \frac{\text{COUT x RESR}}{\text{RC}} = \frac{22 \mu \text{F x 0.005}}{23 \text{k}} = 4.8 \text{pF} \,, \end{split}$$

which is less than 10pF. So. It can be ignored.

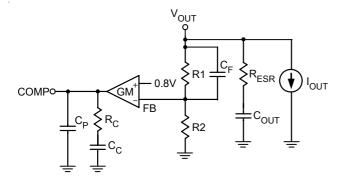

### CH1 Sync-Buck (Select Pin = Low Logic) and CH2 Sync-Buck:

CH1 sync-buck (select pin=low logic) and CH2 sync-buck are converters employ current-mode control to simplify the control loop compensation. There is no RHPZ (Right Hand Plan Zero) in the buck topology but there is a high frequency pole  $f_{HP}$  >=  $f_{OSC}$   $/\pi$  . The  $f_{C}$  (cross over frequency) is chosen sufficient less than f<sub>HP</sub>.

The fixed parameters for CH1 and CH2 buck compensation are as follows:

- Transconductance (from FB to COMP), GM = 200μs

- Current sense transresistance, R<sub>CS</sub> = 0.3V/A

- Feedback voltage, V<sub>FB</sub> = FB = 0.8V

The input parameters for CH1 and CH2 buck compensation are as follows:

R1, the voltage divider resistor in between V<sub>OUT</sub> and

# **RT9911**

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- f<sub>OSC</sub>, operating frequency

- . L, inductance

- R<sub>ESR</sub>, ESR (Equivalent Series Resistance) of C<sub>OUT</sub> (ceramic output capacitor)

- T<sub>DRP</sub>(%), Transient droop.

The results we will get for CH1 boost compensation are as follows:

- R2, the voltage divider resistor in between FB and ground.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with R<sub>C</sub> and connect to ground

- C<sub>P</sub>, connect in between COMP pin and ground. (Can be ignored if C<sub>P</sub> < 10pF)</li>

- C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

The major steps for getting above results:

1.

$$R2 = R1 \frac{V_{FB}}{V_{OUT} - V_{FB}}$$

2. Set fc (cross over frequency) sufficiently below f<sub>OSC</sub>.

For example :

$$fc = \frac{f_{HP}}{4}$$

3.

$$Cc = \frac{R_{LOAD}}{R_{CS}} \times \frac{GM}{2\pi f_C} \times \frac{V_{FB}}{V_{OUT}}$$

- 4.  $RC = \frac{dI \times RCS}{GM \times dV_{FB}}$ , where dI = transient step,  $dV_{FB} = T_{DRP}(\%) \times V_{FB}$

- 5. Get Cout =  $\frac{\text{Rc x Cc}}{\text{RLOAD}}$

- 6. Find ffz, zero and ffp, pole ratio of voltage divider with

$$C_F$$

.

ratio =  $\frac{ffp}{ffz} = \frac{V_{OUT}}{V_{FB}}$

7. Get  $C_F$  by placing ffp on  $f_C$  and ffz therefore on  $\frac{f_C}{ratio}$

$$C_F = \frac{1}{2\pi \times \text{ffz} \times \text{R1}}$$

, where  $\text{ffz} = \frac{\text{fc}}{\text{ratio}}$ .

8. Evaluate C<sub>P</sub>. C<sub>P</sub> is for canceling the zero from C<sub>OUT</sub> (ceramic output capacitor).

$$C_P = \frac{C_{OUT} \ x \ R_{ESR}}{R_C} \, . \, C_P \ can \ be \ ignore \ if \ C_P < 10 pF.$$

Example : Set R1 =  $470k\Omega$ ,  $V_{IN}$  = 3V,  $V_{OUT}$  = 1.8V,

$$V_{FB} = 0.8V$$

,  $I_{OUT(MAX.)} = 0.5A$ ,  $f_{OSC} = 500kHz$ ,  $L = 4.7\mu H$ ,

$R_{ESR}$  = 5m $\Omega$ , and half-load transient droop is 5%.

#### Results:

1. R2 = R1x

$$\frac{V_{FB}}{V_{OUT} - V_{FB}}$$

= 470k x  $\frac{0.8}{1.8 - 0.8}$  = 376k $\Omega$

2. fc =

$$\frac{\text{fHP}}{4} = \frac{\text{fosc}}{4\pi} = 40\text{kHz}$$

3.

$$C_C = \frac{R_{LOAD}}{R_{CS}} \times \frac{GM}{2\pi f_C} \times \frac{V_{FB}}{V_{OUT}} = 4.25 nF$$

, where

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX)}} = 3.6 \Omega$$

#### Choose 4.7nF.

Half-load transient means load from 0.25A to 0.5A transient. So, dI = 0.5 - 0.25 = 0.25A

$$dV_{FB} = T_{DRP}(\%) \times V_{FB} = 5\% \times 0.8 = 0.04V.$$

Thus,

4.

$$Rc = dI \frac{Rcs}{GM \ x \ dV_{FB}} = 9.4 k\Omega$$

, choose  $10 k\Omega$ .

5. Cout =

$$\frac{\text{Rc x Cc}}{\text{RLOAD}} = \frac{10\text{k x } 3.9\text{nF}}{3.6} = 10.8 \,\mu\text{F}$$

. Choose  $10\,\mu\text{F}$ .

6. ratio =

$$\frac{\text{ffp}}{\text{ffz}} = \frac{\text{Vout}}{\text{VFB}} = \frac{1.8}{0.8} = 2.25$$

7.

$$C_F = \frac{1}{2\pi \times ff_Z \times R1} = 15.2pF$$

, where

$ff_Z = \frac{f_C}{ratio} = \frac{50k}{2.25} = 22.2kHz$

Choose  $C_F = 22pF$

8.

$$CP = \frac{COUT \times RESR}{Rc} = \frac{10 \,\mu \times 0.005}{10 k} = 5pF$$

,

which is less than 10pF. So, It can be ignored.

### CH3 Syn Boost Controller with External MOSFET:

CH3 boost controller driving external logic level MOSFET employs current-mode control to simplify the control loop compensation. There is a RHPZ (Right Hand Plan Zero) appeared in the loop-gain frequency response when a boost converter operates with continuous inductor current (typically the case), we also call it works in CCM (Continuous Current Mode). For stability, cross over frequency (f<sub>C</sub>), unity gain frequency, must lower than this RHPZ frequency.

The fixed parameters for CH3 boost compensation are as follows:

- Transconductance (from FB to COMP), GM = 200μs

- Feedback voltage, V<sub>FB</sub> = FB = 0.8V

The input parameters for boost compensation are as follows:

- R<sub>DS(ON)</sub>, the NMOSFET R<sub>DS(ON)</sub>, which is use to find transresistance, R<sub>CS</sub>.

- R1, the voltage divider resistor in between V<sub>OUT</sub> and FB.

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- Fosc, operating frequency

- . L, inductance

- R<sub>ESR</sub>, ESR (Equivalent Series Resistance) of C<sub>OUT</sub> (ceramic output capacitor)

- T<sub>DRP</sub>(%), Transient droop.

The results we will get for boost compensation are as follows:

- R<sub>CS</sub>, the transresistance of current sense.

- R2, the voltage divider resistor in between FB and ground.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with R<sub>C</sub> and connect to ground

- $C_P$ , connect in between COMP pin and ground. (Can be ignored if  $C_P < 10pF$ )

C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

The major steps for getting above results:

1.  $R_{CS} = 2 \times R_{DS(ON)}$

The rest of the steps are the same as sync-boost.

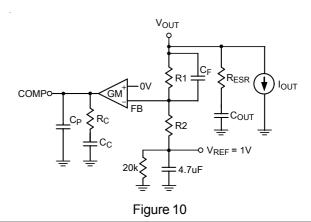

#### **CH4 Asyn-Boost Controller with External MOSFET**

CH4 is an asyn-boost controller driving external logic level N type MOSFET, which employs voltage mode control to regulate the output voltage. Compensation depends on designing the loading range working in discontinuous or continuous inductor current mode. (DCM or CCM).

### Asyn-Boost in DCM:

We call it DCM because inductor current falls to zero on each switch cycle. The benefit of designing in DCM is the simple loop compensation, which has no RHPZ (Right Hand Plan Zero) and conjugate double pole in the frequency domain to worry about, but has a single load pole instead. However, the output ripple and efficiency are worse than in CCM (Continuous Inductor Current). If the loading is around tens of mA, it is not bad to design in DCM with less impact on the output ripple and efficiency, but gain more easy to stabilize the control loop.

The fixed parameters for CH4 asyn-boost in DCM compensation are as follows:

- Transconductance (from FB to COMP), GM = 200us.

- Internal voltage ramp to decide duty cycle, V<sub>P</sub> = 1V.

- Feedback voltage, V<sub>FB</sub> = FB = 1V

Figure 9

# **RT9911**

RICHTEK

The input parameters for CH4 asyn-boost in DCM compensation are as follows :

- R1, the voltage divider resistor in between V<sub>OUT</sub> and FB.

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- fosc, operating frequency

- L. inductance

- C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

- R<sub>ESR</sub>, ESR (Equivalent Series Resistance) of C<sub>OUT</sub> (ceramic output capacitor)

The results we will get for CH4 asyn-boost in DCM compensation are as follows:

- R2, the voltage divider resistor in between FB and ground.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with R<sub>C</sub> and connect to ground

- C<sub>P</sub>, connect in between COMP pin and ground. (Can be ignored if C<sub>P</sub> < 10pF)</li>

The major steps for getting above results:

1.

$$R2 = R1x \frac{V_{FB}}{V_{OUT} - V_{FB}}$$

Select suitable inductor to ensure I<sub>OUT(MIN.)</sub> works in DCM, which is let inductor current falls to zero on each switch cycle.

$$L < \frac{V_{IN} \times D \times (1-D)}{2 \times I_{OUT(MAX.)} \times fosc}$$

3. Set f<sub>C</sub> sufficient below f<sub>OSC</sub>.

For example:

$$fc = \frac{fosc}{10}$$

or lower

4. Find the load pole:  $f_{LP} = \frac{2 \times M - 1}{2\pi \times (M - 1) \times R_{LOAD} \times C_{OUT}}$ ,

where

$$M = \frac{V_{OUT}}{V_{IN}}$$

,  $R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX.)}}$ .

5. Get Rc =

$$\frac{\frac{fc}{f_{LP}} \times V_P}{GM \times G_{dod}}$$

, where  $G_{dod} = 2 \times \frac{V_{OUT}}{D} \times \frac{M-1}{2 \times M-1}$ ,

which is duty to V<sub>OUT</sub> transfer function.

$$D = duty \ cycle = 1 - \frac{V_{IN}}{V_{OUT}}$$

6. Get  $Cc = Cout x \frac{RLOAD}{Rc}$

by letting comp zero = load pole.

7. Find ffz, zero and ffp, pole ratio of voltage divider with C<sub>F</sub>.

$$ratio = \frac{ffp}{ffz} = \frac{V_{OUT}}{V_{FB}}$$

8. Get  $C_F$  by placing ffp on  $f_C$  and ffz therefore on  $\frac{f_C}{ratio}$ .

$$C_F = \frac{1}{2\pi \times ff_Z \times R1}$$

, where  $ff_Z = \frac{f_C}{ratio}$ .

9. Evaluate C<sub>P</sub>. C<sub>P</sub> is for canceling the zero from C<sub>OUT</sub> (ceramic output capacitor).

$$C_P = C_{OUT} x \frac{R_{ESR}}{R_C}$$

.  $C_P$  can be ignore if  $C_P < 10pF$ .

#### Asyn-boost in CCM:

We call it CCM because inductor current is always continuous in operation. The benefit of designing in CCM is lower  $V_{\text{OUT}}$  and inductor current ripple and higher efficiency from the lower coil loss, but with the expense of larger inductor size and cost and the control loop comes with a RHPZ (Right Hand Plan Zero) and a conjugate double pole in the frequency domain to worry about.

The fixed parameters for CH4 asyn-boost in CCM compensation are as follows :

- Transconductance (from FB to COMP), GM = 200μs

- Internal voltage ramp to decide duty cycle, V<sub>P</sub> = 1V

- Feedback voltage, V<sub>FB</sub> = FB = 1V

The input parameters for CH4 asyn-boost in CCM compensation are as follows :

- R1, the voltage divider resistor in between V<sub>OUT</sub> and FB.

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- I<sub>OUT(MIN.)</sub>, minimum output laod

- f<sub>OSC</sub>, operating frequency

- L, inductance

- C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

- R<sub>ESR</sub>, ESR (Equivalent Series Resistance) of C<sub>OUT</sub> (ceramic output capacitor)

The results we will get for CH4 asyn-boost in CCM compensation are as follows:

- R2, the voltage divider resistor in between FB and ground.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with R<sub>C</sub> and connect to ground

- C<sub>P</sub>, connect in between COMP pin and ground. (Can be ignored if  $C_P < 10pF$ )

The major steps for getting above results:

1.

$$R2 = R1x \frac{V_{FB}}{V_{OUT} - V_{FB}}$$

2. Select suitable inductor to ensure I<sub>OUT(MIN.)</sub> works in

$$L > \frac{V_{\text{IN}} \times D \times (1-D)}{2 \times I_{\text{OUT}(\text{MIN.})} \times fosc}$$

3. Find RHPZ(Right Hand Plan Zero) location.

RHPZ(Boost) = RLOAD

$$\frac{(1-D)^2}{2\pi L}$$

, where

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX)}}, D = duty \ cycle = 1 - \frac{V_{IN}}{V_{OUT}}$$

4. Set f<sub>C</sub> (cross over frequency) sufficiently below RHPZ.

For example :

$$fc = \frac{RHPZ}{6}$$

or lower.

For example : fc =  $\frac{\text{RHPZ}}{6}$  or lower. 5. Find the load pole : fLP =  $\frac{2 \times \text{M} - 1}{2\pi \times (\text{M} - 1) \times \text{RLOAD} \times \text{COUT}}$ ,

where

$$M = \frac{V_{OUT}}{V_{IN}}$$

,  $R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX.)}}$  .

6. Get Rc =

$$\frac{\frac{fc}{f_{LP}} \times V_P}{GM \times G_{doc}}$$

, where  $G_{doc} = \frac{V_{IN}}{(1-D)^2}$ ,

which is duty to V<sub>OUT</sub> transfer function.

D = duty cycle =

$$1 - \frac{VIN}{VOLIT}$$

D = duty cycle = 1-

$$\frac{V_{\text{IN}}}{V_{\text{OUT}}}$$

.

7. Find fcdp =  $\frac{1-D}{2\pi \times (LC)^2}$ ,

which is the conjugate double pole from LC filter.

8.

$$Cc = \frac{1}{2\pi x \text{ fcdp } x \text{ Rc}}$$

to cancel one of the double pole.

9. Find C<sub>f</sub> by placing its zero on f<sub>cdp</sub> to cancel another double pole.

$$C_F = \frac{1}{2\pi \times f_{cdp} \times R1}.$$

10.Evaluate C<sub>P</sub>. C<sub>P</sub> is for canceling the zero from C<sub>OUT</sub> (ceramic output capacitor).

$$C_P = C_{OUT} \times \frac{R_{ESR}}{R_C}$$

.  $C_P$  can be ignore if  $C_P < 10pF$ .

#### CH5 Asyn-Inverter Controller with External MOSFET

CH5 is an asyn-inverter controller driving external logic level P type MOSFET, which employs voltage mode control to regulate the output voltage. Compensation depends on designing the loading range working in discontinuous or continuous inductor current mode. (DCM or CCM).

#### Asyn-Inverter in DCM:

We call it DCM because inductor current falls to zero on each switch cycle. The benefit of designing in DCM is the simple loop compensation, which has no RHPZ (Right Hand Plan Zero) and conjugate double pole in the frequency domain to worry about, but has a single load pole instead. However, the output ripple and efficiency are worse than in CCM (Continuous Inductor Current). If the loading is around tens of mA, it is not bad to design in DCM with less impact on the output ripple and efficiency, but gain more easy to stabilize the control loop.

The fixed parameters for CH5 asyn-inverter in DCM compensation are as follows:

- Transconductance (from FB to COMP), GM = 200μs

- Internal voltage ramp to decide duty cycle, V<sub>P</sub> = 1V

- Feedback voltage, V<sub>FB</sub> = FB = 0V

- Reference voltage, V<sub>REF</sub> = 1V

# **RT9911**

RICHTE

The input parameters for CH5 asyn-inverter in DCM compensation are as follows:

- R1, the voltage divider resistor in between V<sub>OUT</sub> and FB.

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- f<sub>OSC</sub>, operating frequency

- · L. inductance

- C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

- R<sub>ESR</sub>, ESR (Equivalent Series Resistance) of C<sub>OUT</sub> (ceramic output capacitor)

The results we will get for CH5 asyn-inverter in DCM compensation are as follows:

- R2, the voltage divider resistor in between FB and V<sub>REF</sub>.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with R<sub>C</sub> and connect to ground

- C<sub>P</sub>, connect in between COMP pin and ground. (Can be ignored if  $C_P < 10pF$ )

The major steps for getting above results:

1. R2 = R1x

$$\frac{V_{REF} - V_{FB}}{V_{FB} - V_{OUT}}$$

. If R1 = 1M $\Omega$  and Vout = (-8)V then R2 = 1M x  $\frac{1 - 0}{0 - (-8)}$  = 125k $\Omega$

2. Select suitable inductor to ensure I<sub>OUT(MIN.)</sub> works in DCM, which is let inductor current falls to zero on each switch cycle.

$$L < \frac{V_{IN} x (1-D)}{2 x I_{OUT(MAX.)} x fosc}$$

3. Set f<sub>C</sub> sufficient below f<sub>OSC</sub>

For example:

$$f_C = \frac{f_{OSC}}{10}$$

or lower

For example:  $f_C = \frac{f_{OSC}}{10}$  or lower 4. Find the load pole:  $f_{LP} = \frac{2}{2\pi \times R_{LOAD} \times C_{OUT}}$

$$\text{where } R_{\text{LOAD}} = \frac{V_{\text{OUT}}}{I_{\text{OUT}(\text{MAX.})}}$$

5. Get Rc =

$$\frac{\frac{fc}{f_{LP}} \times V_P}{GM \times G_{dod}}$$

, where  $G_{dod} = \frac{V_{OUT}}{D}$ ,

which is duty to Vout transfer function.

$$D = duty \ cycle = \frac{abs(Vout)}{Vin + abs(Vout)}.$$

6. Get

$$C_C = C_{OUT} \times \frac{R_{LOAD}}{R_C}$$

by letting comp zero = load pole.

7. Find ffz, zero and ffp, pole ratio of voltage divider with

$$ratio = \frac{ffp}{ffz} = \frac{abs(Vout) + VREF}{VREF}$$

8. Get  $C_F$  by placing ffp on  $f_C$  and ffz therefore on  $\frac{f_C}{ratio}$

$$C_F = \frac{1}{2\pi \times ff_Z \times R1}$$

, where  $ff_Z = \frac{f_C}{ratio}$ .

9. Evaluate C<sub>P</sub>. C<sub>P</sub> is for canceling the zero from C<sub>OUT</sub> (ceramic output capacitor).

$$C_P = C_{OUT} \ x \, \frac{R_{ESR}}{R_C} \, . \, C_P \ can \ be \ ignore \ if \ C_P < 10 pF.$$

#### Asyn-Inverter in CCM:

We call it CCM because inductor current is always continuous in operation. The benefit of designing in CCM is lower V<sub>OUT</sub> and inductor current ripple and higher efficiency from the lower coil loss, but with the expense of larger inductor size and cost and the control loop comes with a RHPZ (Right Hand Plan Zero) and a conjugate double pole in the frequency domain to worry about.

The fixed parameters for CH5 asyn-inverter in CCM compensation are as follows:

- Transconductance (from FB to COMP), GM = 200us

- Internal voltage ramp to decide duty cycle, V<sub>P</sub> = 1V

- Feedback voltage, V<sub>FB</sub> = FB = 0V

- Reference voltage, V<sub>REF</sub> = 1V

The input parameters for CH5 asyn-inverter in CCM compensation are as follows:

- R1, the voltage divider resistor in between V<sub>OUT</sub> and

- V<sub>IN</sub>, input voltage.

- V<sub>OUT</sub>, desired output voltage

- I<sub>OUT(MAX.)</sub>, maximum output load

- I<sub>OUT(MIN.)</sub>, minimum output laod

- f<sub>OSC</sub>, operating frequency

- . L, inductance

- C<sub>OUT</sub>, output capacitance. This compensation is based on ceramic output capacitor.

- Resr., ESR (Equivalent Series Resistance) of Cout (ceramic output capacitor)

The results we will get for CH5 asyn-inverter in CCM compensation are as follows:

- R2, the voltage divider resistor in between FB and V<sub>REF</sub>.

- C<sub>F</sub>, feedforward capacitor in parallel with R1.

- R<sub>C</sub>, compensation resistor on COMP pin.

- C<sub>C</sub>, compensation capacitor in series with R<sub>C</sub> and connect to ground

- C<sub>P</sub>, connect in between COMP pin and ground. (Can be ignored if C<sub>P</sub> < 10pF)

The major steps for getting above results:

1. R2 = R1x

$$\frac{V_{REF} - V_{FB}}{V_{FB} - V_{OUT}}$$

. If R1 = 1M $\Omega$  and Vout = (-8)V then R2 = 1Mx  $\frac{1-0}{0-(-8)}$  = 125k $\Omega$

2. Select suitable inductor to ensure I<sub>OUT(MIN.)</sub> works in

$$\label{eq:ccm} \begin{split} & \cdot \text{CCM}, \\ & L < \frac{\text{Vin x (1-D)}}{2 \text{ x lout(Min.) x fosc}} \end{split}$$

3. Find RHPZ(Right Hand Plan Zero) location.

Find RHPZ(Right Hand Plan Zero) locat

$$\frac{(1-D)^2}{D}$$

RHPZ(Boost) = RLOAD  $\frac{D}{2\pi L}$ , where

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX)}}, D = duty \ cycle = \frac{abs(V_{OUT})}{V_{IN} + abs(V_{OUT})}$$

4. Set f<sub>C</sub> (cross over frequency) sufficiently below RHPZ.

For example:

$$fc = \frac{RHPZ}{6}$$

or lower

For example: fc =  $\frac{\text{RHPZ}}{6}$  or lower 5. Find the load pole: fLP =  $\frac{2}{2\pi \text{ x RLOAD x Cout}}$ ,

where

$$R_{LOAD} = \frac{abs(V_{OUT})}{I_{OUT(MAX.)}}$$

.

6. Get Rc =

$$\frac{\frac{fc}{f_{LP}} \times V_P}{GM \times G_{doc}}$$

, where  $G_{doc} = \frac{V_{IN}}{(1-D)^2}$ ,

which is duty to V<sub>OUT</sub> transfer function.

D = duty cycle =

$$\frac{abs(Vout)}{Vin + abs(Vout)}$$

Vout

7. Find fcdp =  $\frac{1-D}{2\pi \, x \, (LC)^2}$ ,

which is the conjugate double pole from LC filter.

- 8.  $Cc = \frac{1}{2\pi x \text{ fcdp } x \text{ Rc}}$  to cancel one of the double pole.

- 9. Find C<sub>f</sub> by placing its zero on fcdp to cancel another double pole.

$$C_F = \frac{1}{2\pi \times f_{cdp} \times R1}.$$

10.Evaluate C<sub>P</sub>. C<sub>P</sub> is for canceling the zero from C<sub>OUT</sub> (ceramic output capacitor).

$$C_P = C_{OUT} \ x \ \frac{R_{ESR}}{R_C} \, . \ C_P \ can \ be \ ignore \ if \ C_P < 10 pF.$$

#### **PCB Layout Considerations**

- The feedback netwok should be very close to the FB pin.

- The compensation network should be very close to the COMP pin and avoid through VIA.

- For CH3 current sense, CS should be close to the drain site of external NMOS.

- Keep high current path as short as possible.

DS9911-05 April 2011

### **Outline Dimension**

Note: The configuration of the Pin#1 identifier is optional, but must be located within the zone indicated.

| Cumbal | Dimensions I | n Millimeters | Dimension | s In Inches |

|--------|--------------|---------------|-----------|-------------|

| Symbol | Min          | Max           | Min       | Max         |

| А      | 0.800        | 1.000         | 0.031     | 0.039       |

| A1     | 0.000        | 0.050         | 0.000     | 0.002       |

| A3     | 0.175        | 0.250         | 0.007     | 0.010       |

| b      | 0.180        | 0.300         | 0.007     | 0.012       |

| D      | 5.950        | 6.050         | 0.234     | 0.238       |

| D2     | 4.000        | 4.750         | 0.157     | 0.187       |

| Е      | 5.950        | 6.050         | 0.234     | 0.238       |

| E2     | 4.000        | 4.750         | 0.157     | 0.187       |

| е      | 0.500        |               | 0.020     |             |

| L      | 0.350        | 0.450         | 0.014     | 0.018       |

V-Type 40L QFN 6x6 Package

### **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.