# **Driver IC for 3-phase Brushless Motor**

#### **FEATURES**

- Supply voltage range: 4.5 V ~ 26.4 V

- Built-in 5-V regulator

- 3-phase full-wave sine-wave PWM drive by 1-Hall-sensor

- Selectable Input Mode: Either linear voltage input or PWM input through VSP pin

- Controllable lower limit for linear voltage input mode through VSPL pin

- Conduction angle auto driver phase shift correction

- Rotation direction selectable (Forward/Reverse)

- FG pulse divide selectable

- Sleep mode

- Various protection functions: Under Voltage Lock Out (UVLO), Over Voltage Lock Out (OVLO), Thermal protection, Over Load Protection, and Over Current Protection

#### **DESCRIPTION**

AN44142A is a driver IC for 3-phase brushless motor optimized for fan motors. By employing the rotor position detector and sine wave PWM drive by 1-Hall-sensor, this IC achieves component reduction and miniaturization of motor set as well as motor drive at low noise, low vibration and low power consumption.

#### **APPLICATIONS**

• Driver IC for 3-phase brushless fan motor

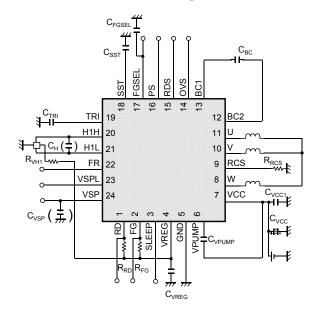

### TYPICAL APPLICATION

Notes: The application circuit is an example. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit in the design of the equipment.

$V_{CC}$  = 12 V,  $V_{FR}$  = 0 V,  $V_{VSP}$  = PWM mode (60kHz,Duty60%)

: 2014-07-08

Established: 2014-05-14 Revised

# **CONTENTS**

| FEATURES                   | 1  |

|----------------------------|----|

| DESCRIPTION                | 1  |

| APPLICATIONS               | 1  |

| TYPICAL APPLICATION        | 1  |

| TYPICAL CHARACTERISTICS    | 1  |

| CONTENTS                   | 2  |

| ABSOLUTE MAXIMUM RATINGS   | 3  |

| POWER DISSIPATION RATING   | 3  |

|                            |    |

| ELECTRICAL CHARACTERISTICS |    |

| PIN FUNCTIONS              |    |

| PIN CONFIGURATION          |    |

| FUNCTIONAL BLOCK DIAGRAM   | 10 |

| OPERATION                  | 11 |

| AREA OF SAFE OPERATION     | 33 |

| PIN EQUIVALENT CIRCUIT     | 34 |

| PACKAGE INFORMATION        | 41 |

| IMPORTANT NOTICE           | 44 |

| USAGE PRECAUTIONS          | 46 |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     | Symbol                                                                                                                                                                                             | Rating             | Unit     | Notes  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------|

| Supply voltage                | V <sub>CC</sub>                                                                                                                                                                                    | 28                 | ٧        | *1     |

| Operating ambient temperature | T <sub>opr</sub>                                                                                                                                                                                   | −40 ~ + 95         | °C       | *2     |

| Storage temperature           | $T_{stg}$                                                                                                                                                                                          | – 55 $\sim$ +150   | °C       | *2     |

|                               | $V_{VREG}$                                                                                                                                                                                         | $-0.3\sim6.0$      | ٧        | *3     |

| Input Voltage Range           | $\begin{matrix} V_{\text{SLEEP}}, V_{\text{H1H}}, V_{\text{H1L}}, V_{\text{FGSEL}}, \\ V_{\text{VSP}}, V_{\text{VSPL}}, V_{\text{FR}}, V_{\text{RDS}}, V_{\text{PS}}, V_{\text{OVS}} \end{matrix}$ | <b>-</b> 0.3 ∼ 6.0 | <b>V</b> | _      |

|                               | V <sub>TRI</sub> ,V <sub>SST</sub>                                                                                                                                                                 | $-0.3\sim6.0$      | ٧        | _      |

|                               | $V_{FG}$ , $V_{RD}$                                                                                                                                                                                | $-0.3\sim6.0$      | V        | _      |

|                               | $V_{VREG}$                                                                                                                                                                                         | $-0.3\sim6.0$      | V        | _      |

| Output Voltage Range          | $V_{RCS}$                                                                                                                                                                                          | $-0.3\sim6.0$      | ٧        | *4     |

|                               | V <sub>BC1</sub>                                                                                                                                                                                   | 28                 | V        | *4     |

|                               | $V_{BC2}, V_{pump}$                                                                                                                                                                                | 37                 | ٧        | *4     |

|                               | I <sub>Udc</sub> , I <sub>Vdc</sub> , I <sub>Wdc</sub>                                                                                                                                             | ± 600              | mA       | *5     |

| Output Current Bango          | I <sub>Upeak</sub> , I <sub>Vpeak</sub> , I <sub>Wpeak</sub>                                                                                                                                       | ± 2200             | mA       | *5, *6 |

| Output Current Range          | I <sub>FG</sub> ,I <sub>RD</sub>                                                                                                                                                                   | 5                  | mA       | _      |

|                               | I <sub>VREG</sub>                                                                                                                                                                                  | -10                | mA       | _      |

| ESD                           | HBM                                                                                                                                                                                                | 2                  | kV       | _      |

Notes: This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteed as it is higher than our stated recommended operating range. When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.

- \*1:The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

- \*2: Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for Ta = 25°C.

- \*3: Applying external voltage to this pin is possible only when this pin and VCC pin is connected.

When applying external voltage to this pin, do not exceed the stated ratings even in transient state.

- \*4: Applying external voltage into these pins is prohibited. Do not exceed the stated ratings even in transient state.

- \*5: Applying external voltage into these pins is prohibited. Do not exceed the stated ratings even in transient state.

- \*6: For VCC≥5.6 V, output current of ±2200 mA is only allowed within 100μs. For VCC<5.6 V, output current of ±1500 mA is only allowed within 100μs.

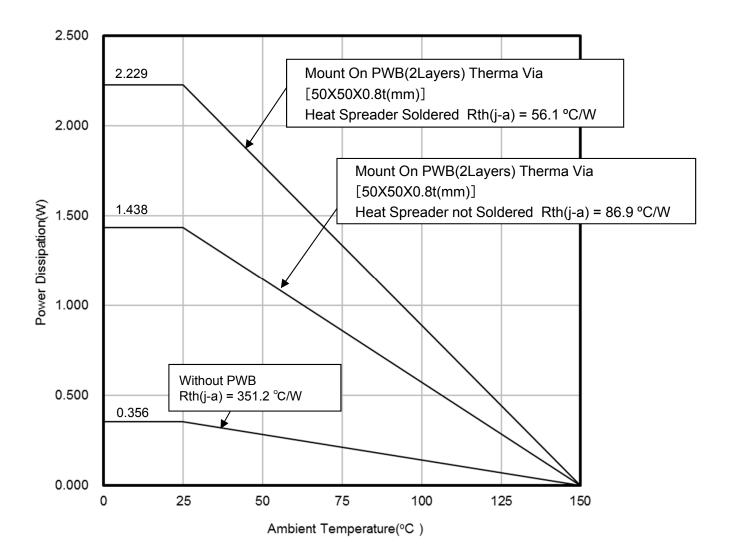

#### POWER DISSIPATION RATING

| Package                                                | $\theta_{j-a}$ | $\theta_{	ext{j-c}}$ | P <sub>D</sub><br>(T <sub>a</sub> =25 °C) | P <sub>D</sub><br>(T <sub>a</sub> =70 °C) |

|--------------------------------------------------------|----------------|----------------------|-------------------------------------------|-------------------------------------------|

| 24 pin Plastic Quad Flat Non-leaded Package (QFN type) | 56.1 °C/W      | 4.4 °C/W             | 2.22 W                                    | 1.42 W                                    |

Notes: For the actual usage, please refer to the P<sub>D</sub>-T<sub>a</sub> characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

\*1: Glass-Epoxy Substrate (2 Layers) : 50 x 50 x 0.8t (mm), Heat dissipation fin: Die-pad, Soldered. (Heat dissipation via 2 layer board)

#### **CAUTION**

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates.

## **AN44142A**

#### RECOMMENDED OPERATING CONDITIONS

| Parameter            | Symbol             | Min. | Тур.  | Max.       | Unit | Notes    |

|----------------------|--------------------|------|-------|------------|------|----------|

| Supply voltage range | V <sub>CC</sub>    | 4.5  | _     | 26.4       | V    | _        |

|                      | V <sub>SLEEP</sub> | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | V <sub>H1H</sub>   | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | V <sub>H1L</sub>   | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | $V_{PS}$           | 0    | _     | $V_{VREG}$ | V    | *1       |

| Input voltage range  | $V_{RDS}$          | 0    | _     | $V_{VREG}$ | V    | *1       |

| Imput voitage range  | V <sub>OVS</sub>   | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | $V_{FGSEL}$        | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | $V_{VSP}$          | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | $V_{VSPL}$         | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | $V_{FR}$           | 0    | _     | $V_{VREG}$ | V    | *1       |

|                      | C <sub>VCC</sub>   | 4.7μ | _     | _          | F    | *2,*3    |

|                      | C <sub>VCC1</sub>  | _    | 0.1μ  | _          | F    | *2,*3    |

|                      | $C_{VREG}$         | _    | 0.1μ  |            | F    | *2,*4    |

|                      | $C_{SST}$          | 22p  | 1800p |            | F    | *2,*5    |

|                      | C <sub>BC</sub>    | _    | 0.1μ  |            | F    | *2,*4    |

| External constants   | $C_{VPUMP}$        | _    | 0.1μ  | _          | F    | *2,*4    |

|                      | $C_{TRI}$          | 220p | 390p  | 1300p      | F    | *2,*5    |

|                      | R <sub>RCS</sub>   | 0.15 | 0.22  | _          | Ω    | *2,*5,*6 |

|                      | R <sub>VH</sub>    | _    | 1k    | _          | Ω    | *2,*5    |

|                      | $C_{FGSEL}$        | _    | 0.01μ | _          | F    | *2,*7    |

|                      | C <sub>VSP</sub>   |      | 0.1μ  | _          | F    | *2,*8    |

Note: \*1: For setting range of input control voltage, refer to Electrical Characteristics (page 5 - 8) and Operation (page 11 - 32).

- \*3: Please perform sufficient evaluation and verification to ensure that VCC pin voltage ripple is reduced.

- \*4: It is recommended to use the values indicated.

- \*5: Please choose the setting according to the usage. Please refer to the Electrical Characteristics (page 5 8) and Operation (page 11 32)

- \*6: Do not use resistor of value smaller than this. When using value smaller than the minimum value, latch-up function which is used to prevent thermal damage may operate due to external factors (PCB heat dissipation, metal impedance, etc...) or internal factors (threshold change, etc...).

- \*7: When using with FGSEL pin open, please connect capacitor to the FGSEL pin to prevent noise and carry out sufficient evaluation and verification.

- \*8: When VSP pin is used for DC input, it is recommended to insert a capacitor to the VSP pin.

<sup>\*2:</sup> Operation of mass production set is not guaranteed. Perform enough evaluation and verification on the design of mass production set.

**AN44142A**

## **ELECTRICAL CHARACTERISTICS**

$V_{\rm CC}$  = 12.0 V,  $V_{\rm VREG}$  = 5.0 V

Note:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

|     | Damanatan                             | Ols al              | 0                           |       | Limits | 1114           | NI - 4 - |      |

|-----|---------------------------------------|---------------------|-----------------------------|-------|--------|----------------|----------|------|

|     | Parameter                             | Symbol              | Condition                   | Min   | Тур    | Max            | Unit     | Note |

| Cir | cuit Current                          |                     |                             |       |        |                |          |      |

|     | V <sub>CC</sub> current               | I <sub>CC1</sub>    | _                           | 3.0   | 5.6    | 9.0            | mA       | _    |

|     | V <sub>CC</sub> current at sleep mode | I <sub>CC3</sub>    | V <sub>SLEEP</sub> = H      |       |        | 50             | μА       | _    |

| Re  | gulator Block                         |                     |                             |       |        |                |          |      |

|     | VREG voltage                          | $V_{VREG}$          | _                           | 4.7   | 5      | 5.3            | V        | _    |

|     | Output impedance                      | Z <sub>VREG</sub>   | $I_{VREG} = -10 \text{ mA}$ | _     | _      | 10             | Ω        | _    |

| FG  | Block                                 |                     |                             |       |        |                |          |      |

|     | FG output (low voltage)               | $V_{FGL}$           | I <sub>FG</sub> = 1.0 mA    | _     | 0.1    | 0.3            | V        | _    |

| RD  | Block                                 |                     |                             |       |        |                |          |      |

|     | RD output (low voltage)               | $V_{RDL}$           | I <sub>RD</sub> = 1.0 mA    | _     | 0.1    | 0.3            | V        | _    |

| Po  | wer Block                             |                     |                             |       |        |                |          |      |

|     | On resistance                         | R <sub>ONHL</sub>   | I = 400 mA                  | 0.5   | 1.0    | 1.5            | Ω        | _    |

|     | On resistance (Vcc=4.5V)              | R <sub>ONHL</sub>   | Vcc = 4.5V<br>I = 400 mA    | _     | 1.25   | 2.05           | Ω        | _    |

|     | Diode forward voltage                 | $V_{DI}$            | I = 400 mA                  | 0.6   | 0.8    | 1              | V        | _    |

| Мо  | tor Lock Protection                   |                     | •                           | -     | -      | •              | •        | •    |

|     | Lock detection time                   | t <sub>LOCK1</sub>  | _                           | 0.35  | 0.5    | 0.65           | s        | _    |

|     | Lock release time                     | t <sub>LOCK2</sub>  | _                           | 3.5   | 5      | 6.5            | S        | _    |

|     | Lock protection ratio                 | PR <sub>RATIO</sub> | _                           | 9     | 10     | 11             | _        | _    |

| Ov  | er Current Protection                 |                     |                             |       |        |                |          |      |

|     | Over current detection level          | V <sub>CL1</sub>    | _                           | 0.225 | 0.250  | 0.275          | V        | _    |

| Ha  | ll Block                              |                     | l.                          |       |        | l              |          |      |

|     | Input dynamic range                   | $V_{HALL}$          | _                           | 0     | _      | VREG -<br>2.0V | V        | _    |

|     | Pin current                           | I <sub>HALL</sub>   | _                           | -2    | 0      | 2              | μΑ       | _    |

|     | Input offset voltage for H1H—H1L drop | $V_{HOFS}$          | _                           | -6    | 0      | 6              | mV       | _    |

|     | Min. input amplitude voltage          | $V_{HA}$            | _                           | 25    | _      | _              | mV       | _    |

|     | Hysteresis width                      | $V_{HHYS}$          | _                           | 7.5   | 10     | 13             | mV       | _    |

| SL  | EEP                                   |                     | 1                           |       |        |                |          |      |

|     | Low-level input voltage               | $V_{SLL}$           | _                           | _     | _      | 0.5            | V        | _    |

|     | High-level input voltage              | V <sub>SLH</sub>    | _                           | 2.5   | _      | _              | V        | _    |

|     | Open-circuit voltage                  | V <sub>SLZ</sub>    | _                           | 1 —   | 0      | 0.3            | V        |      |

|     | Input impedance                       | Z <sub>SL</sub>     | _                           | 70    | 100    | 130            | kΩ       |      |

AN44142A

# **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{\rm CC}$  = 12.0 V,  $V_{\rm VREG}$  = 5.0 V

Note:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

| Parameter                                            | Symbol               | Condition                                 |       | Limits |       | Unit     | Note        |

|------------------------------------------------------|----------------------|-------------------------------------------|-------|--------|-------|----------|-------------|

|                                                      | Syllibol             | Condition                                 | Min   | Тур    | Max   | Oilit    | NOLE        |

| VSP                                                  |                      |                                           |       |        | _     |          |             |

| Pin current                                          | I <sub>VSP</sub>     | V <sub>VSP</sub> =5.0V                    | _     | 15     | 45    | μΑ       | —           |

| VSP DC Input Control                                 |                      |                                           |       |        |       |          |             |

| Stop control VSP input                               | V <sub>VSPDCL</sub>  | _                                         | 0.9   | 1.0    | 1.1   | >        | _           |

| Max. speed VSP input                                 | V <sub>VSPDCH</sub>  | _                                         | 3.6   | 4.0    | 4.4   | ٧        | _           |

| VSP PWM Input Control                                |                      |                                           |       |        |       |          |             |

| Stop control VSP input                               | V <sub>VSPPWML</sub> | V <sub>VREG</sub> =V <sub>OSC</sub> =5.0V | 2     | 3      | 4     | %        | *1,*2<br>*3 |

| Max. speed VSP input                                 | V <sub>VSPPWMH</sub> | V <sub>VREG</sub> =V <sub>OSC</sub> =5.0V | _     | 100    | _     | %        | *1,*2<br>*5 |

| Low-level input voltage during PWM input             | V <sub>VSPLL</sub>   | V <sub>VREG</sub> =V <sub>OSC</sub> =5.0V | _     | -      | 1.0   | >        | *1,*2       |

| High-level input voltage during PWM input            | V <sub>VSPHL</sub>   | V <sub>VREG</sub> =V <sub>OSC</sub> =5.0V | 2.0   | ı      | _     | >        | *1,*2       |

| PWM input frequency range                            | $F_PWM$              | _                                         | 15    | _      | 100   | kHz      | *1,*2       |

| VSPL DC Input Control                                |                      |                                           |       |        |       |          |             |

| VSPL enabled input voltage range                     | $V_{VSPL}$           | _                                         | 1.3   | _      | 3.0   | V        | _           |

| Pin current                                          | I <sub>VSPL</sub>    | V <sub>VSPL</sub> =5.0V                   | _     | 5      | 15    | μΑ       | _           |

| Internal Oscillation Frequency                       |                      |                                           |       |        |       |          |             |

| Internal oscillation frequency                       | f <sub>OSC</sub>     | _                                         | 17.5  | 25     | 32.5  | MHz      | _           |

| Triangle Wave Oscillator for PWM Wav                 |                      | pin)                                      |       |        |       |          |             |

| Amplitude                                            | $V_{TRI}$            | _                                         | 1.36  | 1.53   | 1.70  | Vpp      | _           |

| External capacitor charging current                  | I <sub>TRI1</sub>    | V <sub>TRI</sub> =0.5V                    | -83.5 | -64.5  | -45.5 | μΑ       | _           |

| External capacitor discharging current               | I <sub>TRI2</sub>    | V <sub>TRI</sub> =2.0V                    | 45.5  | 64.5   | 83.5  | μΑ       | _           |

| TRI pin input voltage during PWM control             | $V_{TRITH}$          | _                                         | 2.9   | ı      | _     | <b>V</b> | *2          |

| Triangle Wave Oscillator during Soft Start (SST pin) |                      |                                           |       |        |       |          |             |

| Amplitude                                            | $V_{SST}$            | _                                         | 0.75  | 1.0    | 1.25  | Vpp      | _           |

| External capacitor charging current                  | I <sub>SST1</sub>    | V <sub>SST</sub> =0.6V                    | -6.0  | -4.0   | -2.0  | μΑ       | _           |

| External capacitor discharging current               | I <sub>SST2</sub>    | V <sub>SST</sub> =1.6V                    | 2.0   | 4.0    | 6.0   | μА       |             |

| SST pin input voltage when Soft Start not used       | V <sub>SSTTH</sub>   | _                                         | 2.9   | _      | _     | ٧        | *4          |

Established: 2014-05-14 : 2014-07-08 Revised

Note: \*1: During PWM control, VSPL pin must be connected to GND.

\*2: During PWM control setting, TRI pin must be connected to VREG pin.

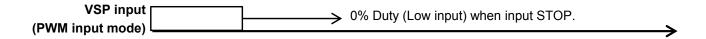

<sup>\*3:</sup> It is recommended to input 0% Duty (Low input) when input STOP.

<sup>\*4:</sup> When Soft Start is not in used, SST pin must be connected to VREG pin.

<sup>\*5:</sup> Typical Design Value.

**AN44142A**

# **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{\rm CC}$  = 12.0 V,  $V_{\rm VREG}$  = 5.0 V

Note:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

|    | Parameter                   | Symbol              | Condition                |              | Limits | Limits |      |      |

|----|-----------------------------|---------------------|--------------------------|--------------|--------|--------|------|------|

|    | Parameter                   | Symbol              | Condition                | Min          | Тур    | Max    | Unit | Note |

| FR | (3-State Input circuit)     |                     |                          |              |        |        |      |      |

|    | Low-level input voltage     | $V_{FRL}$           | _                        | _            | _      | 8.0    | V    | _    |

|    | Mid-level input voltage     | $V_{FRM}$           | _                        | 1.3          |        | 2.0    | V    | _    |

|    | High-level input voltage    | $V_{FRH}$           | _                        | 2.5          |        |        | V    | _    |

|    | Open-circuit voltage        | $V_{FRZ}$           | _                        | 1.4          | 1.65   | 1.9    | ٧    | _    |

|    | Pin current                 | I <sub>INFR</sub>   | V <sub>FR</sub> = 0 V    | - 40         | - 20   |        | μА   | _    |

| FG | SEL (3-State Input circuit) | -                   | •                        | <del>-</del> |        |        | -    |      |

|    | Low-level input voltage     | V <sub>FGSELL</sub> | _                        | _            |        | 1.0    | V    | _    |

|    | High-level input voltage    | $V_{FGSELH}$        | _                        | 4.0          | _      | _      | V    | *1   |

|    | Open-circuit voltage        | V <sub>FGSELZ</sub> | _                        | 1.8          | 2.4    | 2.8    | V    | *2   |

|    | Pin current                 | I <sub>INFG</sub>   | V <sub>FGSEL</sub> = 0 V | - 40         | - 20   | _      | μА   | _    |

| PS | (2-State Input circuit)     |                     |                          |              |        |        |      |      |

|    | Low-level input voltage     | $V_{PSL}$           | _                        | _            |        | 1.0    | ٧    | _    |

|    | High-level input voltage    | $V_{PSH}$           | _                        | 4.0          |        |        | V    | *1   |

|    | Open-circuit voltage        | $V_{PSZ}$           | _                        | _            | 0.0    | 0.5    | V    | _    |

|    | Pin current                 | I <sub>INPS</sub>   | V <sub>PS</sub> = 5.0 V  | _            | 5      | 15     | μΑ   | _    |

| RD | S (2-State Input circuit)   |                     |                          |              |        |        |      |      |

|    | Low-level input voltage     | $V_{RDSL}$          | _                        | _            |        | 1.0    | ٧    | _    |

|    | High-level input voltage    | $V_{RDSH}$          | _                        | 4.0          |        |        | ٧    | *1   |

|    | Open-circuit voltage        | $V_{RDSZ}$          | _                        | _            | 0.0    | 0.5    | ٧    | _    |

|    | Pin current                 | I <sub>INRDS</sub>  | V <sub>RDS</sub> = 5.0 V | _            | 5      | 15     | μΑ   | _    |

| ٥٧ | /S (2-State Input circuit)  |                     |                          |              |        |        |      |      |

|    | Low-level input voltage     | V <sub>OVSL</sub>   | _                        | _            | _      | 1.0    | V    | _    |

|    | High-level input voltage    | V <sub>OVSH</sub>   | _                        | 4.0          |        |        | V    | *1   |

|    | Open-circuit voltage        | V <sub>OVSZ</sub>   | _                        | _            | 0.0    | 0.5    | V    |      |

|    | Pin current                 | I <sub>INOVS</sub>  | V <sub>OVS</sub> = 5.0 V | _            | 5      | 15     | μА   | _    |

Note: \*1: During High level setting, please ensure to connect to VREG pin.

<sup>\*2:</sup> Please connect a capacitor to FGSEL pin when it is open during use to prevent noise. To ensure the noise prevention, please perform sufficient evaluation and verification.

**AN44142A**

# **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{\rm CC}$  = 12.0 V,  $V_{\rm VREG}$  = 5.0 V

Note:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

|     | Devementer                          | Cumbal             | Condition                  | Des  | sign val | ue   | Unit | Note |

|-----|-------------------------------------|--------------------|----------------------------|------|----------|------|------|------|

|     | Parameter                           | Symbol             | Condition                  | Min  | Тур      | Max  | Unit | Note |

| Th  | ermal Protection                    |                    |                            |      |          |      |      |      |

|     | Protection operating temperature    | TSD <sub>ON</sub>  | _                          | _    | 160      | _    | °C   | *1   |

|     | Hysteresis width                    | TSD <sub>HYS</sub> | _                          | _    | 25       | _    | °C   | *1   |

| Ou  | tput Block                          |                    |                            |      |          |      |      |      |

|     | Output slew rate at source current  | $V_{TRSO}$         | _                          | _    | 300      | _    | V/μs | *1   |

|     | Output slew rate at source current  | V <sub>TFSO</sub>  | _                          | _    | 300      | _    | V/μs | *1   |

|     | Output slew rate at sink current    | V <sub>TRSI</sub>  | _                          | _    | 300      | _    | V/μs | *1   |

|     | Output slew rate at sink current    | $V_{TFSI}$         | _                          | _    | 300      | _    | V/μs | *1   |

| Tri | angle Wave Oscillator for PWM Wav   | eform (TRI         | pin)                       |      |          |      |      |      |

|     | Oscillation frequency range         | f <sub>TRI</sub>   | _                          | 15   | _        | 100  | kHz  | *2   |

|     | Standard oscillation frequency      | F <sub>TRI</sub>   | C <sub>TRI</sub> = 390 pF  | _    | 55.4     | _    | kHz  | *1   |

| Tri | angle Wave Oscillator during Soft S | tart (SST pi       | n)                         |      |          |      |      |      |

|     | Standard oscillation frequency      | F <sub>SST</sub>   | C <sub>SST</sub> = 1800 pF | _    | 1.13     | _    | kHz  | *1   |

| Ма  | ximum Rotating Speed                |                    |                            |      |          |      |      |      |

|     | Minimum hall cycle                  | T <sub>HMIN</sub>  | _                          | _    | 173      | _    | μS   | *1   |

| Un  | der Voltage Lock Out                |                    |                            |      |          |      |      |      |

|     | Protection operating voltage        | $V_{LVON}$         | _                          | _    | 3.55     | _    | V    | *1   |

|     | Protection release voltage          | $V_{LVOFF}$        | _                          | _    | 3.75     | _    | V    | *1   |

| Ov  | er Voltage Lock Out                 |                    |                            |      |          |      |      |      |

|     | Protection operating voltage 1      | V <sub>OVON1</sub> | V <sub>OVS</sub> = VREG    | 15.0 | 16.0     | 17.0 | V    | *1   |

|     | Protection operating voltage 2      | V <sub>OVON2</sub> | V <sub>OVS</sub> = 0V      | 26.4 | 27.2     | 28.0 | V    | *1   |

Note: \*1: Typical Design Value.

Page 8 of 48

<sup>\*2:</sup> These are values checked by design but not production tested.

# AN44142A

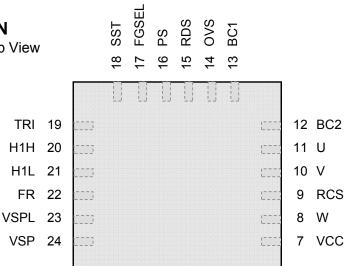

## PIN CONFIGURATION

Top View

SLEEP VREG

RD FG

9

GND

### **PIN FUNCTIONS**

| Pin No. | Pin name | Type           | Description                                                                                                                             |  |  |  |

|---------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | RD       | Output         | Over load protection                                                                                                                    |  |  |  |

| 2       | FG       | Output         | FG external output                                                                                                                      |  |  |  |

| 3       | SLEEP    | Input          | Sleep setting                                                                                                                           |  |  |  |

| 4       | VREG     | Output         | nternal reference voltage                                                                                                               |  |  |  |

| 5       | GND      | Ground         | Ground                                                                                                                                  |  |  |  |

| 6       | VPUMP    | Output         | Charge pump circuit output                                                                                                              |  |  |  |

| 7       | VCC      | Power          | Supply voltage for motor                                                                                                                |  |  |  |

| 8       | W        | Output         | W-phase output                                                                                                                          |  |  |  |

| 9       | RCS      | Output         | Motor current detector                                                                                                                  |  |  |  |

| 10      | V        | Output         | V-phase output                                                                                                                          |  |  |  |

| 11      | U        | Output         | U-phase output                                                                                                                          |  |  |  |

| 12      | BC2      | Output         | Capacitor connection pin 2 for charge pump                                                                                              |  |  |  |

| 13      | BC1      | Output         | Capacitor connection pin 1 for charge pump                                                                                              |  |  |  |

| 14      | ovs      | Input          | Over voltage detection selectable threshold. High for 16V detection, Low for 27.2V detection                                            |  |  |  |

| 15      | RDS      | Input          | Selectable Release of Motor lock protection. High to use the release of lock protection. Low to disable the release of lock protection. |  |  |  |

| 16      | PS       | Input          | Selectable phase shift mode. High to enable Auto Phase FB shift mode. Low to enable constant phase shift mode.                          |  |  |  |

| 17      | FGSEL    | Input          | FG pulse count select                                                                                                                   |  |  |  |

| 18      | SST      | Input / Output | Capacitor connection pin for Soft Start triangle wave oscillator frequency setting                                                      |  |  |  |

| 19      | TRI      | Input / Output | Capacitor connection pin for PWM triangle wave oscillator frequency setting                                                             |  |  |  |

| 20      | H1H      | Input          | Hall amplifier input (+)                                                                                                                |  |  |  |

| 21      | H1L      | Input          | Hall amplifier input (-)                                                                                                                |  |  |  |

| 22      | FR       | Input          | Rotation direction select (Forward/Reverse)                                                                                             |  |  |  |

| 23      | VSPL     | Input          | Voltage input for setting low rotating speed during DC input mode                                                                       |  |  |  |

| 24      | VSP      | Input          | Voltage input for setting rotating speed                                                                                                |  |  |  |

Page 9 of 48

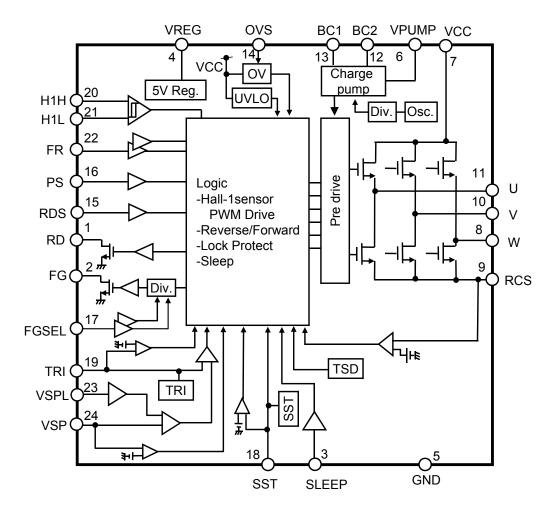

### **FUNCTIONAL BLOCK DIAGRAM**

Notes: This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

# **Panasonic**

**AN44142A**

## **OPERATION**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

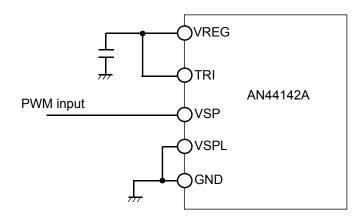

### 1. VSP input configuration

#### 1-1. PWM input mode

PWM input control or DC input control are used as the input controls to VSP pin. When using PWM input control, please ensure to connect TRI pin to VREG pin. VSPL pin shall be open or connected to GND pin (It is recommended to connect to GND.).

#### PWM input control signal detection

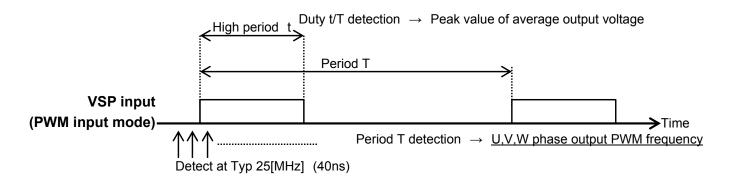

The below periodic signal T and Duty signal t/T is detected when PWM is input to VSP pin. Periodic signal T respond to output PWM frequency and Duty signal t/T respond to speed signal.

Doc No. TA4-EA-06255

Revision. 2

# **Panasonic**

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

- 1. VSP input configuration (Continued)

- 1-1. PWM input mode (Continued)

#### Points to note when using PWM input mode

#### Operation when input at VSP=100%duty

During output, when the VSP PWM input duty changes from below 100% to 100% duty, the frequency (period t) that is being input will halt and 100% input will be detected.

Therefore, output frequency will become 1/t. (However, this will be reflected in the output about 7t later, after signal is changed to 100% duty.)

When VSP pin is already input with 100% duty during power or SLEEP start-up, operation is at output frequency of about 58kHz.

After which, when PWM signal is input to the VSP pin and frequency signal is detected, output frequency will follow the frequency that is being input to VSP pin.

#### Maximum pulse width when VSP below 100% is input

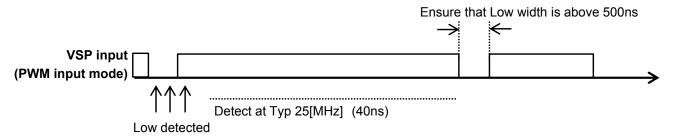

VSP input resolution under PWM input mode is typ 25MHz(40ns period).

Therefore, input pulse below 40ns may not be detected.

This is especially when input is near to 100% duty, period T signal many not be correctly detected.

Therefore to ensure that normal signal can be detected, please ensure that input to VSP pin at Low is above 500ns and more.

It is recommended to input 0% Duty (Low input) when input STOP.

Under PWM input mode, please ensure that PWM signal is input to the VSP pin.

Page 12 of 48

Revision. 2

# **Panasonic**

**AN44142A**

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

### 1. VSP input configuration (Continued)

#### 1-2. VSP input mode

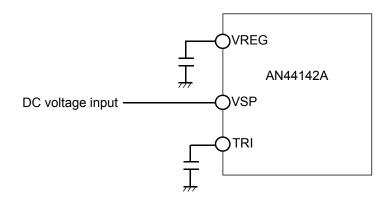

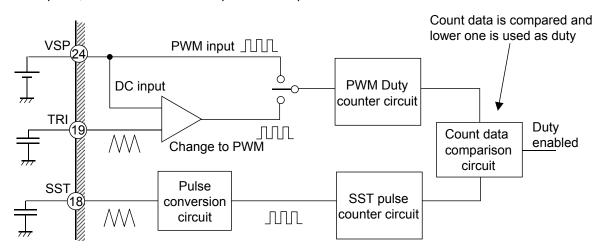

PWM input control or DC input control are used as the input controls to VSP pin.

When using DC input control, please ensure to connect a capacitor between TRI pin and GND pin.

Signal during DC input mode

During DC input mode, PWM signal is generated by the comparison between the TRI pin triangle waveform and the VSP pin input DC voltage.

Peak value of average output voltage is dependent on VSP pin voltage and output PWM frequency is dependent on TRI pin triangle waveform frequency.

#### TRI pin triangle wave oscillator frequency

The triangle wave oscillator frequency input into TRI pin is calculated using the below formula.

Triangle wave oscillator frequency

$$f_{TRI} = \frac{A}{2 \times C_{TRI} \times V_{TRI}}$$

$V_{TRI}\;$  : Triangle waveform amplitude (Under typ.1.53 V)

A : 64.5 μA (Under typ.)

#### Lower limit control using VSPL pin

During DC input control, lower limit of the VSP input voltage can be controlled by inputting DC voltage to the VSPL pin. When not controlling the lower limit, please ensure to connect VSPL pin to GND pin during use.

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

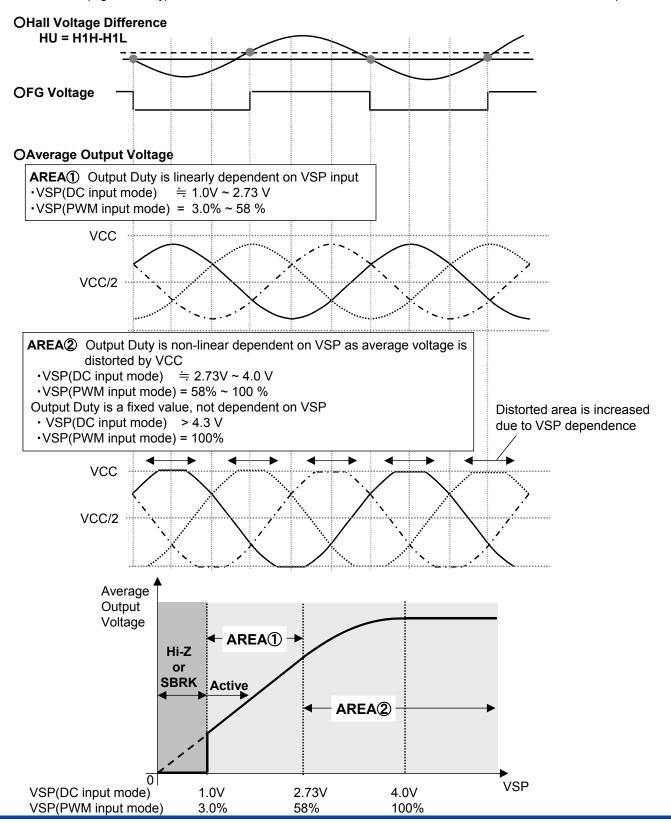

#### 2. VSP input voltage and average output voltage

Values in this page are all Typ values. In addition, these are where our recommended TRI value is used, under DC input mode.

# **Panasonic**

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

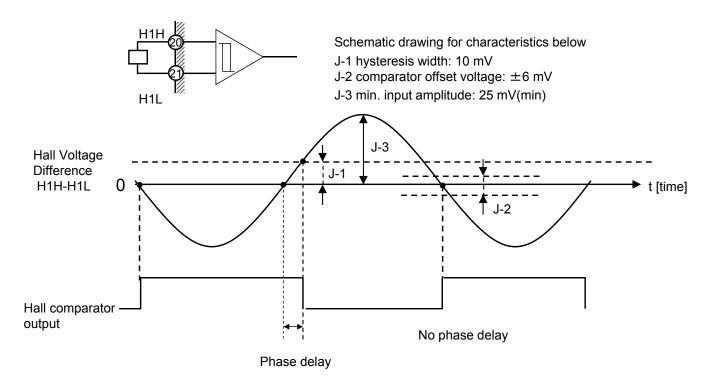

#### 3. Hall Input Specification

#### 3.1. System to detect hall signal

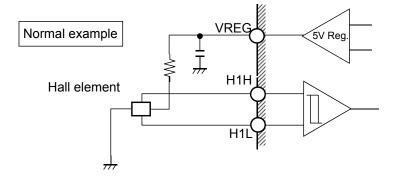

The motor position is detected by the Hall hysteresis comparator. If the amplitude of sine wave is small, phase delay of comparator output will be very prominent. Therefore, please make the amplitude of the sine wave larger. When chattering occurs to Hall element, insert a capacitor between H1H (pin 20) and H1L (pin 21).

For the biased source of the Hall element, please construct by externally shorting to VREG pin.

Page 15 of 48

# **Panasonic**

**AN44142A**

## **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

### 3. Hall Input Specification (Continued)

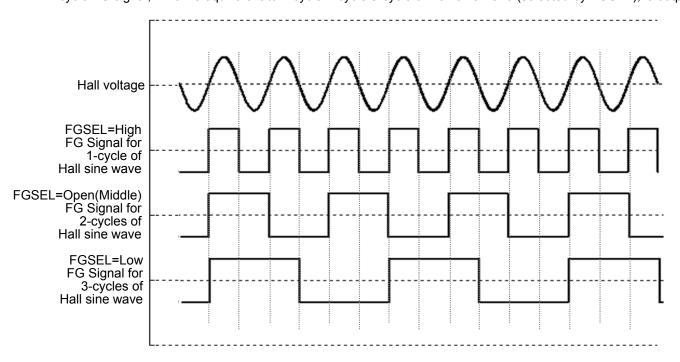

#### 3.2. The Relation between Hall Voltage and FGSEL

1-cycle FG signal, which is equivalent to 1-cycle/2-cycle/3-cycle of Hall sine wave (selected by FGSEL), is output.

# **Panasonic**

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

### 3. Hall Input Specification (Continued)

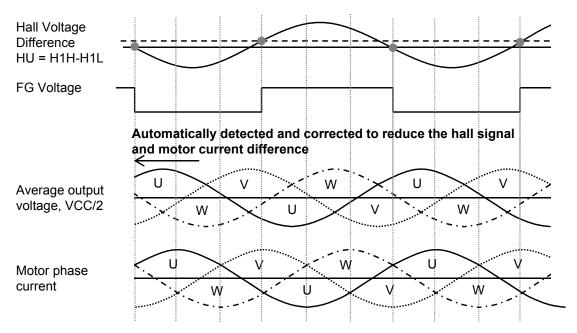

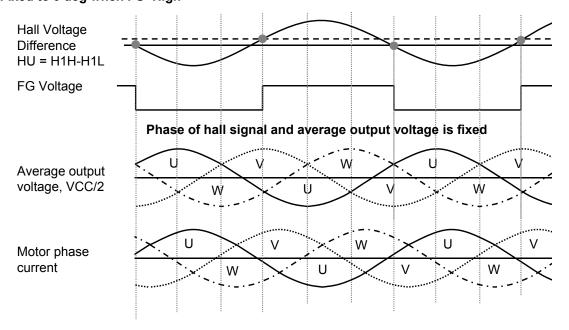

#### 3.3. Drive Phase Shift Control

Automatic drive phase shift control when PS=Low. The hall signal phase with respect to the conduction angle detects the IC's own phase difference and automatically correct it to the most optimum phase. The example for U-phase output voltage is shown below.

### Automatic drive phase shift control when PS=Low

#### Fixed to 0 deg when PS=High

Page 17 of 48

# **Panasonic**

**AN44142A**

## **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

### 3. Hall Input Specification (Continued)

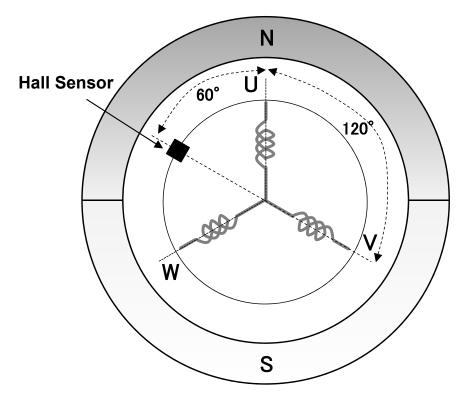

#### 3.4. Hall Sensor Placement

This IC uses only 1 hall sensor.

Please use the U-phase hall sensor for 3 phase 3 sensor motor

The diagram below shows the hall placement for a 2 pole 3 slots motor

Example placement for the hall sensor (2 pole 3 slot motor)

Page 18 of 48

# **Panasonic**

**AN44142A**

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 4. Start / Stop control

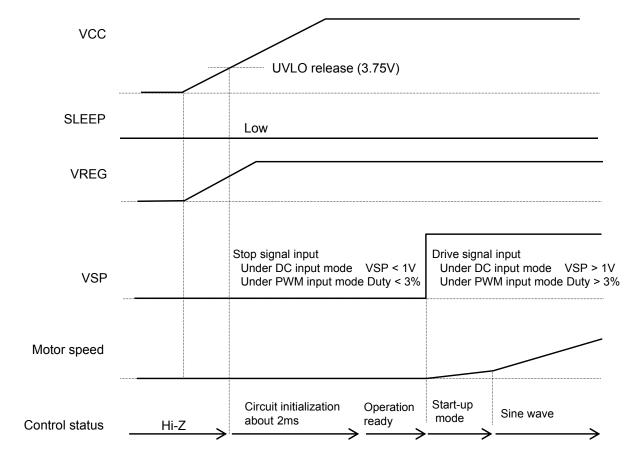

Start-up by rising VCC pin voltage

- After UVLO is released, circuit initialization is required for about 2ms and output signal is stopped. When circuit is under initialization, no signal is output even when VSP drive signal is inputted. Output of signal starts after initialization completes.

- •Start up mode is within 4 cycles hall signal input. During this period, no FG signal is output.

Page 19 of 48

# **Panasonic**

**AN44142A**

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 4. Start / Stop control (Continued)

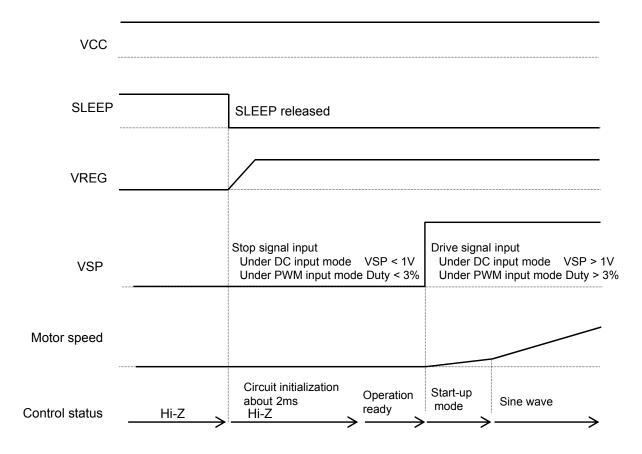

Start-up by SLEEP signal release

- •After SLEEP mode is released, circuit initialization is required for about 2ms and output signal is stopped. When circuit is under initialization, no signal is output even when VSP drive signal is inputted. Output of signal starts after initialization completes.

- ·Start up mode is within 4 cycles hall signal input. During this period, no FG signal is output.

Page 20 of 48

# **Panasonic**

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

## 4. Start / Stop control (Continued)

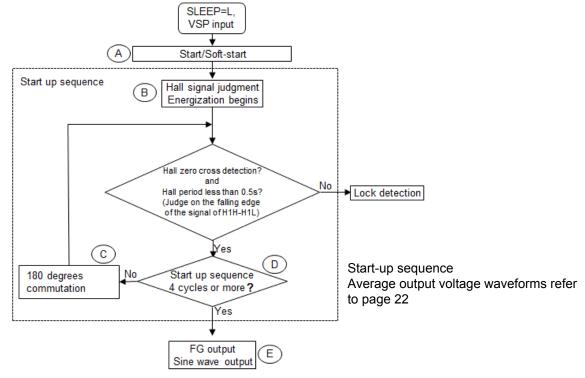

#### Start-up sequence

The flow chart below illustrates the start-up sequence.

#### Start-up sequence flow chart

Page 21 of 48

# **Panasonic**

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 4. Start / Stop control (Continued)

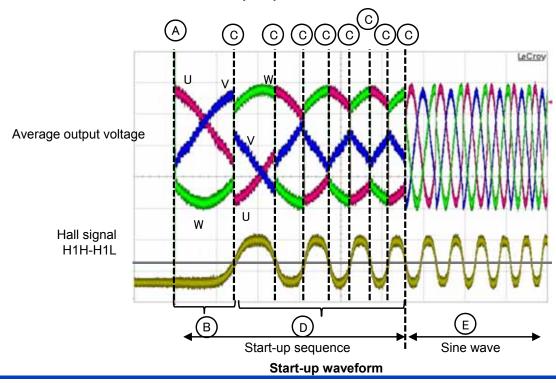

#### Start-up sequence (Continued)

#### Start-up sequence average output voltage.

The following waveforms illustrates the average output for different hall zero crossing detection, H1H-H1L at start-up.

Due to the initial position of the rotor, the starting torque differs slightly during start-up. For motor type

that requires large inertia force to turn, please ensure that sufficient starting current is available for the

motor. Please perform sufficient testing and evaluations to ensure this.

Page 22 of 48

# **Panasonic**

AN44142A

## **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

### 4. Start / Stop control (Continued)

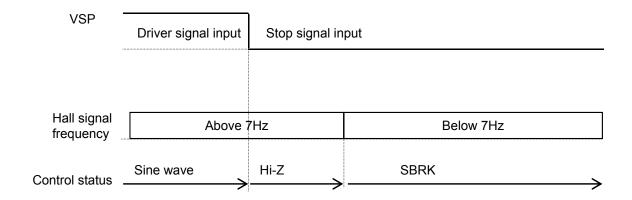

#### Stop

•When stop signal is input to VSP, hall signal frequency above 7Hz will result in Hi-Z at output and below 7Hz will result in SBRK at output.

# **Panasonic**

**AN44142A**

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

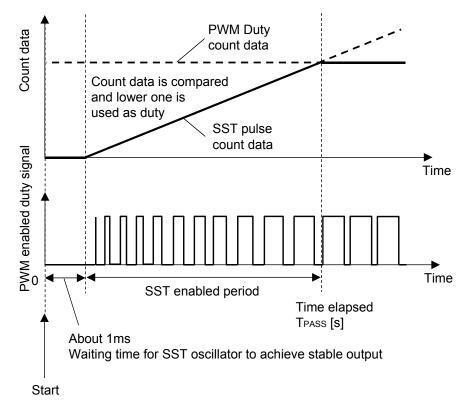

#### 5. Soft Start Function and PWM Specification

By connecting a capacitor to the SST pin, soft start control is performed by the start-up mode conditions during the mode transition. The period for soft start control is determined by the formula shown on the next page. When soft start control is not required, ensure to connect SST pin to VREG pin.

Below shows the correlation timing chart of count data and PWM enabled duty for VSP and SST.

•Notes on the use of the soft-start function.

With the increase in soft-start time, the motor current will also increase slowly . Therefore if the soft-start timing is too long, it will result in the motor not having enough starting torque and lock protection detection will be triggered if soft start timing is more than 0.5s (typ). This will cause the motor to be unable to start. Please evaluate and check this condition thoroughly when using this function.

Page 24 of 48

**AN44142A**

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 5. Soft Start Function and PWM Specification (Continued)

The triangle wave oscillator frequency output by SST pin is determined by the below formula. Soft Start timing is generated by comparing the VSP pin input PWM frequency and this triangle waveform frequency.

Triangle wave oscillator frequency

$$f_{SST} = \frac{A}{2 \times C_{SST} \times V_{SST}}$$

$V_{\text{SST}}\,$  : Triangle waveform amplitude (At typ. 1 V) : Current flowing in/out SST pin (At typ. 4 µA)

The PWM enabled duty reflected in the output, at the time elapsed T<sub>PASS</sub> within the SST enabled timing is determined by the below formula:

$$PWM \ duty = \frac{T_{PASS} \times T_{OSC}}{T_{SST} \times T_{PWM}} \qquad \begin{array}{c} T_{PWM} : \text{Input PWM cycle [s]} \\ T_{OSC} : \text{Oscillation cycle of internal oscillator} \\ 40*10^{-9} \ [s] \\ T_{SST} : SST \ triangle \ wave \ oscillation \ cycle[s] \end{array}$$

T<sub>PASS</sub>: Time elapsed [s]

T<sub>PASS</sub> at the end of the SST timing can be determined by the below formula:

$$T_{PASS} = \frac{T_{PWM} \times D \times T_{SST}}{T_{OSC}}$$

D : Input PWM duty [%]

Input PWM duty during the DC input can be determined by the below formula:

D =

$$\left(\frac{97}{3} \times V_{VSP} - \frac{88}{3}\right) \times 0.01$$

Under DC input,  $V_{VSP} = 1V \sim 4V$

Page 25 of 48

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

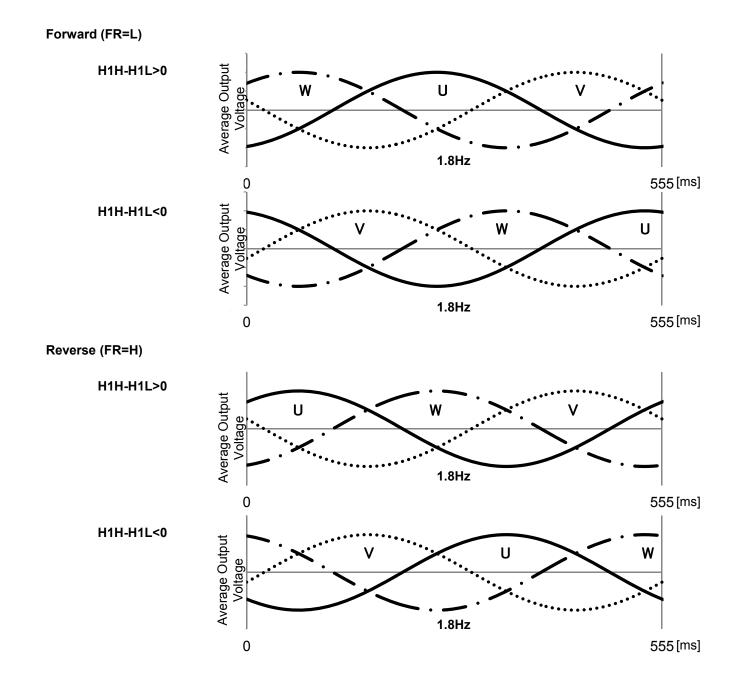

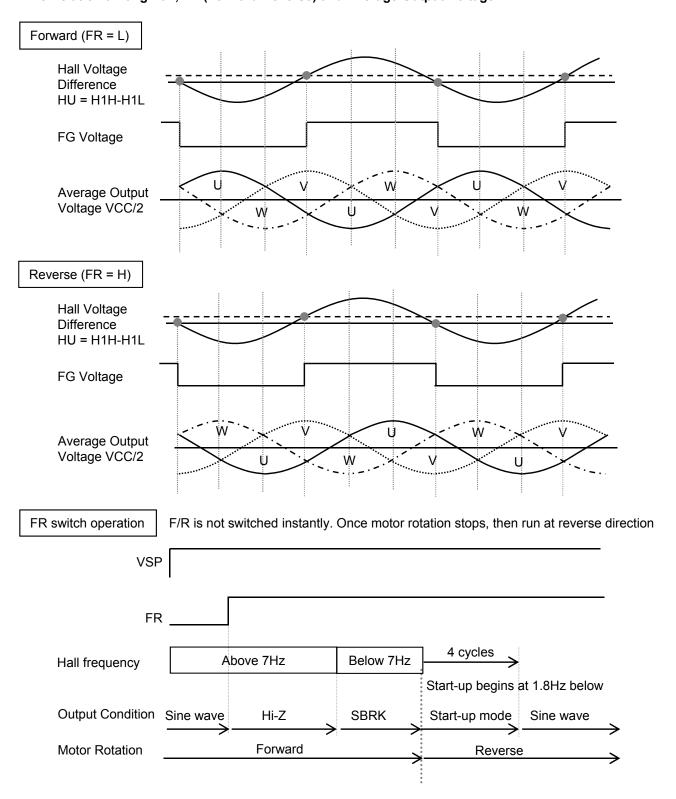

#### 6. Forward, Reverse and Short-break

The Relation among Hall, FR (Forward/Reverse) and Average Output Voltage

# **Panasonic**

**AN44142A**

## **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

## 6. Forward, Reverse and Short-break (Continued)

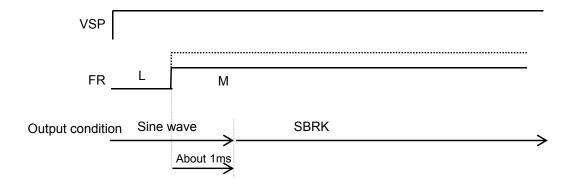

**Short-break mode**

Changes to short-break mode when FR=M.

Short-break may generate very large motor current. Please perform sufficient evaluation and verification to ensure that it does not exceed the absolute maximum ratings.

# **Panasonic**

**AN44142A**

## **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 7. SLEEP Mode

Sleep mode is used to reduce power consumption.

|                       | Enter the Mode                           | Motor Output  | VREG<br>Voltage | Exit the Mode    |

|-----------------------|------------------------------------------|---------------|-----------------|------------------|

| SLEEP<br>SLEEP pin: H | Sleep pin: $L \Rightarrow H$ (Immediate) | All phase OFF | OFF             | Sleep pin: H ⇒ L |

In SLEEP mode, VREG voltage is OFF and all circuit protections cease to operate.

When SLEEP pin is changed from "L" to "H" while motor is running at high speed, please ensure that motor regenerated current, etc. does not exceed the absolute maximum rating of each pin and perform sufficient evaluation and verification to ensure this.

**AN44142A**

### **OPERATION** (Continued)

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 8. Protection Functions

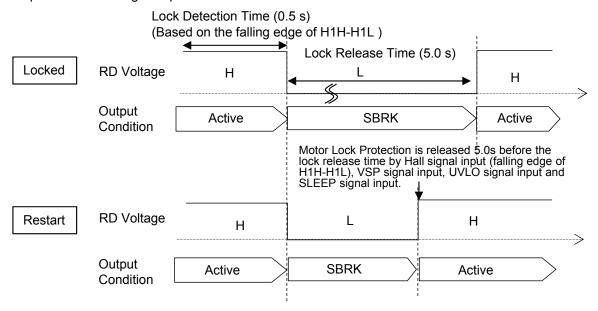

#### 8.1. Motor Lock Protection

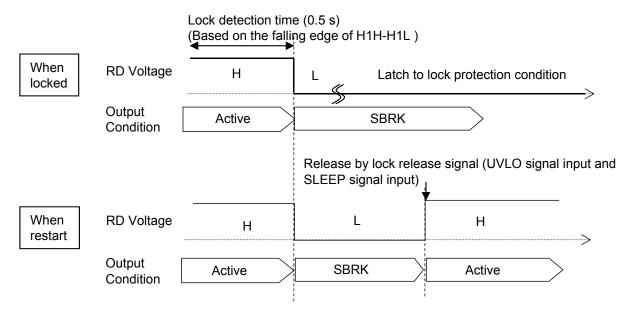

#### When RDS=L (Automatic reset mode)

When no signal for Hall signal input (Based on the falling edge of H1H-H1L) is continued for 0.5s or more, motor output turns OFF (short-brake) and Motor Lock Protection starts working (RD = L), and automatically resets after 5s elapses. Motor Lock Protection is released immediately by Hall signal input (falling edge of H1H-H1L), VSP signal input, UVLO signal input and SLEEP signal input.

#### When RDS=H (Latch mode)

When there is no hall signal (Based on the falling edge of H1H-H1L) for more than 0.5s, motor output will be OFF (Short-break), operation will switch and latch to RD=L protection. UVLO signal input and SLEEP signal input will immediately release the protection.

Page 29 of 48

# **Panasonic**

**AN44142A**

### **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 8. Protection Functions

### 8.2. Under Voltage Lock Out (UVLO)

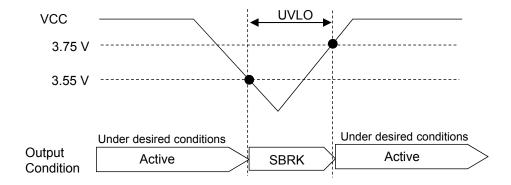

When VCC voltage drops to 3.55V and below, UVLO activates and motor output enters short-brake mode. When VCC voltage increases to 3.75V and above, UVLO is released.

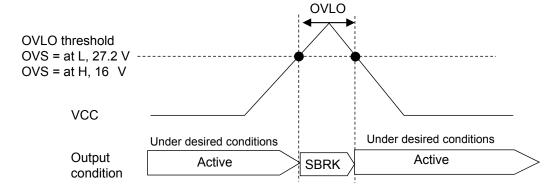

#### 8-3. Over Voltage Lock Out (OVLO)

When VCC voltage increases above threshold, OVLO activates and motor output enters short-brake mode. When VCC voltage drops below threshold, OVLO is released.

## **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 8. Protection Functions

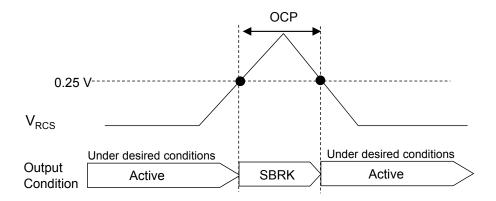

#### 8.4. Over Current Protection (OCP)

When RCS voltage increases to 0.25 V and above, OCP starts working and motor output enters short-brake mode. When RCS voltage decreases to 0.25 V and below, OCP is released.

Current value for over current detection can be set by varying the RCS pin detection resistor (RCS).

Over current protection current detection value

$$I_{PEAK} = 0.250V \times \frac{1}{RCS}$$

Eg:  $I_{PEAK}$  = To set to 1.0 A, set RCS to 0.250  $\Omega$  based on the below formula.

$$RCS = 0.250(V) \times \frac{1}{1.00(A)} = 0.250(\Omega)$$

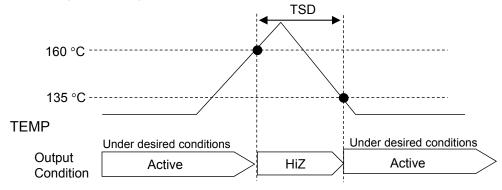

#### 8-5. Thermal Shut Down (TSD)

When IC junction temperature increases to 160°C and above, TSD activates and motor output turns OFF. When IC junction temperature drops to 135°C and below, TSD is released.

# **OPERATION (Continued)**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

#### 9. Control mode Table

Revised

| Pin | Pin   | Description                                                                                 | Voltage    |                               | Remarks                                                                                                                                                                                                      |

|-----|-------|---------------------------------------------------------------------------------------------|------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name  | Description                                                                                 | Open(Low)  | High                          | Remarks                                                                                                                                                                                                      |

| 3   | SLEEP | Sleep mode select                                                                           | Normal     | Sleep                         | SLEEP = "H" : Sleep mode (Motor output: OFF, VREG output: OFF) SLEEP = "L" : Normal mode  Note) For the setting range of SLEEP control voltage, refer to "SLEEP" under Electrical Characteristics on page 5. |

| 14  | ovs   | OVP Threshold select                                                                        | 27.2V      | 16V                           | Note: Please connect to VREG pin when set to High.                                                                                                                                                           |

| 15  | RDS   | Motor Lock mode select                                                                      | Auto reset | Disable auto<br>reset         | RDS = 'H': If there is no automatic reset after a specific time elapsed, release of the protection will only be by SLEEP = H or ULVO operation.  Note: Please connect to VREG pin when set to High.          |

| 16  | PS    | Phase Shift mode select                                                                     | Auto       | Constant                      | Note: Please connect to VREG pin when set to High.  Note: Do not switch during motor driving.                                                                                                                |

| 18  | SST   | Capacitor connection pin<br>for Soft Start triangle<br>wave oscillator frequency<br>setting | -          | Soft start control not in use | When soft start control is not in used, please connect SST pin to VREG pin. When soft start control is in used, please connect a capacitor to SST pin.                                                       |

| 19  | TRI   | Capacitor connection pin<br>for PWM triangle wave<br>oscillator frequency<br>setting        | -          | PWM input control             | When PWM input is used in speed control, please connect TRI pin to VREG pin. When DC input is used in speed control, please connect a capacitor to TRI pin.                                                  |

| Dim        | Voltage     |                                                                             |         |                    |         |                                                                                                                                                                                                           |

|------------|-------------|-----------------------------------------------------------------------------|---------|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Pin<br>Name | Description                                                                 | Low     | Open (Middle) High |         | Remarks                                                                                                                                                                                                   |

| 22         | FR          | Rotation direction select<br>(Forward/Reverse)<br>Short-brake control input | Forward | Short-<br>brake    | Reverse | Arbitrary direction is denoted as "Forward", and reverse direction is denoted as "Reverse".  Note) For the setting range of FR control voltage, refer to "FR" under Electrical Characteristics on page 7. |

| 17         | FGSEL       | FG pulse count select [ratio of hall signal cycle]                          | 1/3     | 1/2                | 1       | FG pulse output which is equivalent to arbitrary magnification of hall signal cycle  Note) For set range of FGSEL control voltage, refer to "FGSEL" of the Electrical Characteristics on page 7           |

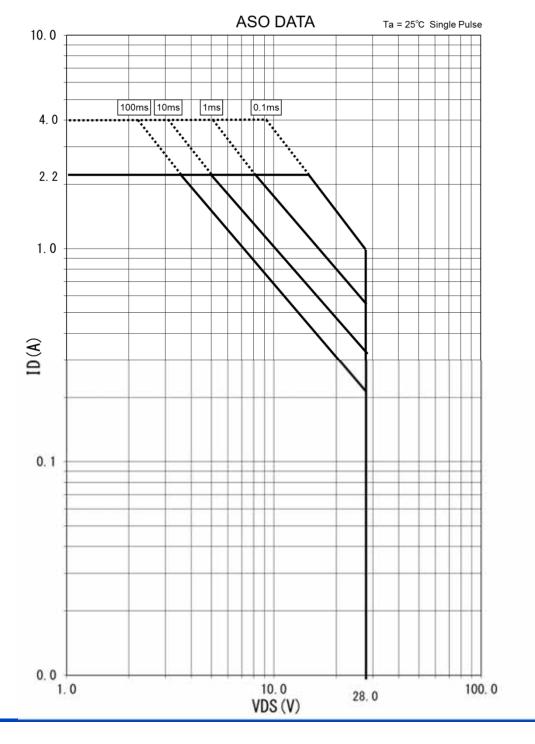

### **AREA OF SAFE OPERATION**

Note) The characteristics listed below are reference values derived from design of the IC and are not guaranteed.

This data is a single pulse data under Ta = 25  $^{\circ}$ C.

Under the actual usage, there could be Tj rising and more than one pulse applied.

Therefore, please use this data only as a reference.

Customer shall conduct sufficient reliability evaluation and verification on the set.

Page 33 of 48

## Pin equivalent circuit

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No. | Internal Circuit               | Impedance | Description                                                                          |

|------------|--------------------------------|-----------|--------------------------------------------------------------------------------------|

| 1, 2       | 1 VREG                         | 100Ω      | Pin1 (RD), Motor lock protection output signal pin. Pin2 (FG), FG output signal pin. |

| 3          | $3$ $2k\Omega$ $47k\Omega$ $m$ | 100kΩ     | Pin3(SLEEP),<br>Sleep select input pin.                                              |

Page 34 of 48

# Pin equivalent circuit (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No. | Internal Circuit | Impedance                        | Description                                                                          |

|------------|------------------|----------------------------------|--------------------------------------------------------------------------------------|

| 4          | 4 VCC            | 10Ω<br>(VREG<br>In<br>operation) | Pin4 (VREG)<br>Internal voltage regulator.                                           |

| 6,<br>12   |                  |                                  | Pin6(VPUMP), Charge pump output pin. Pin12(BC2), Pin to connect the boost capacitor. |

Page 35 of 48

**AN44142A**

# Pin equivalent circuit (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No.            | Internal Circuit | Impedance | Description                                                                                                              |

|-----------------------|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| 8,<br>9,<br>10,<br>11 | VREG 88 100 111  |           | Pin8 (W), 10 (V), 11 (U), Output channel pins to be connected to the motor Pin9 (RCS), Motor current sense resistor pin. |

Page 36 of 48

## Pin equivalent circuit (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No. | Internal Circuit              | Impedance | Description                                                  |

|------------|-------------------------------|-----------|--------------------------------------------------------------|

| 13         | VPUMP<br>VCC<br>13            | _         | Pin13 (BC1), Pin to connect the boost capacitor.             |

| 14         | 200kΩ<br>14<br>200kΩ<br>500kΩ | 1000kΩ    | Pin14(OVS), Over voltage protection threshold selection pin. |

Page 37 of 48

**AN44142A**

### Pin equivalent circuit (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No. | Internal Circuit       | Impedance | Description                                                                                                                                                                                                                                                                                   |

|------------|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15,<br>16  | VREG                   | 1000kΩ    | Pin15 (RDS), Motor lock protection input control pin.  Pin16(PS), Auto phase control setting input control pin.  • Connect pin to VREG voltage when there is a need to set to high level.                                                                                                     |

| 17         | VREG<br>563kΩ<br>520kΩ | _         | Pin17(FGSEL), FG signal input control pin.  Connect pin to VREG voltage when there is a need to set to high level.  When pin is used in open condition, please connect capacitor to pin to prevent noise from affecting operation. Please do verifications and evaluation for this condition. |

| 18         | 18                     |           | Pin18 (SST), Soft start triangle waveform using external capacitor to set the frequency.  Connect pin to VREG voltage when SST is not in used.                                                                                                                                                |

Page 38 of 48

### Pin equivalent circuit (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No. | Internal Circuit | Impedance | Description                                                                                                                     |

|------------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| 19         | 19               | _         | Pin19 (TRI), Connect a capacitor to TRI pin to set the frequency in DC linear mode.  • Connect pin to VREG voltage in PWM mode. |

| 20, 21     | 20 (21)          | Hi-Z      | Pin20 (N1H) , Hall amplifier + input terminal. Pin21(N1L) , Hall amplifier - input terminal.                                    |

Page 39 of 48

### Pin equivalent circuit (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed values.

| Pin<br>No. | Internal Circuit                                 | Impedance | Description                                                                                                                                                                                    |

|------------|--------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | 22 4kΩ 500kΩ ——————————————————————————————————— | 504kΩ     | Pin22 (FR),<br>Forward / reverse rotation and short<br>brake control input pin.                                                                                                                |

| 23         | 23<br>500kΩ<br>500kΩ                             | 1000kΩ    | Pin23 (VSPL), In DC input mode, speed is limited by this input pin. In PWM input mode, VSPL can either be connected to GND or in open state. However it is recommended to be connected to GND. |

| 24         | 24<br>165kΩ<br>165kΩ                             | 330kΩ     | Pin24 (VSP), Input pin for speed required In PWM input mode, please use the high and low level as required in the specifications.                                                              |

Page 40 of 48

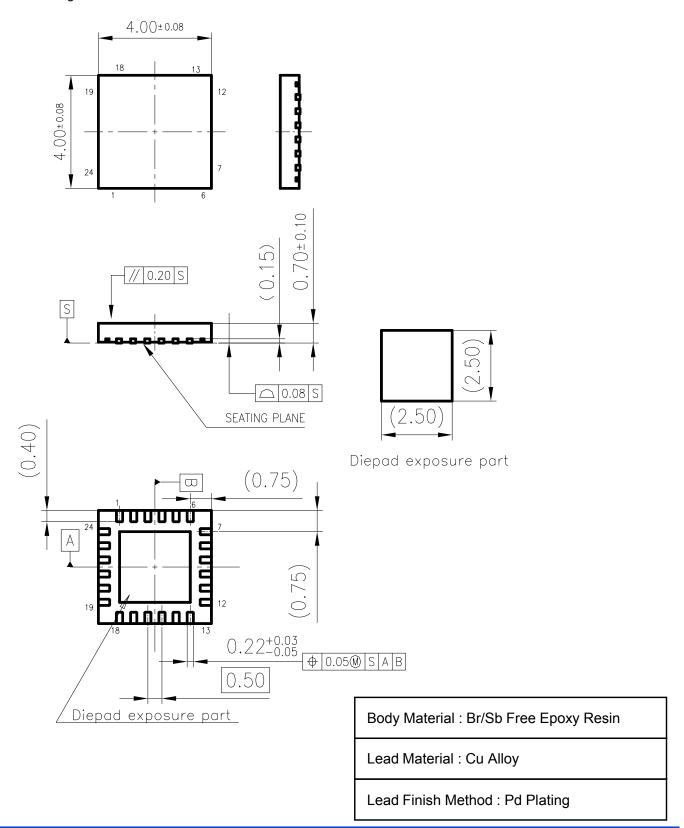

#### PACKAGE INFORMATION

#### **Outline Drawing**

Package code: HQFN024-A-0404AZ Unit: mm

Page 41 of 48

#### PACKAGE INFORMATION (Continued)

Power Dissipation (Technical Report)

Package code: HQFN024-A-0404AZ

### **PACKAGE INFORMATION (Continued)**

Power Dissipation (Supplementary Explanation)

#### [Experiment environment]

Power Dissipation (Technical Report) is a result in the experiment environment of SEMI standard conformity.

(Ambient air temperature (Ta) is 25 degrees C)

#### [Supplementary information of PWB to be used for measurement]

The supplement of PWB information for Power Dissipation data (Technical Report) are shown below.

| Indication  | Total Layer | Resin Material |

|-------------|-------------|----------------|

| Glass-Epoxy | 1-layer     | FR-4           |

| 2-layer     | 2-layer     | FR-4           |

| 4-layer     | 4-layer     | FR-4           |

#### [Notes about Power Dissipation (Thermal Resistance)]

Power Dissipation value (Thermal Resistance) depend on the conditions of the surroundings, such as specification of PWB, mounting condition and ambient temperature. (Power Dissipation (Thermal Resistance) is not a fixed value.)

The Power Dissipation value (Technical Report) is the result based on evaluation under specified conditions (Evaluation environment under SEMI International Standards). Power Dissipation value (Thermal resistance) depends and changes with the environmental conditions.

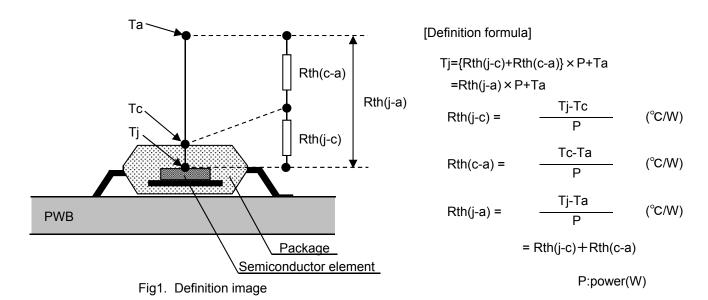

#### [Definition of each temperature and thermal resistance]

Ta : Ambient air temperature

\*Air temperature is defined as temperature separated from the heating elements and not affected by convection, radiation, etc.

Tc : Temperature near the center of a package surface. Opposite side of the package mounting surface.

Tj : Semiconductor element surface temperature (Junction temperature.)

Rth(j-c): Thermal resistance (Temperature difference per 1 Watts) between the semiconductor element junction part and the package surface.

Rth(c-a): Thermal resistance (Temperature difference per 1 Watts) between the package surface and ambient air temperature.

Rth(j-a): Thermal resistance (Temperature difference per 1 Watts) between a semiconductor element junction part and ambient air temperature.

Page 43 of 48

Doc No. TA4-EA-06255 Revision. 2

## **Panasonic**

**AN44142A**

#### **IMPORTANT NOTICE**

- 1. When using the IC for new models, verify the safety including the long-term reliability for each product.

- When the application system is designed by using this IC, please confirm the notes in this book. Please read the notes to descriptions and the usage notes in the book.

- 3. This IC is intended to be used for general electronic equipment.

Consult our sales staff in advance for information on the following applications: Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body. Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Traffic control equipment (such as for automotive, airplane, train, and ship)

- (3) Medical equipment for life support

- (4) Submarine transponder

- (5) Control equipment for power plant

- (6) Disaster prevention and security device

- (7) Weapon

- (8) Others: Applications of which reliability equivalent to (1) to (7) is required

Our company shall not be held responsible for any damage incurred as a result of or in connection with the IC being used for any special application, unless our company agrees to the use of such special application.

However, for the IC which we designate as products for automotive use, it is possible to be used for automotive.

- 4. This IC is neither designed nor intended for use in automotive applications or environments unless the IC is designated by our company to be used in automotive applications.

- Our company shall not be held responsible for any damage incurred by customers or any third party as a result of or in connection with the IC being used in automotive application, unless our company agrees to such application in this book.

- 5. Please use this IC in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Our company shall not be held responsible for any damage incurred as a result of our IC being used by our customers, not complying with the applicable laws and regulations.

- 6. Pay attention to the direction of the IC. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might be damaged.

- 7. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 8. Perform visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as solder-bridge between the pins of the IC. Also, perform full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the IC during transportation.

- 9. Take notice in the use of this IC that it might be damaged when an abnormal state occurs such as output pin-VCC short (Power supply fault), output pin-GND short (Ground fault), or output-to-output-pin short (load short). Safety measures such as installation of fuses are recommended because the extent of the above-mentioned damage will depend on the current capability of the power supply.

- Although the following pins comes with short circuit protection function, the protection may be damaged depending on the VCC voltage. Pins with short circuit protection function: Pin11(U), Pin10(V) and Pin8(W).

- 10. The protection circuit is for maintaining safety against abnormal operation.

- When sudden voltage or current change is applied to the pin, it may exceed the designated voltage and current level and therefore, customer shall perform sufficient evaluation and verification to ensure these are not exceeded in the usage.

- Especially for the thermal protection circuit, if the area of safe operation or the absolute maximum rating is momentarily exceeded due to output pin to VCC short (Power supply fault), or output pin to GND short (Ground fault), the IC might be damaged before the thermal protection circuit could operate.

- 11. Unless specified in the product specifications, make sure that negative voltage or excessive voltage are not applied to the pins because the IC might be damaged, which could happen due to negative voltage or excessive voltage generated during the ON and OFF timing when the inductive load of a motor coil or actuator coils of optical pick-up is being driven.

- 12. Product which has specified ASO (Area of Safe Operation) should be operated in ASO

- 13. Verify the risks which might be caused by the malfunctions of external components.

Doc No. TA4-EA-06255 Revision. 2

## **Panasonic**

**AN44142A**

#### **IMPORTANT NOTICE (Continued)**

- 14. Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process.

- Dip soldering is not recommended.

- 16. Connect the metallic plate (fin) on the back side of the IC to the GND potential. The thermal resistance and electrical characteristics are guaranteed only when the metallic plate (fin) is connected with the GND potential.

- 17. Follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

- 18. When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment, etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damage, for example, by using the products.

Doc No. TA4-EA-06255 Revision. 2

## **Panasonic**

**AN44142A**

#### **USAGE PRECAUTIONS**

- Below are the precautions to take note when using this IC.

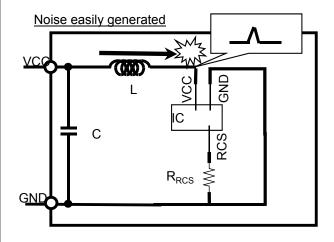

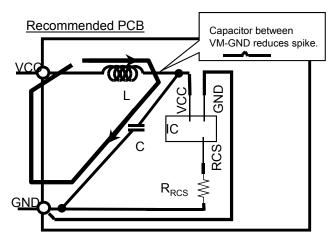

- 1. Apply power supply with low impedance to VCC and connect bypass capacitor near to the IC.

- 2. When designing PCB pattern for RCS pin (Pin 9), place a resistor for current detection (R<sub>RCS</sub>) close to the IC. The setting value for over current protection may fluctuate due to the impedance of wiring pattern between RCS pin and the RCS resistor.

- 3. When VCC is input, VCC voltage will start to rise to the designated voltage. However, at the same time, motor driver starts driving and when this results in decreases the VCC voltage, it may disrupt the normal start-up. Therefore, please conduct sufficient evaluation and verification to ensure the power supply current.

- 4. The minimum input amplitude of hall signal comparator should be designed in consideration of tolerances and temperature characteristics of the hall element, so that it will not result in failure to the motor operation.

- 5. In the 1-HALL-sensor system motor driver adopted in this IC, energization pattern of a cycle is generated based on previous 1-cycle of a HALL input signal. Therefore, when the acceleration of a motor is very high, the motor may be unable to accelerate normally because of the big difference in cycle between the generated energization pattern and the motor rotation. When using a motor with very high speed acceleration, ensure to conduct sufficient technical evaluation and examination on the sudden acceleration from low rotation.

When the above acceleration problems arises, the problem may be improved by putting the speed to zero first and then input the required speed. Please conduct sufficient evaluation before use.

(When HALL input signal of below 10Hz is inputted to this IC, putting the speed to zero and then input the required speed again will restart the rotation.)

In addition, when using the VSPL function, it is not possible to input zero to the speed and therefore, please take note when using the lower limit rotation constant and conduct sufficient evaluation and examination on the sudden acceleration from low rotation.