PB005002-0601

## Z16C32

# IUSC<sup>TM</sup> INTEGRATED UNIVERSAL SERIAL CONTROLLER

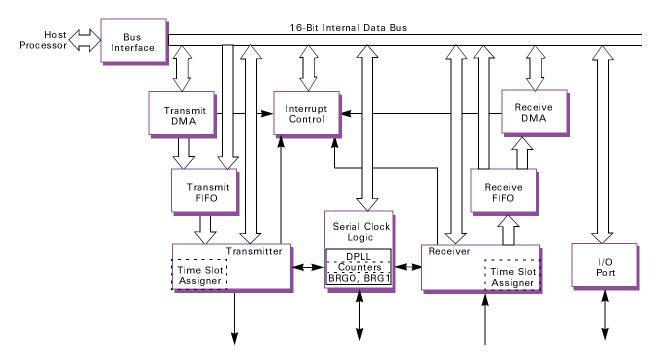

#### PRODUCT BLOCK DIAGRAM

| CTR  | ı        | 3RG         | DF | LL      | BRG | ì    | CTR |

|------|----------|-------------|----|---------|-----|------|-----|

| DMA  | Transmit |             |    | Receive |     | DMA  |     |

| FIFO |          | Logic       |    | Logic   |     | FIFO |     |

| CRC  |          | Modem Logic |    |         | (   | CRC  |     |

#### **FEATURES**

- Single full-duplex, 0 to 20 Mbps channel, with two baud rate generators (BRG) and one digital phase locked loop (DPLL) for clock recovery

- Two full-capacity 20 MHz DMA channels, each with 32-Bit addressing and 16-bit data transfers

- 32-byte data FIFO's for each receiver and transmitter

- ASYNC Mode with:

- 1–8 bits/character; 1/16 to 2 stop bits/ character in 1/16 bit increments

- programmable clock factor

- Break detect and generation

- Odd, Even, Mark, Space, no parity and framing error detection

- Byte-oriented Synchronous mode with

- 1–8 bits/character

- 2- to 16-bit programmable SYNC character

- 16- or 32-bit CRC

- Transmit-to-receive slaving (for X.21)

- HDLC/SDLC mode with:

- 8-bit address compare

- 16- or 32-bit CRC

- Selectable number of flags between back-toback frames

- External character synchronous mode for receive

- Receive and transmit time slot assigners for ISDN, T1, and E1 (CEPT) applications

#### **GENERAL DESCRIPTION**

The Z16C32 IUSCTM (Integrated Universal Serial Controller) is a multi-protocol data communications device with an on-chip dual-channel DMA. The integration of high-speed serial communications and high-performance DMA channels promote higher data throughput than can be achieved with discrete serial/DMA chip combinations.

In addition to using the Z16C32 IUSC for just reduced chip count and board space economy, the DMA and serial channel intercommunication also offers application benefits. For example, events such as the reception of the end of a HDLC frame is internally communicated from the serial controller to the DMA, so that each frame can be written into a separate memory buffer. The buffer chaining capabilities, ring buffer support, automated frame status/control blocks, and buffer termination at the end of the frame combine to significantly reduce CPU overhead.

The IUSC is configured under software to satisfy a wide variety of serial communication applications. The 20 Mbps data rate and multi-protocol support make this device ideal for applications in today's dynamic environment of changing specifications and increasing speed. The many programmable features allow the user to tune the device response to meet a variety of system requirements. The IUSC contains many sophisticated internal functions, including two baud rate generators, a digital phase-locked loop, character counters, and 32-byte FIFOs for both the receiver and the transmitter.

The on-chip DMA channels allow high speed data transfers for both the receiver and the transmitter. The IUSC supports automatic status and control transfer through DMA, and allows initialization of the serial controller under DMA control. Each DMA channel can do a 16-bit transfer in as little as three 50 ns clock cycles, and can generate addresses compatible with 32-, 24- or 16-bit memory ranges.

The CPU bus interface is designed for use with any conventional multiplexed or non-multiplexed bus from manufacturers of CISC and RISC processors including Intel, Motorola, and ZiLOG. The bus interface is configurable for 16-bit data and 8-bit data to support multiplexed or non-multiplexed busses.

Interrupts are supported by a daisy-chain hierarchy within the serial channel and between the serial channel and the DMA. The IUSC supports Pulsed, Double Pulsed, and Status Interrupt Acknowledge cycles.

#### **APPLICATIONS AND SUPPORT TOOLS**

The following development tools are available for the programming and debug of this device:

Z8018600ZCO evaluation board

### **RELATED PRODUCTS**

Similar communication controllers available from ZiLOG's SCC family include:

| Z8030  | NMOS SCC (Serial Communication        |

|--------|---------------------------------------|

| Z8530  | Controller).                          |

| Z80C30 | CMOS SCC (Serial Communication        |

| Z85C30 | Controller).                          |

| Z16C35 | ISCC Single channel SCC with built-in |

|        | DMA controllers.                      |

| Z80230 | ESCC (Enhanced Serial                 |

| Z85230 | Communication Controller).            |

| Z16C30 | USC (Universal Serial controller).    |

#### **ORDERING INFORMATION**

| PSI         | Description             |

|-------------|-------------------------|

| Z16C3220FSC | 80-pin PQFP IUSC device |

| Z16C3220VSC | 68-pin PLCC IUSC device |

| Z8018600ZCO | 80186 Evaluation board  |

To order, contact your nearest ZiLOG sales office or send an email to: csupport@zilog.com.

©2001 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.