# Switch-Mode Single Cell Li-Ion Battery Charger with USB-OTG

#### **General Description**

The RT9458 is a switch-mode single cell Li-lon/Li-Polymer battery charger for portable applications. It integrates a synchronous PWM controller, power MOSFETs, input current sensing, high accuracy voltage regulation and charge termination circuits. The RT9458 also features USB On-The-Go (OTG).

The RT9458 optimizes the charging task by using a control algorithm to vary the charge rate via different modes, including pre-charge mode, fast charge mode, and constant voltage mode. The key charge parameters can be programmed via the I<sup>2</sup>C interface. The RT9458 resumes the charge cycle whenever the battery voltage falls below an internal threshold and automatically enters sleep mode when the input power supply is removed.

Other features include under-voltage protection, overvoltage protection, thermal regulation and reverse leakage protection.

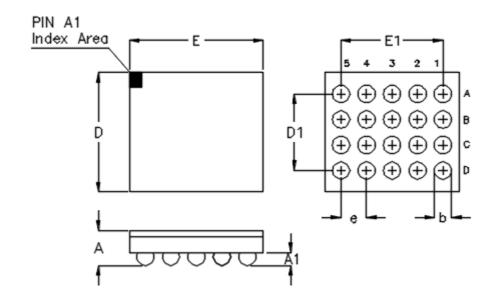

The RT9458 is available in the small WL-CSP-20B 2.1x1.87 (BSC) package.

# **Marking Information**

4E : Product Code W : Date Code

#### **Features**

- Support Quick Start for Charger

- High Accuracy Voltage/Current Regulation

- Input Current Regulation : 100mA/500mA/700mA/

1A

- Minimum Input Voltage Regulation : 4.1V to 4.7V

Per 0.1V Step

- Charge Voltage Regulation Accuracy: ±1% (0 to 85°C)

- Charge Current Regulation Accuracy: ±5%

- Built-In Input Current Sensing and Limiting

- Integrated Power MOSFETS for up to 1.55A Charge Rate

- Integrated Sensing Resistors for Charging Current Sensing

- Synchronous 1.5MHz Fixed Frequency PWM Controller with up to 95% Duty Cycle

- Reverse Leakage Protection to Prevent Battery Drainage

- Thermal Regulation and Protection

- Over-Temperature Protection

- Input Over-Voltage Protection

- IRQ Output for Communication with I<sup>2</sup>C

- Automatic Charging

- RoHS Compliant and Halogen Free

# **Applications**

- Cellular Telephones

- Personal Information Appliances

- MP3 Players

- Portable Instruments

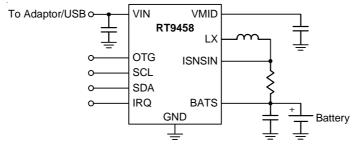

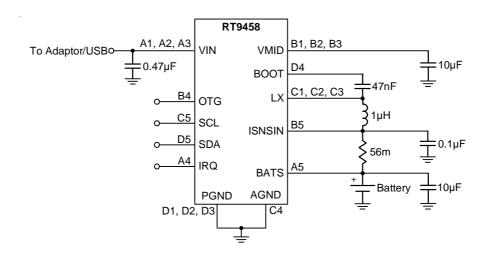

# **Simplified Application Circuit**

# **Ordering Information**

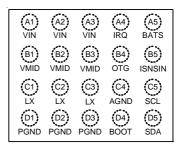

# **Pin Configuration**

RT9458□

└-Package Type

WSC: WL-CSP-20B 2.1x1.87 (BSC)

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

(TOP VIEW)

WL-CSP-20B 2.1x1.87 (BSC)

## **Functional Pin Description**

| Pin No.    | Pin Name | Pin Function                                                                         |

|------------|----------|--------------------------------------------------------------------------------------|

| A1, A2, A3 | VIN      | Power input.                                                                         |

| A4         | IRQ      | IRQ output node. Open-drain output, connect a 10kΩ pull up resistor.                 |

| A5         | BATS     | Feedback voltage input for battery.                                                  |

| B1, B2, B3 | VMID     | Connection point between reverse blocking MOSFET and high-side MOSFET.               |

| B4         | отб      | Boost mode control input or current regulation setting for average input current.    |

| B5         | ISNSIN   | Charge current sense input.                                                          |

| C1, C2, C3 | LX       | Switch node.                                                                         |

| C4         | AGND     | Analog ground.                                                                       |

| C5         | SCL      | Clock input for $I^2$ C. Open-drain output, connect a $10k\Omega$ pull-up resistor.  |

| D1, D2, D3 | PGND     | Power ground for switching charger.                                                  |

| D4         | воот     | Bootstrap supply for high-side MOSFET. Connect a capacitor between BOOT and LX.      |

| D5         | SDA      | Data input for I $^2$ C. Open-drain output, connect a 10k $\Omega$ pull-up resistor. |

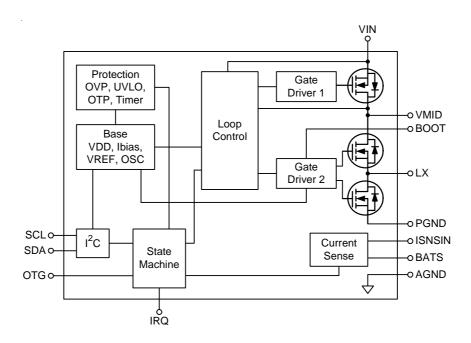

# **Functional Block Diagram**

# **Operation**

The RT9458 is a switch mode charger with USB-OTG support for single cell Li-lon battery in portable applications.

#### **Base Circuits**

Base circuits provide the internal power, VDD and reference voltage and bias current.

#### **Current Sense**

Current sense circuit regulates the output current up to 1.5A to battery

#### **Protection Circuits**

The protection block includes the OVP, UVLO, OTP, Timer and other circuits. It turns off the charging when the charger IC or input power is in abnormal level.

#### **Loop Controller and PWM and Driver**

The multi-loop controller controls the PWM signal during the charging process. The PWM circuit controls the power stage through the driver. It makes sure that the battery is well-charged with suitable current, voltage and dietemperature.

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is used to program the charging parameters, ex: output current and output voltage.

#### **State Machine**

The State Machine controls the operation of the switching charger and outputs the interrupt via the IRQ pin if there is any fault be triggered.

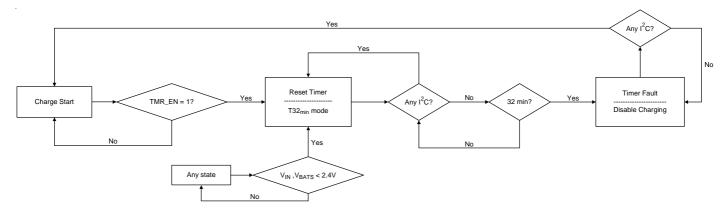

#### **Flow Charts**

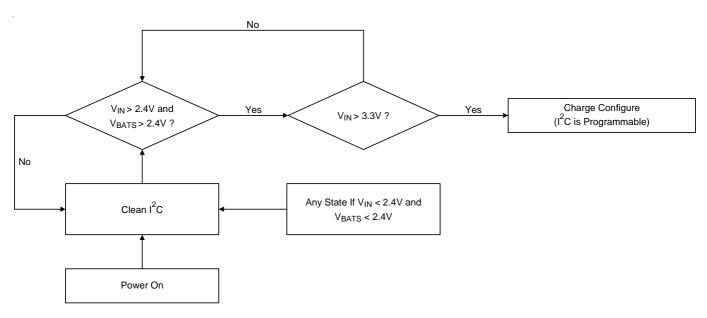

#### **POR Reset**

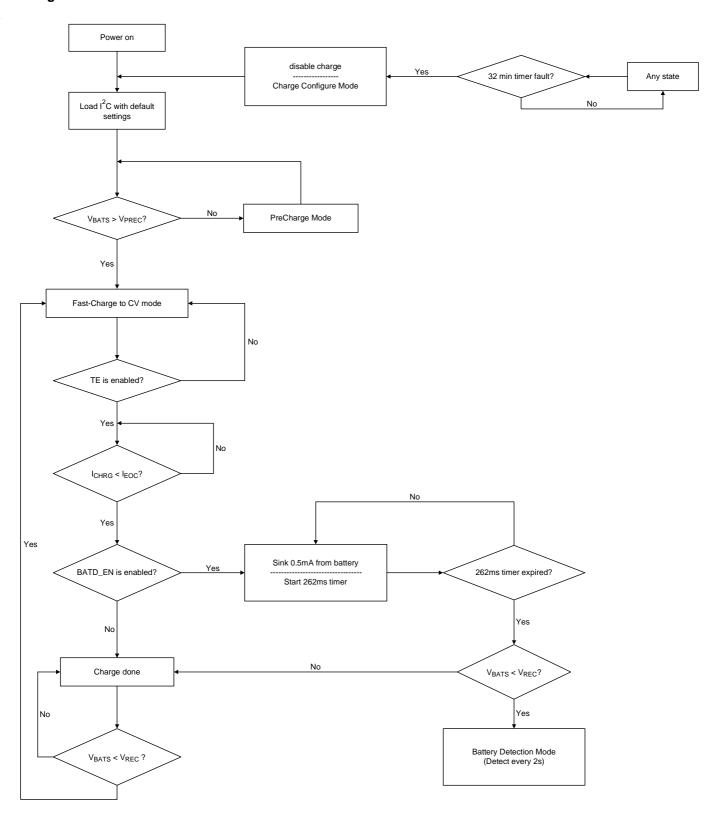

#### **Charger Flow**

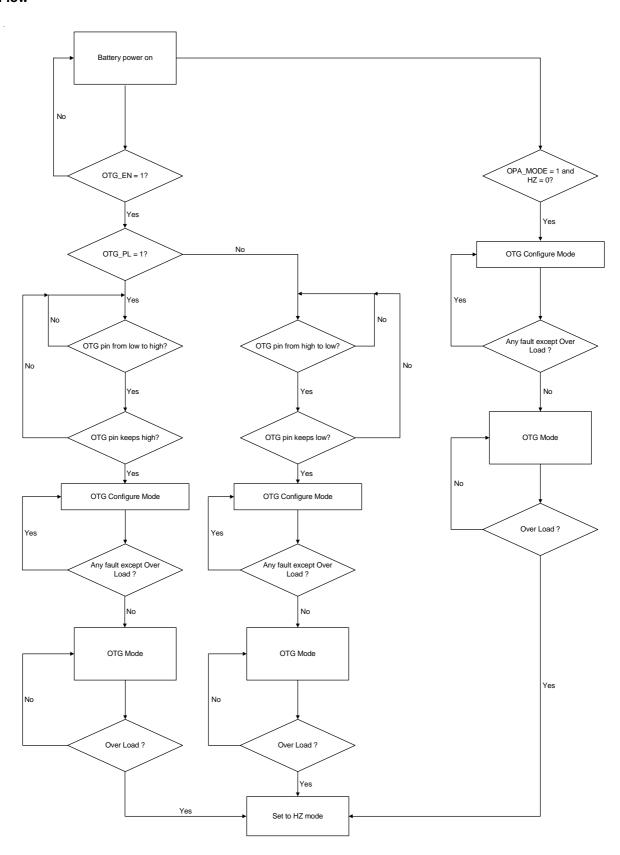

#### **OTG Flow**

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VIN                                                   | 0.3V to 20V      |

|-----------------------------------------------------------------------------|------------------|

| • VMID, BOOT                                                                | 0.3V to 20V      |

| • LX                                                                        | 0.3V to 10V      |

| • MID – VIN, BOOT – LX                                                      | 0.3V to 6V       |

| • Other Pins                                                                | 0.3V to 6V       |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                  |

| WL-CSP-20B 2.1x1.87 (BSC)                                                   | - 2.45W          |

| Package Thermal Resistance (Note 2)                                         |                  |

| WL-CSP-20B 2.1x1.87 (BSC), $\theta_{JA}$                                    | - 40.8°C/W       |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C          |

| • Junction Temperature                                                      |                  |

| Storage Temperature Range                                                   | - −65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                  |

| HBM (Human Body Model)                                                      | - 2kV            |

|                                                                             |                  |

| Recommended Operating Conditions (Note 4)                                   |                  |

# • Supply Input Voltage. VIN ------ 4.3V to 6V

| • | Cappiy input voitage, viiv | 4.0 0 10 0 0   |

|---|----------------------------|----------------|

| • | Junction Temperature Range | -40°C to 125°C |

|   |                            |                |

• Ambient Temperature Range ------ -40°C to 85°C

#### **Electrical Characteristics**

$(V_{IN}=5V,\,V_{BAT}=4.2V,\,L=1\mu H,\,C_{IN}=0.47\mu F,\,C_{BATS}=10\mu F,\,T_{A}=25^{\circ}C,\,unless\,\,otherwise\,\,specified)$

| Parameter                                                         | Symbol               | Test Conditions                                                        | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------|----------------------|------------------------------------------------------------------------|------|------|------|------|

| Protection                                                        |                      |                                                                        |      |      |      |      |

| V <sub>IN</sub> OVP Threshold Voltage                             | VINOVP               | V <sub>IN</sub> rising                                                 | 6.4  | 6.7  | 7    | V    |

| V <sub>IN</sub> OVP Hysteresis                                    | VINOVP_Hys           |                                                                        |      | 150  |      | mV   |

| Battery OVP                                                       | Vватоvр              | (Battery OVP - Voreg) / Voreg                                          | 110  | 117  | 124  | %    |

| Battery OVP Hysteresis                                            | VBATOVP_Hys          |                                                                        |      | 10   |      | %    |

| Over-Temperature Protection                                       | OTP                  |                                                                        |      | 165  |      | °C   |

| OTP Hysteresis                                                    | T <sub>OTP_Hys</sub> |                                                                        |      | 10   |      | °C   |

| Thermal Regulation Threshold                                      |                      | Charge current begins to reduce                                        |      | 120  |      | °C   |

| Sleep Mode Comparator                                             |                      |                                                                        |      |      |      |      |

| Sleep-Mode Entry Threshold VIN - VBATS                            | V <sub>SLP</sub>     | 2.5V < V <sub>BATS</sub> < V <sub>OREG</sub> , V <sub>IN</sub> falling | 0    | 0.04 | 0.1  | V    |

| Sleep-Mode Exit Hysteresis<br>V <sub>IN</sub> – V <sub>BATS</sub> | VSLPEXIT             | 2.5V < V <sub>BATS</sub> < V <sub>OREG</sub> , V <sub>IN</sub> rising  | 40   | 100  | 200  | mV   |

| Sleep-Mode Deglitch Time                                          | tslp                 | VIN rising above VSLP + VSLPEXIT                                       |      | 128  |      | ms   |

| Under-Voltage Lockout Thre                                        | shold                |                                                                        |      |      |      |      |

| IC Active Threshold Voltage                                       | V <sub>U</sub> VLO   | V <sub>IN</sub> rising                                                 | 3.05 | 3.3  | 3.55 | V    |

| IC Active Hysteresis                                              | $\Delta V_{UVLO}$    | V <sub>IN</sub> falling from UVLO                                      |      | 150  |      | mV   |

Copyright@2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS9458-01 December 2016 www.richtek.com

| Parameter Symbol                                                            |                        | Test Conditions                                                             | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| Input Currents                                                              |                        | •                                                                           |      |      |      |      |

|                                                                             |                        | PWM switching, ICHRG = IBAT = 0mA                                           |      | 10   |      | mA   |

| VIN Supply Current                                                          | IQ                     | PWM is not switching. ICHRG = IBAT = 0mA                                    |      |      | 5    | mA   |

|                                                                             |                        | High impendence mode                                                        |      |      | 150  | μΑ   |

| Leakage Current from Battery                                                | I <sub>BAT</sub>       | V <sub>BATS</sub> = 4.2V, V <sub>IN</sub> = 0V, charger off                 |      |      | 15   | μА   |

| Leakage from Battery to VBUS                                                | I <sub>BAT_LEK</sub>   | HZ mode = 1, V <sub>BAT</sub> = 4.2V                                        |      | 0.2  | 5    | μΑ   |

| Input Power Regulation                                                      |                        | •                                                                           |      |      |      |      |

| Minimum Input Voltage<br>Regulation                                         | VMIVR                  | I <sup>2</sup> C programmable per 0.1V                                      | 4.1  |      | 4.7  | V    |

| VMIVR Accuracy                                                              | V <sub>MI</sub> VR_ACC |                                                                             | -3   |      | 3    | %    |

| Average Input Current                                                       | 1                      | USB charge mode, I <sub>AICR</sub> = 100mA                                  | 80   | 90   | 100  | A    |

| Regulation Accuracy                                                         | IAICR                  | USB charge mode, I <sub>AICR</sub> = 500mA                                  | 440  | 470  | 500  | mA   |

| Battery Voltage Regulation                                                  |                        |                                                                             |      |      |      |      |

| Battery Voltage Regulation                                                  | Voreg                  | I <sup>2</sup> C programmable per 20mV                                      | 3.5  |      | 4.44 | V    |

| V <sub>OREG</sub> Accuracy                                                  | Voreg_acc              | 0 to 85°C                                                                   | -1   |      | 1    | %    |

| Initial CV Voltage when V <sub>BUS</sub><br>Plug in Before toN_SET          | VCV_INI                | V <sub>IN</sub> = 5V, without connect battery                               |      | 4.35 |      | V    |

| Deglitch Time when CV is<br>Determined by I2C Setting<br>After VBUS Plug in | ton_set                | V <sub>IN</sub> = 5V, without connect battery                               |      | 1    |      | s    |

| Re-Charge Threshold                                                         | VREC                   | VBATS falling, below VOREG                                                  | 100  | 150  | 200  | mV   |

| Re-Charge Deglitch                                                          | t <sub>REC</sub>       |                                                                             |      | 128  |      | ms   |

| Charging Current Regulation                                                 | 1                      |                                                                             |      |      |      |      |

| Output Charging Current                                                     | I <sub>CHRG</sub>      | I <sup>2</sup> C programmable per 0.15A                                     | 0.5  |      | 1.55 | Α    |

| I <sub>CHRG</sub> Accuracy                                                  | I <sub>CHRG_ACC</sub>  | 500mA to 1.55A                                                              | -5   |      | 5    | %    |

| Pre-Charge Threshold                                                        | V <sub>PREC</sub>      | I <sup>2</sup> C programmable per 0.2V                                      | 2    |      | 3    | V    |

| V <sub>PREC</sub> Accuracy                                                  | V <sub>PREC_ACC</sub>  |                                                                             | -5   |      | 5    | %    |

| Pre-Charge Current                                                          | IPREC                  | I <sup>2</sup> C programmable per 20mA                                      | 20   |      | 60   | mA   |

| I <sub>PREC</sub> Accuracy                                                  | IPREC_ACC              |                                                                             | -50  |      | 50   | %    |

| Charge Termination Detection                                                | n                      | •                                                                           | •    |      |      |      |

| End of Charge Current                                                       | I <sub>EOC</sub>       | I <sup>2</sup> C programmable per 50mA                                      | 50   |      | 400  | mA   |

| Fixed I <sub>EOC</sub>                                                      | IEOC_Fix               | As I <sub>AICR</sub> = 100mA                                                |      | 50   |      | mA   |

| Deglitch Time for EOC                                                       | tEOC                   | I <sub>CHRG</sub> < I <sub>EOC</sub> , V <sub>BATS</sub> > V <sub>REC</sub> |      | 32   |      | μS   |

|                                                                             | IEOC_ACC1              | $I_{EOC}$ = 50mA to 100mA<br>(RSENSE = 56m $\Omega$ )                       | -15  |      | 15   |      |

| End of Charge Current<br>Accuracy                                           | I <sub>EOC_ACC2</sub>  | $I_{EOC}$ = 100mA to 250mA (R <sub>SENSE</sub> = 56mΩ)                      | -10  |      | 10   | %    |

|                                                                             | IEOC_ACC3              | $I_{EOC}$ = 250mA to 400mA (Rsense = 56m $\Omega$ )                         | -5.5 |      | 5.5  |      |

| Parameter                        | Test Conditions | Min                                                   | Тур   | Max  | Unit |     |

|----------------------------------|-----------------|-------------------------------------------------------|-------|------|------|-----|

| PWM                              | •               |                                                       |       |      |      |     |

| Internal MOSFET<br>On-Resistance | R <sub>DS</sub> | From VIN to LX, as IAICR[1:0] = 11                    |       | 185  | 222  | mΩ  |

| Internal MOSFET<br>On-Resistance |                 | From LX to PGND                                       | 1     | 90   | 100  | mΩ  |

| Charging Efficiency              |                 | $V_{IN} = 5V$ , $V_{BATS} = 4V$ , and $I_{CHRG} = 1A$ | I     | 90   |      | %   |

| Oscillator Frequency             | osc             |                                                       |       | 1.5  |      | MHz |

| Frequency Accuracy               |                 |                                                       | -10   |      | 10   | %   |

| Maximum Duty Cycle               |                 | At minimum voltage input                              |       | 95   |      | %   |

| Minimum Duty Cycle               |                 |                                                       | 0     |      |      | %   |

| Peak OCP as Charger Mode         | ICHRGOCP        |                                                       | 2     | 2.75 | 3.5  | Α   |

| Boost Mode Operation             |                 | •                                                     |       |      | I    | I   |

| Output Voltage Level             | VотG            | To VMID, I <sup>2</sup> C programmable per 25mV       | 4.425 |      | 5.6  | V   |

| Output Voltage Accuracy          | Votg_acc        |                                                       | -3    |      | 3    | %   |

| Efficiency                       |                 | $V_{IN} = 5V$ , $V_{BATS} = 4V$ , and $I_{IN} = 0.4A$ | -     | 92.5 |      | %   |

| MAX Output Current               |                 | V <sub>BATS</sub> = 3.7V, V <sub>IN</sub> = 5V        | 1     | 1    |      | Α   |

| Peak Over Current Protection     |                 | $V_{BATS} = 3.7V$                                     | 2.5   | 3.25 | 4    | Α   |

| V <sub>IN</sub> OVP as OTG Boost |                 |                                                       |       | 6    |      | V   |

| V <sub>IN</sub> OVP Hysteresis   |                 |                                                       |       | 200  |      | mV  |

| Minimum Battery Voltage for      | VBATMIN         | As boost start-up                                     | 2.75  | 2.9  | 3.05 | V   |

| Boost                            | VBATIVIIN       | During boost mode                                     | 2.35  | 2.5  | 2.65 | v   |

| I <sup>2</sup> C Characteristics |                 |                                                       |       |      |      |     |

| Output Low Voltage               | VoL             | I <sub>DS</sub> = 10mA                                |       |      | 0.4  | V   |

| SCL, SDA Input Threshold         | ViH             | Logic high threshold                                  | 1.3   |      |      | V   |

| Voltage                          | V <sub>IL</sub> | Logic low threshold                                   |       |      | 0.4  | ٧   |

| SCL Clock                        |                 |                                                       |       |      | 400  | kHz |

| Load Capacitance                 | CLOAD           | VPULL_UP = 1.8V                                       |       |      | 1    | рF  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}\text{C}$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

# **Typical Application Circuit**

#### Below are recommended capacitor and inductor information

| Pin    | Description     | Part Number       | Package | Manufacture |

|--------|-----------------|-------------------|---------|-------------|

| VIN    | 0.47μF/25V/X5R  | GRM155R61E474K01  | 0402    | muRata      |

| VMID   | 10μF/16V/X5R    | GRM188R61C106KAAL | 0603    | muRata      |

| BOOT   | 0.047μF/50V/X7R | GCM155R71H473KE01 | 0402    | muRata      |

| ISNSIN | 0.1μF/10V/X5R   | GRM155R61A104KA01 | 0402    | muRata      |

| BATS   | 10μF/6.3V/X5R   | GRM185R60J106ME15 | 0603    | muRata      |

| ISNSIN | 56mΩ/1%         | RL10FTNR056       | 0805    | TA-I        |

| LX     | 1Uh/20%         | DFE252012-H-1R0M  | 252012  | TOKO        |

### **Applications Information**

The RT9458 is an integrated solution of single-cell Li-ion and Li-polymer battery charger for portable applications. The part integrates a synchronous PWM controller with power MOSFETs to provide input voltage MIVR (Minimum Input Voltage Regulation), input current sensing, high accuracy current and voltage regulation, and charge termination in a small package for space limited devices. The part also features USB OTG (On-The-Go).

The RT9458 has three operation modes: charge mode, boost mode (USB OTG), and high impedance mode. In charge mode, the RT9458 supports a precision charging system for single cell. In boost mode, the RT9458 works as the Boost converter and boosts the voltage from battery to VIN pin for sourcing the OTG devices. In high impedance mode, the RT9458 stops charging or boosting and operates in a mode with low current from VIN or battery to reduce the power consumption when the portable device is in standby mode.

Notice that the RT9458 does not integrate input power source (AC adapter or USB input) detection. Thus, the RT9458 does not set the charge current automatically. The charge current needs to be set via I<sup>2</sup>C interface by the host. The RT9458 application mechanism and I<sup>2</sup>C compatible interface are introduced in later sections. The slave address for this device is "1101010".

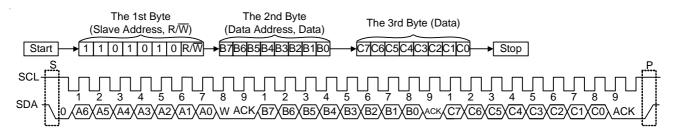

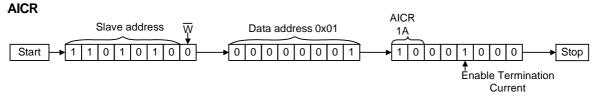

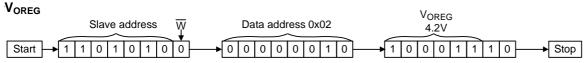

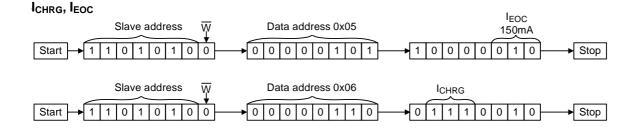

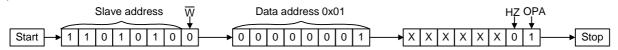

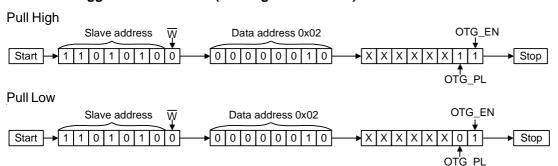

#### I<sup>2</sup>C Interface Timing Diagram

The RT9458 acts as an  $I^2C$  -bus slave. The  $I^2C$  -bus master configures the settings for charge mode and boost mode by sending command bytes to the RT9458 via the 2-wire  $I^2C$  -bus. After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The second byte selects the register to which the data will be written. The third byte contains data to the selected register.

S = Start Condition

W = Write (SDA = "0")

R = Read (SDA = "1")

ACK = Acknowledge

P = Stop Condition

#### **Charge Mode Operation**

#### **Support Quick Start Feature of Charger**

When the battery voltage is lower than 2.4V by overdischarge condition, the RT9458 charges the battery with 60mA to wake up the battery. Once the voltage level is higher than 2.4V, the RT9458 charges the battery to higher level with large current and makes sure that the system could work normally in short period with OTG pin pulled low.

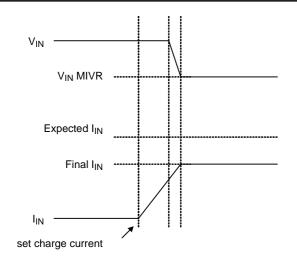

#### Minimum Input Voltage Regulation (MIVR)

The RT9458 features input voltage MIVR function to prevent input voltage drop due to insufficient current provided by the adaptor or USB input. If MIVR function is enabled, the input voltage decreases when the over current of the input power source occurs and is regulated at a predetermined voltage level which can be set as 4.1V to 4.7V per 0.1V step by I<sup>2</sup>C interface to MIVR[2:0] in the register of address 0x11 the MIVR bit is set to high. At this time, the current drawn by the RT9458 equals to the maximum current value that the input power can provide at the predetermined voltage level, instead of the set value.

Copyright@2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9458-01 December 2016 www.richtek.com

Figure 1. Minimum Input Voltage Regulation (MIVR)

#### **Charge Profile**

The RT9458 provides a precision Li-ion or Li-polymer charging solution for single-cell applications. Input current limit, charge current, termination current, charge voltage and input voltage MIVR are all programmable via the I<sup>2</sup>C interface. In charge mode, the RT9458 has five control loops to regulate input current, charge current, charge voltage, input voltage MIVR and device junction temperature. During the charging process, all five loops (if MIVR is enabled) are enabled and the dominant one will take over the control.

For normal charging process, the Li-ion or Li-polymer battery is charged in three charging modes depending on the battery voltage. At the beginning of the charging process, the RT9458 is in pre-charge mode. When the battery voltage rises above pre-charge threshold voltage ( $V_{PREC}$ ), the RT9458 enters fast-charge mode. Once the battery voltage is close to the regulation voltage ( $V_{OREG}$ ), the RT9458 enters constant voltage mode.

#### **Pre-Charge Mode**

For life-cycle consideration, the battery can not be charged with large current under low battery condition. When the BATS pin voltage is below pre-charge threshold voltage ( $V_{PREC}$ ), the charger is in pre-charge mode with a weak charge current which equals to the pre-charge current ( $I_{PREC}$ ). In pre-charge mode, the charger basically works as an LDO. The pre-charge current also acts as the current limit when the BATS pin is shorted.

#### **Fast-Charge Mode and Settings**

As the BATS pin rises above  $V_{PREC}$ , the charger enters fast-charge mode and starts switching. Notice that the RT9458 does not integrate input power source (AC adapter or USB input) detection. Thus, the RT9458 does not set the charge current automatically. Unlike the linear charger (LDO), the switching charger (Buck converter) is a current amplifier. The current drawn by the RT9458 is different from the current into the battery. The user can set the Average Input Current Regulation (AICR) and output charge current ( $I_{CHRG}$ ) respectively.

#### **Cycle-by-Cycle Current Limit**

The charger of the RT9458 has an embedded cycle-bycycle current limit for inductor. Once the inductor current touches the threshold (2.75A typ.), the charger stops charging immediately to prevent over current from damaging the device. Notice that, the mechanism can not be disabled by any way.

#### **Average Input Current Regulation (AICR)**

The AICR setting is controlled by the AICR section (bit 7 and 6) in the register of address 0x01. The written value of "00" is for USB100 mode with the maximum current limit of 100mA, "01" is for USB 500 mode with the maximum current limit of 500mA and "10" is for the maximum current limit of 1000mA. If the application does not need input current limit, write "11" into the IINLIMIT section.

#### Charge Current (I<sub>CHRG</sub>)

The charge current into the battery is determined by the sense resistor (R<sub>SENSE</sub>) and I<sub>CHRG</sub> section (bit4, bit5, and bit6) in the register of address 0x06. The voltage between the ISNSIN and BATS pins is regulated to the voltage control by I<sub>CHRG</sub> section. The charge current equals to the voltage between the ISNSIN and BATS pins (V<sub>ICHRG</sub>) divided by R<sub>SENSE</sub>:

$$I_{CHRG} = \frac{V_{ICHRG}}{R_{SENSE}}$$

For example, for a  $56m\Omega$  sense resistor, the charge current can be set from 500mA (ICHRG [2:0] = 000) to 1550mA (ICHRG [2:0] = 111).

When input current limit and charge current are both set, the charge current in fast charge phase is calculated as below:

$$I_{CHRG} = MIN \left[ \frac{V_{ICHRG}}{R_{SENSE}}, \left( \frac{I_{IN\_LIMIT}}{D} \times \eta \right) \right]$$

where D is the duty cycle and  $\eta$  is the efficiency.

#### **Constant Voltage Mode and Settings**

The RT9458 enters constant voltage mode when the BATS voltage is close to the output-charge voltage (V<sub>OREG</sub>). Once in this mode, the charge current begins to decrease. For default settings (charge current termination is disabled), the RT9458 does not turn off and always regulates the battery voltage at V<sub>OREG</sub>. However, once the charge current termination is enabled, the charger terminates if the charge current is below termination current (I<sub>EOC</sub>) in constant voltage mode. The charge current termination function is controlled by the I<sup>2</sup>C interface in the "TE" bit via the register of address 0x01.

After termination, a new charge cycle restarts when one of the following conditions is detected:

- $\blacktriangleright$  The BATS pin voltage falls below the  $V_{\text{OREG}}-V_{\text{RECH}}$  threshold.

- VIN Power On Reset (POR).

- ▶ CHG\_EN bit toggle or RST bit is set (via I<sup>2</sup>C interface).

#### **Output Charge Voltage (Voreg)**

The output-charge voltage is set by the  $I^2C$  interface in the CV section (Bit2 to Bit7 bits) via the register of address 0x02. Its range is from 3.5V to 4.45V. The default is 4.2V (100011).

#### **Termination Current (IEOC)**

If the end of charge detection and shutdown control for EOC are both enable (TE bit = "1", TE\_SHDN\_EN bit = "1"), the end-of-charge current is determined by both the change current ( $I_{CHRG}$ ) and  $I_{EOC}$  percentage.  $I_{EOC}$  percentage is set by the  $I^2C$  interface in the  $I_{EOC}$  section via the register of address 0x05. Its range is from 50mA to 400mA with an step of 50mA.

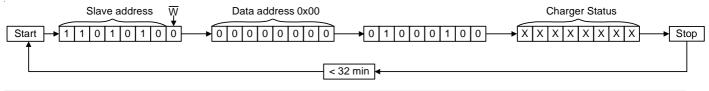

#### Safety Timer in Charge Mode and in OTG Mode

To implement safety mechanism, the RT9458 has two timer modes: T32min mode with a 32-minute timer for charger mode and T32sec mode with a 32-second timer for OTG mode.

In the charger mode, a the beginning of a charging operation, the RT9458 enters T32min mode and starts a 32-minute timer that can be reset by any read or write action performed by the host through the I<sup>2</sup>C interface. If the 32-minute timer expires, the charging operation is terminated and shows the fault bit CH32MI.

In the OTG mode, at the beginning of a OTG operation, the RT9458 enters T32sec mode and starts a 32-second timer that can be reset by any read or write action performed by the host through the I<sup>2</sup>C interface. If the 32-second timer expires, the OTG operation will keep going but shows the fault bit BST32SI.

#### Input Voltage Protection in Charge Mode

During charge mode, there are two protection mechanisms against poor input power source.

#### Sleep Mode $(V_{IN} - V_{BATS} < V_{SLP})$

The RT9458 enters sleep mode if the voltage drop between the VIN and BATS pins falls below  $V_{\text{SLP}}$ . In sleep mode, the reverse blocking switch and PWM are all turned off. This function prevents battery drain during poor or no input power source.

#### **Input Over-Voltage Protection**

When VIN voltage rises above the input over-voltage threshold ( $V_{INOVP}$ ), the RT9458 stops charging and then sets fault status bits. The condition is released when VIN falls below  $V_{INOVP} - V_{INOVP\_Hys}$ . The RT9458 then resumes charging operation.

#### **Boost Mode Operation (OTG)**

#### **Trigger and Operation**

The RT9458 features USB OTG. When OTG function is enabled, the synchronous boost control loop takes over the power MOSFETs and reverses the power flow from the battery to the VIN pin. In normal boost mode, the VMID pin is regulated to 5V (typ.) and provides up to 1A current to support other USB OTG devices connected to the USB connector.

#### **Output Over-Voltage Protection**

In boost mode, the output over-voltage protection is triggered when the VIN voltage is above the output OVP threshold (6V typ.). When OVP occurs and the boost mode is triggered by the OTG pin, the RT9458 goes back to Boost Configure state. When VIN returns to normal operating range, the condition is released and the boost resumes switching. However, if the boost mode is triggered by OPA bit, the RT9458 resets the OPA bit and goes back to Charge Configure state with default charge parameters.

#### **Output Overload Protection**

The RT9458 provides an overload protection to prevent the device and battery from damage when VIN is overload. Once overload condition is detected, the reverse blocking switch operates in linear region to limit the output current while the VMID voltage remains in voltage regulation. If the overload condition lasts for more than 32ms, the RT9458 will recognise the overload fault condition and resets registers to the default settings.

#### **Control Bits**

#### **CHG\_EN Bit (Charge Mode)**

The CHG\_EN bit in control register of address 0x07 is used to disable or enable the charge process. A value of "0" disable the charge, while a value of "1" enable the charge.

#### **RST Bit**

The RST bit in control register of address 0x04 is used to reset the RT9458 back to its default value at power-up, regardless of its charging or boosting process.

#### HZ (High Impedance Mode) Bit

When the HZ bit is set to "1" and the OTG pin is not in active status, the RT9458 operates in high impedance mode. The condition is released by POR or setting the HZ bit to "0".

#### **OPA Bit**

The OPA bit is the operation mode control bit, which is dependent on the status of HZ.

| OPA<br>bit | HZ<br>bit | Operation                                                                                                         |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------|

| 0          | 0         | Charge mode (no fault) Charge configure (fault, $V_{IN} > V_{UVLO}$ ) High impedance mode ( $V_{IN} < V_{UVLO}$ ) |

| 1          | 0         | Boost mode (no fault) Go to charge configure when any fault                                                       |

| Х          | 1         | High impedance mode                                                                                               |

#### **Battery Protection**

#### **Battery Over-Voltage Protection in Charge Mode**

The RT9458 monitors the BATS voltage for output overvoltage protection. In charge mode, if the BATS voltage rises above  $V_{\rm BATOVP}$  x  $V_{\rm OREG}$ , such as when the battery is suddenly removed, the RT9458 stops charging and then sets fault status bits. The condition is released when the BATS voltage falls below ( $V_{\rm BATOVP}-V_{\rm BATOVP\_Hys}$ ) x  $V_{\rm OREG}$ . The RT9458 then resumes charging process with default settings and the fault is cleared.

#### **Battery Detection During Normal Charging**

The RT9458 provides a battery absent detection scheme to detect insertion or removal of the battery pack. The battery detection scheme is valid only when the charge current termination is enabled (TE bit = "1").

During normal charging process, once the charge done condition is satisfied ( $V_{BATS} > V_{OREG} - V_{RECH}$  and termination current is detected), the RT9458 turns off the PWM converter and initiates a discharge current (detection current) for a detection time period. After that, the RT9458 checks the BATS voltage. If it is still above the recharge threshold, the battery is present and charge done is detected. If the BATS voltage is below the recharge threshold, the battery is absent. Thus, the RT9458 stops charging and the charge parameters are reset to the default values. The charge resumes after a period of  $t_{DET}$  (2sec. typ.).

#### **Thermal Considerations**

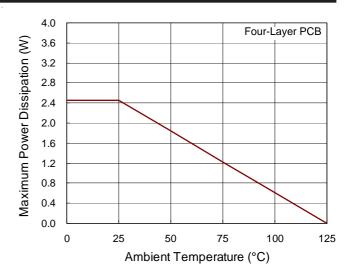

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WL-CSP-20B 2.1x1.87 (BSC) package, the thermal resistance,  $\theta_{JA}$ , is 40.8°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A=25^{\circ}C$  can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (40.8^{\circ}C/W) = 2.45W$  for a WL-CSP-20B 2.1x1.87 (BSC) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 2 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 2. Derating Curve of Maximum Power Dissipation

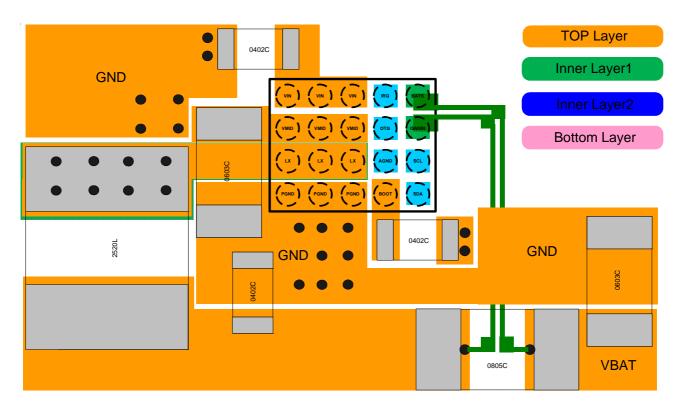

#### Layout consideration

The RT9458 layout guideline is shown as follow. There are several suggestion are provided.

- The capacitor of VMID should be as close as possible to RT9458 for reduce EMI.

- The GND path of VMID and BATS capacitor need to connect directly at TOP layer.

- The traces of Rsense need to follow differential rule to avoid the common mode noise.

- ➤ The other layers are ground plane for improve thermal performance.

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9458-01 December 2016

Figure 3. PCB Layout Guide

#### **Boost Mode**

There are two methods to trigger boost mode.

#### I<sup>2</sup>C - Triggered Boost Mode

#### OTG Pin - Triggered Boost Mode (Pull High or Pull Low)

#### **Keep Monitoring RT9458**

Copyright © 2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS9458-01 December 2016

Device Address: 1101010

| Address | Name           | Bit7      | Bit6     | Bit5           | Bit4           | Bit3                         | Bit2          | Bit1         | Bit0         |

|---------|----------------|-----------|----------|----------------|----------------|------------------------------|---------------|--------------|--------------|

|         | Device ID      |           | VENDO    | DR_ID          |                |                              | CHIP          | REV          |              |

| 0x03    | Reset Value    | 0         | 0        | 0              | 0              | 0                            | 0             | 0            | 1            |

|         | Read/Write     | R         | R        | R              | R              | R                            | R             | R            | R            |

|         | Control1       | Reserved  | Reserved | STA            | AT             | BOOST                        | PWR_Rdy       | OTG_<br>PinP | Reserved     |

| 0x00    | Reset<br>Value | 0         | 1        | 0              | 0              | 0                            | 0             | 0            | 0            |

|         | Read/Write     | R/W       | R/W      | R              | R              | R                            | R             | R            | R            |

|         | Control2       | IAICR     | 2[1:0]   | TE_SHDN<br>_EN | Higher_<br>OCP | TE                           | IAICR_<br>INT | HZ           | OPA_<br>MODE |

| 0x01    | Reset<br>Value | 0         | 0        | 0              | 0              | 0                            | 0             | 0            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

|         | Control3       |           |          | VOREG          | [5:0]          |                              |               | OTG_PL       | OTG_EN       |

| 0x02    | Reset<br>Value | 1         | 0        | 0              | 0              | 1                            | 1             | 1            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

|         | Control4       | RST       | Reserved | Reserved       | Reserved       | Reserved                     | Reserved      | Reserved     | Reserved     |

| 0x04    | Reset<br>Value | 0         | 0        | 0              | 0              | 0                            | 0             | 0            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

|         | Control5       | TMR_EN    | Reserved | Reserved       | Reserved       | Reserved                     |               | IEOC[2:0]    |              |

| 0x05    | Reset<br>Value | 1         | 0        | 0              | 0              | 0                            | 0             | 1            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

|         | Control6       | IAICR_SEL |          | ICHRG[2:0]     |                | FixFreq                      | \             | /PREC[2:0]   |              |

| 0x06    | Reset<br>Value | 0         | 0        | 0              | 0              | 0                            | 0             | 1            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

|         | Control7       | Reserved  | BATD_EN  | Reserved       | CHG_EN         |                              | VMRE          | G[3:0]       |              |

| 0x07    | Reset<br>Value | 0         | 0        | 0              | 1              | 0                            | 0             | 0            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

|         | IRQ1           | TSDI      | VINOVPI  | Reserved       | Reserved       | Reserved                     | Reserved      | Reserved     | BATAB        |

| 0x08    | Reset<br>Value | 0         | 0        | 0              | 0              | 0                            | 0             | 0            | 0            |

|         | Read/Write     | R         | R        | R              | R              | R                            | R             | R            | R            |

|         | Control8       | Reserved  |          | MIVR[2:0]      | T              | Reserved Reserved IPREC[1:0] |               | C[1:0]       |              |

| 0x11    | Reset<br>Value | 0         | 1        | 0              | 0              | 0                            | 0             | 1            | 0            |

|         | Read/Write     | R/W       | R/W      | R/W            | R/W            | R/W                          | R/W           | R/W          | R/W          |

| Address | Name           | Bit7           | Bit6     | Bit5          | Bit4         | Bit3         | Bit2     | Bit1         | Bit0         |

|---------|----------------|----------------|----------|---------------|--------------|--------------|----------|--------------|--------------|

|         | IRQ2           | CHRVPI         | Reserved | CHBATOVI      | CHTERMI      | CHRCHGI      | CH32MI   | CHTREGI      | CHMIVRI      |

| 0x09    | Reset<br>Value | 0              | 0        | 0             | 0            | 0            | 0        | 0            | 0            |

|         | Read/Write     | R              | R        | R             | R            | R            | R        | R            | R            |

|         | IRQ3           | BSTVINOVI      | BSTOLI   | BSTLOWVI      | Reserved     | BST32SI      | Reserved | Reserved     | Reserved     |

| 0x0A    | Reset<br>Value | 0              | 0        | 0             | 0            | 0            | 0        | 0            | 0            |

|         | Read/Write     | R              | R        | R             | R            | R            | R        | R            | R            |

|         | Mask 1         | TSDM           | VINOVPIM | Reserved      | Reserved     | Reserved     | Reserved | Reserved     | BATABM       |

| 0x0B    | Reset<br>Value | 0              | 0        | 0             | 0            | 0            | 0        | 0            | 0            |

|         | Read/Write     | R/W            | R/W      | R/W           | R/W          | R/W          | R/W      | R/W          | R/W          |

|         | Mask 2         | CHRVPIM        | Reserved | CHBATOVI<br>M | CHTERMI<br>M | CHRCHGI<br>M | CH32MIM  | CHTREGI<br>M | CHMIVRI<br>M |

| 0x0C    | Reset<br>Value | 0              | 0        | 0             | 0            | 0            | 0        | 0            | 0            |

|         | Read/Write     | R/W            | R/W      | R/W           | R/W          | R/W          | R/W      | R/W          | R/W          |

|         | Mask 3         | BSTVINOVI<br>M | BSTOLIM  | BSTLOWVI<br>M | Reserved     | BST32SI<br>M | Reserved | Reserved     | Reserved     |

| 0x0D    | Reset<br>Value | 0              | 0        | 0             | 0            | 0            | 0        | 0            | 0            |

|         | Read/Write     | R/W            | R/W      | R/W           | R/W          | R/W          | R/W      | R/W          | R/W          |

19

#### **Detail Table Descriptions**

| Address                         | Name        | Bit7       | Bit6               | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------------------------------|-------------|------------|--------------------|------|------|------|------|------|------|

|                                 | Device ID   |            | VENDOR_ID CHIP_REV |      |      |      |      |      |      |

| 0x03                            | Reset Value | 0          | 0                  | 0    | 0    | 0    | 0    | 0    | 1    |

|                                 | Read/Write  | R          | R                  | R    | R    | R    | R    | R    | R    |

| VENDOR_ID Vendor Identification |             |            |                    |      |      |      |      |      |      |

| CHI                             | P_REV       | Chip Revis | sion               |      |      |      |      |      |      |

| Address | Name        | Bit7                                                                                                                                      | Bit6         | Bit5                                   | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------|------|------|------|------|------|--|--|

|         | Control1    | Reserved                                                                                                                                  | Reserved     | eserved STAT BOOST PWR_Rdy OTG_PinP Re |      |      |      |      |      |  |  |

| 0x00    | Reset Value | 0                                                                                                                                         | 1            | 0                                      | 0    | 0    | 0    | 0    | 0    |  |  |

|         | Read/Write  | R/W                                                                                                                                       | R/W          | R                                      | R    | R    | R    | R    | R    |  |  |

| S       | STAT        | Charger status bit 00 : Ready 01 : Charge in progress 10 : Charge done 11 : Fault                                                         |              |                                        |      |      |      |      |      |  |  |

| В       | DOST        | 1 : Boost n                                                                                                                               | node, 0 : No | t in Boost m                           | node |      |      |      |      |  |  |

| PW      | 'R_Rdy      | Power status bit  0: VIN > VOVP or VIN < VUVLO or VIN < BATS + VSLP (Power Fault)  1: UVLO < VIN < VOVP & VIN > BATS + VSLP (Power Ready) |              |                                        |      |      |      |      |      |  |  |

| ОТ      | G_PinP      | OTG pin polarity 0: OTG input pin is low 1: OTG input pin is high                                                                         |              |                                        |      |      |      |      |      |  |  |

| Address | Name        | Bit7                                        | Bit6                                                            | Bit5                                                               | Bit4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit3                      | Bit2             | Bit1       | Bit0        |  |

|---------|-------------|---------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|------------|-------------|--|

|         | Control2    | IAIC                                        | R[1:0]                                                          | TE_SHDN_<br>EN                                                     | Higher_OCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TE                        | IAICR_INT        | HZ         | OPA_MODE    |  |

| 0x01    | Reset Value | 0                                           | 1                                                               | 0                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                         | 0                | 0          | 0           |  |

|         | Read/Write  | R/W                                         | R/W         R/W         R/W         R/W         R/W         R/W |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                  |            |             |  |

| IAIG    | CR[1:0]     | 00 : VIN<br>10 : VIN<br>When IA<br>00 : VIN | 1A currer<br>ICR_SEL<br>100mA c                                 | urrent limit, 01<br>nt limit, 11 : nc<br>. = 1<br>urrent limit, 01 | : VIN 500mA of input current lite: VIN 700mA of input current current current current in the current c | imit (defa<br>current lir | nult 01)<br>mit, |            |             |  |

| TE_S    | HDN_EN      |                                             |                                                                 |                                                                    | ge is not shutd<br>ge is shutdowr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |                  |            |             |  |

| High    | er_OCP      | 0 : Buck                                    | OCP = 2.                                                        | ection bit<br>75A, OTG OC<br>75A, OTG OC                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                  |            |             |  |

|         | TE          | 1 : Enab                                    | le end of                                                       | charge detecti                                                     | on, 0 : Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | end of c                  | harge detection  | on (defau  | It 0)       |  |

| IAIC    | CR_INT      | curre                                       | ded by exent limit w                                            | kternal OTG phen OTG pinernal I <sup>2</sup> C IAICF               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rent limi                 | t when OTG       | pin is lov | w and 100mA |  |

|         | HZ          | 1 : High                                    | impedano                                                        | e mode, 0 : N                                                      | ot high impeda                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nce mod                   | e (default 0)    |            |             |  |

| OPA     | _MODE       | 1 : Boos                                    | t mode, 0                                                       | : Charger mo                                                       | de (default 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |                  |            |             |  |