# **Discontinued Product**

This device is no longer in production. The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: March 4, 2013

# **Recommended Substitutions:**

For existing customer transition, and for new customers or new applications, contact Allegro Sales.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

### **Features and Benefits**

- Low quiescent current draw (0.1 μA in shutdown mode)

- Primary-side output voltage sensing; no resistor divider required

- User-adjustable current limit from 0.4 to 1.2 A

- 1.1 V logic (V<sub>HI</sub>(min)) compatibility

- Integrated IGBT driver with separate sink and source (CG package) or common sink/source (EJ package)

- Flash dual trigger with interlock for increased noise immunity

- Optimized for mobile phone, 1-cell Li+ battery applications

- No primary-side Schottky diode needed

- Zero-voltage switching for lower loss

- >75% efficiency

- Optional regulation feature to maintain the output voltage

- Charge complete indication

- Integrated 40 V DMOS switch

# Packages:

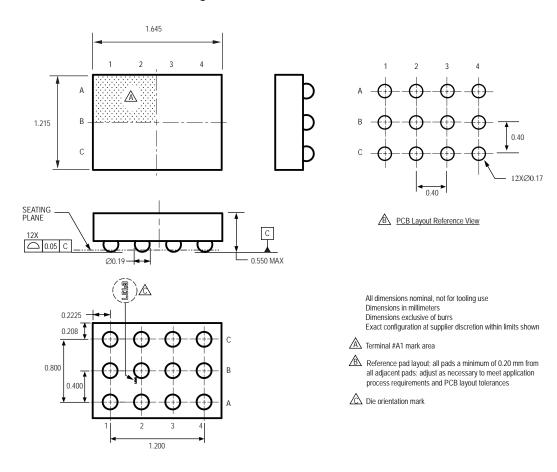

10-contact DFN/MLP 3 mm × 3 mm 0.75 nominal overall height (Package EJ)

12-ball WLCSP 1.205 mm × 1.635 mm 0.5 nominal overall height (Package CG)

# **Description**

The Allegro® A8437 Xenon photoflash charger IC is designed to meet the needs of ultra-low power, small form factor cameras, particularly camera-phones.

The charge current time is adjustable by setting the charge current limit from 0.4 to 1.2 A maximum. By using primary-side voltage sensing, the need for a secondary-side resistive voltage divider is eliminated. This has the additional benefit of reducing leakage currents on the secondary side of the transformer. To extend battery life, the A8437 features very low supply current draw—typically 0.1  $\mu$ A in shutdown mode and 10  $\mu$ A in standby mode.

The A8437 has a flash dual trigger IGBT driver and flash interlock to increase the device noise immunity. The IGBT driver also has separate source and sink connections, for flexibility in controlling IGBT rise and fall times. The charge and trigger voltage logic thresholds are set at 1.1  $V_{\rm HI}$  (min) to support applications implementing low voltage control logic.

The A8437 is available in a 10-pin, 3 mm × 3 mm DFN/MLP package with exposed pad for enhanced thermal performance. For an even smaller PCB footprint, a wafer-level chip scale package (WLCSP) option is available.

Applications include:

- Mobile phone flash

- Digital and film camera flash

TRIGGER2

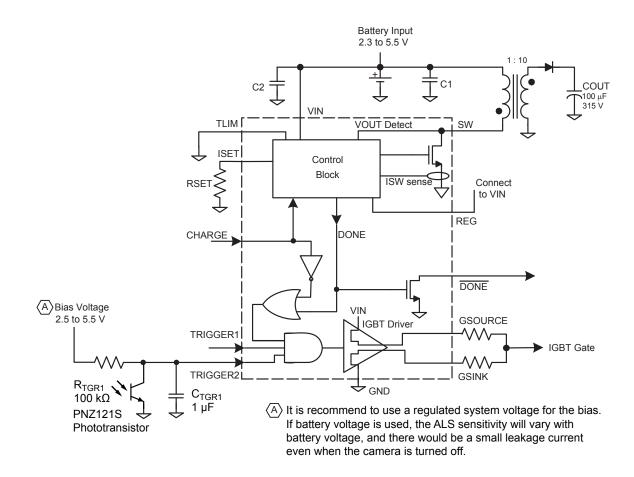

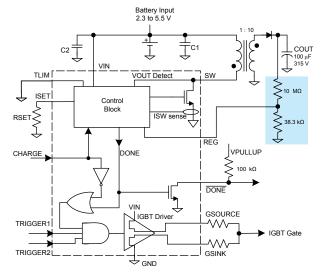

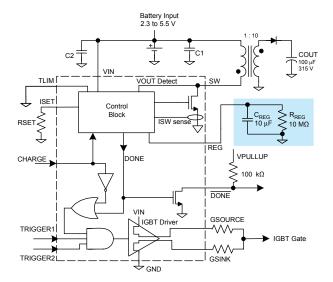

# **Typical Application**

### CG Package

# Battery Input 2.3 to 5.5 V C1 COUTT COUTT

# Application 1. Typical application without output voltage regulation. Note: Application must periodically restart the charging cycle to recover lost charge on the output capacitor.

# RSET Battery Input 2.3 to 5.5 V VIN VOUT Detect SW Connect to VIN TRIGGER1 TRIGGER1 GATE Battery Input 100 µF 315 V COUT 100 µF 315 V VIN TOUT Detect SW Connect to VIN IGBT Driver IGBT Gate GATE

$\Rightarrow_{\mathsf{GND}}$

EJ Package

### **Selection Guide**

| Part Number  | Package            | Packing                             |

|--------------|--------------------|-------------------------------------|

| A8437ECGLT*  | 12-ball WLCSP      | Tape and reel, 4000 pieces per reel |

| A8437EEJTR-T | 10-contact DFN/MLP | Tape and reel, 1500 pieces per reel |

<sup>\*</sup>Contact Allegro for additional ordering information.

### **Absolute Maximum Ratings**

| Characteristic                | Symbol               | Notes                                                                                                                                                                                                               | Rating                          | Units |

|-------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|

|                               |                      | DC voltage.                                                                                                                                                                                                         |                                 |       |

| SW Pin                        | V <sub>SW</sub>      | (V <sub>SW</sub> is self-clamped by internal active clamp<br>and is allowed to exceed 40 V during flyback<br>spike durations. Maximum repetitive energy<br>during flyback spike: 0.5 µJ at frequency<br>≤ 400 kHz.) | -0.3 to 40                      | V     |

| VIN Pin                       | V <sub>IN</sub>      |                                                                                                                                                                                                                     | -0.3 to 6.0                     | V     |

| CHARGE, TRIGGERX, DONE Pins   |                      | Care should be taken to limit the current when –0.6 V is applied to these pins.                                                                                                                                     | -0.6 to V <sub>IN</sub> + 0.3 V | V     |

| Remaining Pins                |                      |                                                                                                                                                                                                                     | -0.3 to V <sub>IN</sub> + 0.3 V | V     |

| Operating Ambient Temperature | T <sub>A</sub>       | Range E                                                                                                                                                                                                             | -40 to 85                       | °C    |

| Maximum Junction              | T <sub>J</sub> (max) |                                                                                                                                                                                                                     | 150                             | °C    |

| Storage Temperature           | T <sub>stg</sub>     |                                                                                                                                                                                                                     | -55 to 150                      | °C    |

### **Thermal Characteristics**

| Characteristic                          | Symbol           | Test Conditions <sup>1</sup>                                                                                  | Value | Units |

|-----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------|-------|-------|

|                                         |                  | CG package, on 4-layer PCB based on JEDEC standard                                                            | 100   | °C/W  |

| Package Thermal Resistance <sup>2</sup> | R <sub>θJA</sub> | EJ package, on 2-layer PCB with 0.88 in. <sup>2</sup> area of 2 oz. copper each side, based on JEDEC standard | 65    | °C/W  |

|                                         |                  | EJ package, on 4-layer PCB based on JEDEC standard                                                            | 45    | °C/W  |

<sup>&</sup>lt;sup>1</sup>Additional thermal information available on Allegro website.

<sup>&</sup>lt;sup>2</sup>CG results preliminary.

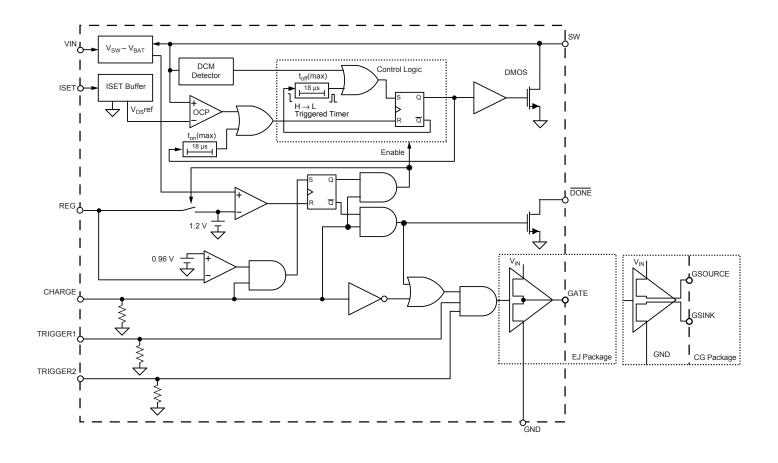

# **Functional Block Diagram**

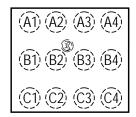

# **Pin-out Diagrams**

(Contacts Down Views)

CG Package

Orientation mark on ball side

EJ Package

# **Terminal List Table**

| Nama     | Number |    | Function                                                                                                                                                                                      |  |

|----------|--------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name     | CG     | EJ | Function                                                                                                                                                                                      |  |

| ISET     | C4     | 1  | Sets the maximum switch current; connect an external resistor to GND to set the desired peak current                                                                                          |  |

| GATE     | _      | 2  | IGBT gate drive – sink/source                                                                                                                                                                 |  |

| GSOURCE  | В3     | -  | IGBT gate drive – source                                                                                                                                                                      |  |

| GSINK    | C3     | -  | IGBT gate drive – sink                                                                                                                                                                        |  |

| VIN      | C2     | 3  | Input voltage; connect to a 2.3 to 5.5 V bias supply                                                                                                                                          |  |

| GND      | C1     | 4  | Ground connection                                                                                                                                                                             |  |

| CHARGE   | B1     | 5  | Pull high to initiate charging; pull low to enter low-power standby mode                                                                                                                      |  |

| TRIGGER2 | B2     | 6  | IGBT input trigger 2                                                                                                                                                                          |  |

| SW       | A1     | 7  | Drain connection of internal power MOSFET switch; connect to transformer                                                                                                                      |  |

| TRIGGER1 | A2     | 8  | IGBT input trigger 1                                                                                                                                                                          |  |

| DONE     | A3     | 9  | Pulls low when output reaches target value and CHARGE pin is high; goes high during charging or whenever CHARGE pin is low                                                                    |  |

| TLIM     | A4     | -  | For production test only; connect to GND on PCB                                                                                                                                               |  |

| REG      | B4     | 10 | Output voltage regulation pin; connect to external resistor and capacitor to regulate output voltage, or connect to VIN pin to disable regulation (see Output Regulation section for details) |  |

| EP       | n.a.   | _  | Exposed pad for enhanced thermal dissipation; not connected electrically                                                                                                                      |  |

ELECTRICAL CHARACTERISTICS typical values valid at V = 2.6 V B = 1.0 A and T. =25°C unless otherwise noted

| Characteristics                              | Symbol                 | Test Conditions                                                                                | Min.  | Тур. | Max. | Unit |

|----------------------------------------------|------------------------|------------------------------------------------------------------------------------------------|-------|------|------|------|

| VIN Voltage Range                            | V <sub>IN</sub>        |                                                                                                | 2.3   | _    | 5.5  | V    |

| UVLO Enable Threshold                        | V <sub>INUV</sub>      | V <sub>IN</sub> rising                                                                         | _     | 2.05 | 2.2  | V    |

| UVLO Hysteresis                              | V <sub>INUVhys</sub>   |                                                                                                | _     | 150  | _    | mV   |

|                                              |                        | Shutdown (CHARGE = 0 V,<br>TRIGGER1 and TRIGGER2 = 0 V)                                        | _     | 0.01 | 0.5  | μA   |

| VIN Cumply Current                           |                        | Charging complete, regulation disabled (REG = VIN)                                             | _     | 10   | 50   | μΑ   |

| VIN Supply Current                           | I <sub>IN</sub>        | Charging complete, regulation enabled                                                          | _     | 0.5  | _    | mA   |

|                                              |                        | Charging (CHARGE = VIN,<br>TRIGGER1 and TRIGGER2 = 0 V)                                        | _     | 2    | _    | mA   |

| Current Limits                               |                        |                                                                                                |       |      |      |      |

| Switch Current Limit <sup>1</sup>            | I <sub>SWIimMAX</sub>  | Maximum, $R_{SET}$ = 26.7 k $\Omega$                                                           | 1.08  | 1.2  | 1.32 | Α    |

| Switch Current Limit                         | I <sub>SWlimMIN</sub>  | Minimum, $R_{SET}$ = 85 k $\Omega$                                                             | _     | 0.4  | _    | Α    |

| SW / ISET Current Ratio                      | $I_{SW}/I_{SET}$       | $R_{SET}$ = 33 kΩ, CHARGE = high                                                               | _     | 28   | _    | kA/A |

| ISET Pin Voltage While Charging              | V <sub>SET</sub>       | $R_{SET}$ = 33 kΩ, CHARGE = high                                                               | _     | 1.2  | _    | V    |

| ISET Pin Internal Resistance                 | R <sub>SET(INT)</sub>  |                                                                                                | _     | 1000 | _    | Ω    |

| Switch On-Resistance                         | R <sub>SWDS(on)</sub>  | $V_{IN} = 3.6 \text{ V}, I_D = 800 \text{ mA}, T_A = 25^{\circ}\text{C}$                       | _     | 0.25 | _    | Ω    |

|                                              |                        | $V_{SW} = V_{IN}(max)$ , over temperature range                                                | _     | _    | 2    | μA   |

| Switch Leakage Current <sup>2</sup>          | I <sub>SWIk</sub>      | Combined $V_{IN}$ and SW leakage current at $T_A$ =25°C $V_{IN}$ = 5.5 V in Shutdown           | _     | _    | 0.5  | μA   |

| CHARGE Input Current                         | I <sub>CHARGE</sub>    | V <sub>CHARGE</sub> = V <sub>IN</sub>                                                          | _     | 36   | _    | μA   |

| CHARGE Input Voltage <sup>2</sup>            | \/                     | High, over input supply range                                                                  | 1.1   | -    | _    | V    |

| CHARGE Input Voltage <sup>2</sup>            | $V_{CHARGE}$           | Low, over input supply range                                                                   | _     | _    | 0.4  | V    |

| CHARGE Pull-Down Resistor Value              | R <sub>CHPD</sub>      |                                                                                                | _     | 100  | _    | kΩ   |

| CHARGE ON/OFF Delay                          | t <sub>CH</sub>        |                                                                                                | _     | 20   | _    | us   |

| Maximum Switch-Off Timeout                   | t <sub>offMAX</sub>    |                                                                                                | _     | 18   | _    | μs   |

| Maximum Switch-On Timeout                    | t <sub>onMAX</sub>     |                                                                                                | _     | 18   | _    | μs   |

| DONE Output Leakage Current <sup>2</sup>     | I <sub>DONEIk</sub>    |                                                                                                | _     | _    | 1    | μA   |

| DONE Output Low Voltage <sup>2</sup>         | V <sub>DONEL</sub>     | 32 μA into DONE pin                                                                            | _     | _    | 100  | mV   |

| Output Comparator Trip Voltage <sup>2</sup>  | V <sub>OUTTRIP</sub>   | Measured as V <sub>SW</sub> – V <sub>IN</sub>                                                  | 31    | 31.5 | 32   | V    |

| Output Comparator Overdrive                  | V <sub>OUTOV</sub>     | Pulse width = 200 ns (90% to 90%)                                                              | _     | 200  | 400  | mV   |

| Minimum dV/dt for ZVS Comparator             | dV/dt                  | Measured at SW pin                                                                             | _     | 20   | _    | V/µs |

| Regulation                                   |                        | '                                                                                              |       |      |      |      |

| REG Voltage When Charging Completes          | V <sub>REG(H)</sub>    | CHARGE = high, at DONE → low transition                                                        | 1.15  | 1.2  | 1.25 | V    |

| REG Voltage Threshold for Regulation         | V <sub>REG(L)</sub>    | CHARGE = high, at DONE = low                                                                   | _     | 0.96 | _    | V    |

| REG Output Current Drive Capability          | I <sub>REG</sub>       | CHARGE = high, at $\overline{\text{DONE}}$ = high, $V_{SW} - V_{IN}$ = 30 V, $V_{REG}$ = 1.0 V | _     | 50   | _    | μA   |

| DEC Lookage Current While Not Charging       | 1                      |                                                                                                |       | 0.1  |      |      |

| REG Leakage Current While Not Charging       | I <sub>REGIK</sub>     | CHARGE = high, at $\overline{\text{DONE}}$ = low, $V_{\text{REG}}$ = 1.2 V                     | _     | 0.1  | _    | μA   |

| IGBT Driver                                  | \/                     | Input - logic bish over input supply same                                                      | 1 4 4 |      | 1    | V    |

| TRIGGER, TRIGGER2 Input Voltage <sup>2</sup> | V <sub>TRIG(H)</sub>   | Input = logic high, over input supply range                                                    | 1.1   | _    | 0.4  |      |

| TRICCED TRICCEDS Bull Davin Berlieber        | V <sub>TRIG(L)</sub>   | Input = logic low, over input supply range                                                     | _     | 100  | 0.4  | V    |

| TRIGGER, TRIGGER2 Pull-Down Resistor         | R <sub>TRIGPD</sub>    |                                                                                                | -     | 100  | _    | kΩ   |

| GSOURCE Resistance to VIN3                   | R <sub>SrcDS(on)</sub> | V <sub>IN</sub> = 3.6 V, V <sub>GSOURCE</sub> = 1.8 V                                          | -     | 5    | _    | Ω    |

| GSINK Resistance to GND <sup>3</sup>         | R <sub>SnkDS(on)</sub> | V <sub>IN</sub> = 3.6 V, V <sub>GSINK</sub> = 1.8 V                                            | -     | 6    | _    | Ω    |

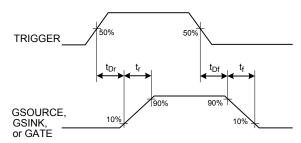

| Propagation Delay (Rising)                   | t <sub>Dr</sub>        |                                                                                                | _     | 30   | _    | ns   |

| Propagation Delay (Falling)                  | t <sub>Df</sub>        | GSOURCE and GSINK tied together, measurement                                                   | _     | 30   |      | ns   |

| Output Rise Time                             | t <sub>r</sub>         | taken at pin; $R_{GATE}$ = 12 $\Omega$ , $C_L$ = 6500 pF, $V_{IN}$ = 3.6 V                     | _     | 70   |      | ns   |

| Output Fall Time                             | t <sub>f</sub>         |                                                                                                | _     | 70   |      | ns   |

<sup>&</sup>lt;sup>1</sup>Current limit guaranteed by design and correlation to static test. Refer to application section for peak current in actual circuits.

<sup>&</sup>lt;sup>3</sup>GSOURCE and GSINK tied together (GATE pin) in EJ package.

<sup>&</sup>lt;sup>2</sup>Specifications over the range  $T_A = -40$ °C to 85°C; guaranteed by design and characterization.

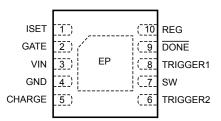

# **Timing and IGBT Interlock Function**

The two TRIGGER signals are internally ANDed together. As shown in the timing diagram, below, triggering is prohibited during the initial charging process. This prevents premature firing

of the flash before the output capacitor has been charged to its target voltage. Refer to the section IGBT Gate Driver Interlock for details.

| Case | Description                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А    | $\frac{\text{TRIGGER}}{\text{DONE}} \text{ pins are both high). IGBTDRV is disabled in this case.}$                                                         |

| В    | Arrives during regulation mode, while not refreshing. IGBTDRV is enabled. Charging resumes once TRIGGER is low again.                                       |

| С    | Arrives during regulation mode, while refreshing. Charging is stopped after present cycle. IGBTDRV is enabled. Charging resumes after TRIGGER is low again. |

| D    | Arrives while IC is in low-power Standby mode (CHARGE pin is low). IGBTDRV is always enabled in this case.                                                  |

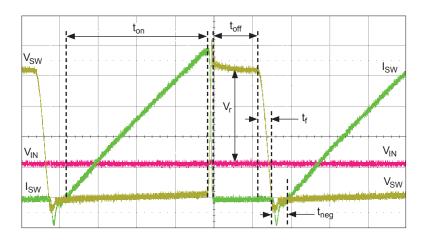

# **IGBT Drive Timing Definition**

# **Performance Characteristics**

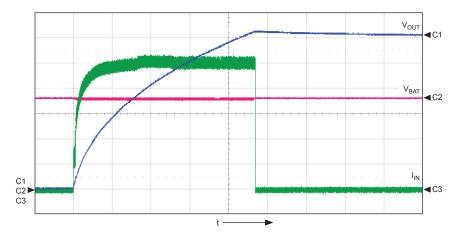

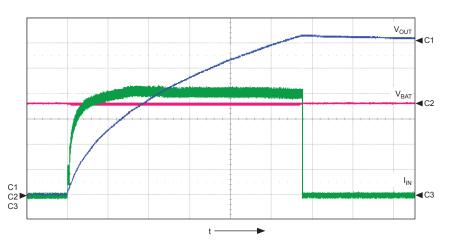

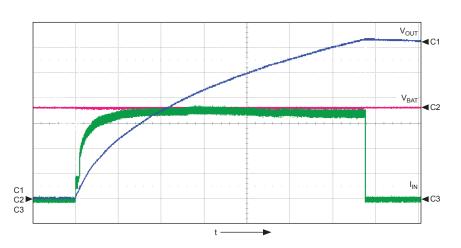

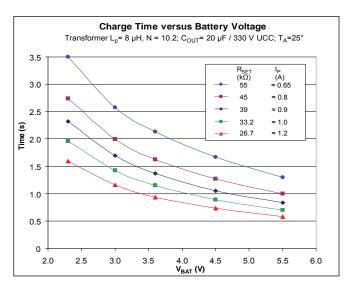

Charging Time at Various Peak Current Levels

| Common Parameters |                  |                |  |  |  |

|-------------------|------------------|----------------|--|--|--|

| Symbol            | Parameter        | Units/Division |  |  |  |

| C1                | V <sub>OUT</sub> | 50 V           |  |  |  |

| C2                | $V_{BAT}$        | 1 V            |  |  |  |

| C3                | I <sub>IN</sub>  | 100 mA         |  |  |  |

| t                 | time             | 200 ms         |  |  |  |

| Conditions        | Parameter        | Value          |  |  |  |

|                   | $V_{BATT}$       | 3.6 V          |  |  |  |

|                   | C <sub>OUT</sub> | 20 μF          |  |  |  |

| Conditions | Parameter        | Value   |

|------------|------------------|---------|

|            | R <sub>SET</sub> | 33.2 kΩ |

|            | Levation         | ≈1 0 A  |

| Conditions | Parameter        | Value |

|------------|------------------|-------|

|            | R <sub>SET</sub> | 39 kΩ |

|            | I                | ≈n    |

$C_{OUT}\!\!=\!20~\mu F.$  For larger or smaller capacitances, charging time scales proportionally.

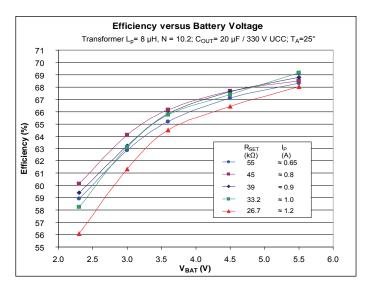

Special low-profile transformer with relatively low inductance (Lp=  $8~\mu H$ ) and high winding resistance (Rp =  $0.37~\Omega$ ). Higher efficiency can be achieved by using transformers with higher Lp, which reduces switching frequency and therefore switching loses, and lower resistance, which reduces conduction losses.

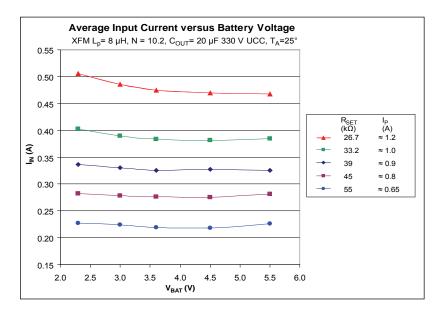

An increase in  $I_{SWlim}$  with respect to  $V_{BAT}$  actually keeps the average input current roughly constant throughout the battery voltage range. Normally, if  $I_{SWlim}$  is kept constant, the average current will drop as  $V_{BAT}$  goes higher.

# **Application Information**

# **General Operation Overview**

The CHARGE pin enables the part and starts charging. The DONE open-drain indicator is pulled low when CHARGE is high and target output voltage is reached. Charging is reinitiated when the REG pin voltage falls below the regulation threshold. Pulling the CHARGE pin low stops charging and forces the chip into low-power standby mode.

# **Output Voltage Regulation**

When the REG pin is connected to VIN, the A8437 stops charging the output voltage after the reflected voltage ( $V_{SW}-V_{IN}$ ) reaches 31.5 V. In this mode, charging can be reinitiated by cycling the CHARGE signal through a low to high transition.

The A8437 can also be used to regulate output voltage within a predetermined window. In this mode, connect a capacitor, CREG, and resistor, RREG, from the REG pin to GND (refer to the figure Application 3). When CHARGE is held high, the voltage monitoring circuit of the A8437 is always active, irrespective of the REG pin voltage level.

Voltage Regulation Using Predictive Droop The A8437 uses a technique called *Predictive Droop* for regulating the output capacitor voltage after the completion of a charging cycle. When the target output voltage is reached, the converter stops charging and output capacitor voltage droops due to leakage current. An external resistor and capacitor connected from the REG pin to ground will provide an RC discharge time constant. This time constant can be selected to mirror the droop rate of the output capacitor. When voltage at the REG pin drops to 80% of the reference value, the converter starts charging again and brings the output capacitor back to target voltage again.

The time required for an RC network to discharge from  $V_0$  to  $V_T$  is given by:

$$T = R \times C \times \ln\left(V_0/V_{\rm T}\right). \tag{1}$$

For example, if  $C = 10 \mu F$ ,  $R = 10 M\Omega$  and  $V_0/V_T = 1.25$ , then T = 22 seconds. Assuming that the RC-discharge characteristic of the output capacitor matches that at the REG pin, we can predict that the output voltage has drooped 20%, and therefore it is time to recharge the output capacitor.

By implementing a Predictive Droop technique, no additional leakage paths are introduced on the secondary side, which helps to keep power losses to a minimum. By intentionally making the RC discharge time constant of the REG pin shorter than that of the output capacitor, we can regulate the output voltage to a window tighter than the default 20% hysteresis.

Voltage Regulation Using Direct Sensing If direct sensing from the secondary side is desired, connect the REG pin to a resistor divider network across the output capacitor to enable output regulation. In this case, the charging cut-off is still controlled by primary side sensing (charging stops when reflected voltage reaches  $31.5 \, \text{V}$ ), but the regulation threshold is controlled by the secondary side sensing. When the CHARGE pin is high, and the sensed output voltage falls below the lower  $V_{REG}$  threshold, the flyback converter charges the output capacitor again until the primary side sensing stops further charging. This cycle repeats till the CHARGE pin is pulled low.

The benefit of this method is that a lower output voltage can be selected independently, simply by changing the resistor divider ratio. For example, given  $R_1$ =10 M $\Omega$ ,  $R_2$ = 33.2 k $\Omega$ , and  $V_{REG(L)}$ = 0.96 V, then:

$$V_{\text{OUT}}(\text{Low}) = V_{\text{REG(L)}} \times (R_1/R_2 + 1) = 290 \text{ V}$$

. (2)

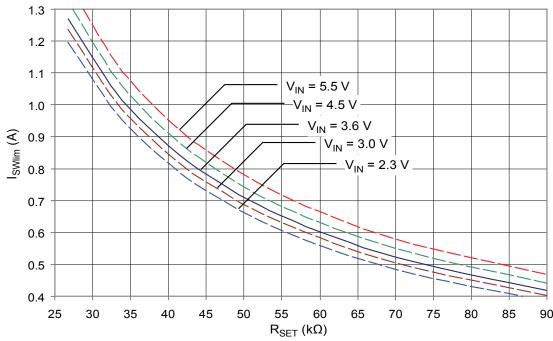

# Selection of Switching Current Limit

The A8437 features continuously adjustable peak switching current between 0.4 and 1.2A. This is done

by selecting the value of an external resistor RSET, connected from the ISET pin to GND, which determines the ISET bias current, and therefore the switching current limit,  $I_{SWlim}$ .

To the first order approximation,  $I_{SWlim}$  is related to  $I_{SET}$  and  $R_{SET}$  according to the following equations:

$$I_{\text{SWlim}} = I_{\text{SET}} \times K = V_{\text{SET}} / R_{\text{SET}} \times K$$

, (3)

where K = 28000 when battery voltage is 3.6 V.

In real applications, the actual switching current limit is affected by input battery voltage, and also the transformer primary inductance, Lp. If necessary, the following expressions can be used to determine  $I_{SWlim}$  more accurately:

$$I_{\text{SET}} = V_{\text{SET}} / (R_{\text{SET}} + R_{\text{SET(INT)}} - K \times R_{\text{GND(INT)}}),$$

(4)

where:

$R_{SET(INT)}$  is the internal resistance of the  $I_{SET}$  pin (1 k $\Omega$  typical),

$R_{GND(INT)}$  is the internal resistance of the bonding wire for the GND pin (27 m $\Omega$  typical), and

$$K = (K' + V_{IN} \times K'')$$

, with  $K' = 24350$  and  $K'' \approx 1040$  at  $T_A = 25$ °C. Then,

$$I_{\text{SWlim}} = I_{\text{SFT}} \times K + V_{\text{BAT}} / L_{\text{P}} \times t_{\text{D}}, \qquad (5)$$

where  $t_D$  is the delay in SW turn-off (0.1 µs typical).

The chart at the bottom of the page can be used to determine the relationship between  $R_{SET}$  and  $I_{SWlim}$  at various battery voltages.

# Peak Current Limit versus ISET Resistance $V_{IN} = V_{BAT}$ , XFM Lp = 8 $\mu$ H, $T_A$ =25°C

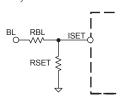

# Smart Current Limit (Optional)

With the help of some simple external logic, the user can change the charging current according to the battery voltage. For example, assume that  $I_{SET}$  is normally 36  $\mu A$  (for  $I_{SWlim}$  = 1.0 A). Referring to the following illustration, when the battery voltage drops

below 2.5 V, the signal at BL (battery-low) goes high. The resistor RBL, connecting BL to the ISET pin, then injects 10  $\mu A$  into RSET. This effectively reduces ISET current to 26  $\mu A$  (for  $I_{SWLIM}$  = 0.73 A). A disadvantage of the above method is that the 10  $\mu A$  current is always flowing whenever the BL signal goes high.

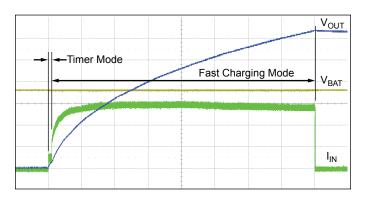

# Timer Mode and Fast Charging Mode

The A8437 achieves fast charging times and high efficiency by operating in discontinuous conduction mode (DCM) through most of the charging process. The relationship of Timer Mode and Fast Charging Mode is shown in the following figure.

$\begin{array}{l} t = & 200 \; ms/div; \; V_{OUT} = & 50 \; V/div; \; V_{BAT} = & 1 \; V/div.; \; I_{IN} = & 100 \; mA/div. \\ V_{BAT} = & 3.6 \; V; \; C_{OUT} = & 20 \; \mu F/330 \; V; \; R_{SET} = & 46 \; k\Omega \; (I_{SWlim} \approx 0.75 \; A) \end{array}$

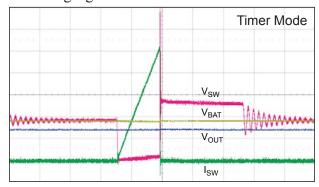

The IC operates in Timer Mode when beginning to charge a completely discharged photoflash capacitor, usually when the output voltage,  $V_{OUT}$ , is less than approximately 15 to 20 V. Timer Mode is a fixed

period, 18 µs, off-time control. One advantage of having Timer Mode is that it limits the initial battery current surge and thus acts as a "soft-start." A time-expanded view of a Timer Mode interval is shown in the following figure.

$V_{OUT} \le 14~V;~t=2~\mu s/div;~V_{BAT}=3.6~V;~R_{SET}=33.2~k\Omega$

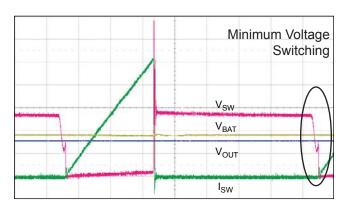

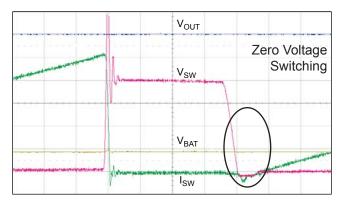

As soon as a sufficient voltage has built up at the output capacitor, the IC enters Fast-Charging Mode. In this mode, the next switching cycle starts after the secondary side current has stopped flowing, and the switch voltage has dropped to a minimum value. A proprietary circuit is used to allow minimum-voltage switching, even if the SW pin voltage does not drop to 0 V. This enables Fast-Charging Mode to start earlier than previously possible, thereby reducing the overall charging time. Minimum-voltage switching is shown in the following figure.

$V_{OUT} \ge 15~V;~t=1~\mu s/div;~V_{BAT}=3.6~V;~R_{SET}=33.2~k\Omega$

During Fast-Charging Mode, when V<sub>OUT</sub> is high enough (over 50 V), true zero-voltage switching

(ZVS) is achieved. This further improves efficiency as well as reduces switching noise. A ZVS interval is shown in the following figure.

$V_{OUT}$  = 120 V; t =0.2  $\mu$ s/div;  $V_{BAT}$  =3.6 V;  $R_{SET}$ =33.2  $k\Omega$

### IGBT Gate Driver Interlock

The TRIGGER1 and TRIGGER2 pins are ANDed together inside the IC to control the IGBT gate driver. If only one trigger signal is needed, tie both trigger pins together and use as a single input.

Triggering is disabled (locked) during charging. This is to prevent switching noise from interfering with the IGBT driver. After the CHARGE pin goes high (at the start of a charging cycle), the IC must wait for completion of the charging cycle ( $\overline{DONE}$  goes low) before

triggering can be enabled, according to the following chart:

| Con    | Resulting State |                  |

|--------|-----------------|------------------|

| CHARGE | DONE            | IGBT Gate Driver |

| Low    | Don't Care      | Enabled          |

| High   | High            | Disabled         |

| High   | Low             | Enabled          |

After completion of the charging cycle, if the charge pin is kept high and REG is enabled, the IC will periodically recharge the output. If a trigger signal comes in during a recharge cycle, charging will be halted immediately and the IGBT gate driver will be allowed to fire after a delay of less than 1 µs. Charging resumes after the trigger signal is removed.

### Red Eye Reduction

The IGBT gate driver is always enabled when CHARGE is low. If the charge pin is disabled before sufficient voltage has built up on the output capacitor, the flash may not fire. In the case of red-eye reduction flashes, it is recommended to keep the CHARGE pin low until completion of triggering pulses. This ensures that the IGBT gate driver will remain enabled regardless of the  $\overline{\rm DONE}$  state.

# **Ambient Light Sensing**

Ambient Light Sensing (ALS) can be easily implemented for the A8437 using the TRIGGER2 pin plus three external components. This configuration is shown in the figure below.

The phototransistor current is proportional to the intensity of the light that it receives. When there is sufficient ambient light (for example, during daylight outdoor photographing), a current of about 30  $\mu A$

can flow through the phototransistor. This forces the voltage at TRIGGER2 pin to fall to 0.8 V or lower, so it prohibits TRIGGER1 from firing the flash. The exact threshold of ambient light required to prohibit flash firing can be adjusted by R<sub>TGR1</sub>. The smaller this resistance, the brighter the ambient light must be to prohibit flash firing.

When ambient conditions are dark, the current flowing through the phototransistor is in less than 1  $\mu$ A. Because the TRIGGER2 pin is biased at 1.4 V or

ALS typical application (CG package shown)

higher, TRIGGER1 is allowed to activate the IGBT gate driver (and thereby fire the flash).

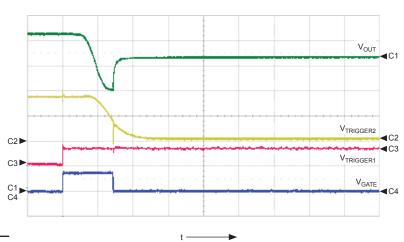

The capacitor CTGR1 and resistor RTGR1 form an integrator for light exposure. When the flash fires, bright light bounces back from subject and enters the phototransistor. In example A below, the flash terminates after just 30  $\mu$ s, without fully discharging the photoflash capacitor.

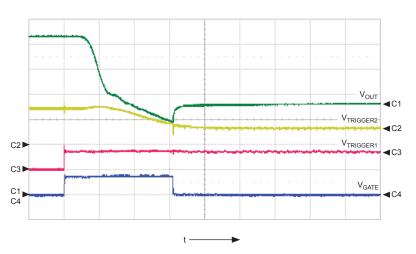

If the subject is far away, the reflected light intensity is lower, so the phototransistor current is also lower. In example B below, the flash stays on for longer time  $(60 \mu s)$  and discharges more energy from the photoflash capacitor.

Using a larger  $C_{TGR1}$  causes the time constant of the integrator to increase, so a longer pulse is required before the flash is terminated.

### Example A

|   | Common Parameters |                       |                |  |  |  |

|---|-------------------|-----------------------|----------------|--|--|--|

| Ī | Symbol            | Parameter             | Units/Division |  |  |  |

|   | C1                | V <sub>OUT</sub>      | 50 V           |  |  |  |

|   | C2                | V <sub>TRIGGER2</sub> | 1 V            |  |  |  |

|   | C3                | V <sub>TRIGGER1</sub> | 5 V            |  |  |  |

|   | C4                | $V_{GATE}$            | 5 V            |  |  |  |

| _ | t                 | time                  | 20 μs          |  |  |  |

|   |                   |                       |                |  |  |  |

### Example B

### **Transformer Selection**

1. The transformer turns ratio, N, determines the output voltage:

$$N = N_{\rm S} / N_{\rm P}$$

$$V_{\rm OUT} = 31.5 \times N - V_{\rm d} ,$$

where 31.5 is the typical value of  $V_{OUTTRIP}$ , and  $V_d$  is the forward drop of the output diode.

2. The primary inductance,  $L_P$ , determines the on-time of the switch:

$$t_{\rm on} = (-L_{\rm P}/R) \times \ln(1 - I_{\rm SWlim} \times R/V_{\rm IN})$$

,

where R is the total resistance in the primary current path (including  $R_{SWDS(on)}$  and the DC resistance of the transformer).

If  $V_{IN}$  is much larger than  $I_{SWlim} \times R$ , then  $t_{on}$  can be approximated by:

$$t_{\rm on} = I_{\rm SWlim} \times L_{\rm P} / V_{\rm IN}$$

.

3. The secondary inductance, L<sub>S</sub>, determines the off-time of the switch. Given:

$$L_{\rm S}/L_{\rm P} = N \times N$$

, then

$$t_{\rm off} = (I_{\rm SWlim}/N) \times L_{\rm S}/V_{\rm OUT}$$

$$= (I_{\rm SWlim} \times L_{\rm P} \times N)/V_{\rm OUT}.$$

The minimum pulse width for  $t_{off}$  determines what is the minimum  $L_P$  required for the transformer. For example, if  $I_{SWlim}$  = 0.7 A, N = 10, and  $V_{OUT}$  = 315 V, then  $L_P$  must be at least 9  $\mu$ H in order to keep  $t_{off}$  at 200 ns or longer. These relationships are illustrated in the figure at the bottom of the page.

In general, choosing a transformer with a larger  $L_P$  results in higher efficiency (because a larger  $L_P$  means lower switch frequency and hence lower switching loss). But transformers with a larger  $L_P$  also require more windings and larger magnetic cores. Therefore, a trade-off must be made between transformer size and efficiency.

# Component Selection

Selection of the flyback transformer should be based on the peak current, according to the following table:

| I <sub>Peak</sub> Range |          |                 | $L_P$ |

|-------------------------|----------|-----------------|-------|

| (A)                     | Supplier | Part Number     | (µH)  |

| 0.4 to 1.0              | TDK      | LDT565630T-002  | 14.5  |

| 0.6 to 1.2              | TDK      | LDT565630T-003  | 10.5  |

| 0.75 to 1.0             | TDK      | LDT565620ST-203 | 8.2   |

Application 2. Maintaining output target voltage by directly monitoring the output voltage (REG pin connected to a secondary-side resistor divider). CG package shown.

Application 3. Maintaining output voltage by *predicting* the output voltage droop (REG pin connected to primary-side RC network). CG package shown.

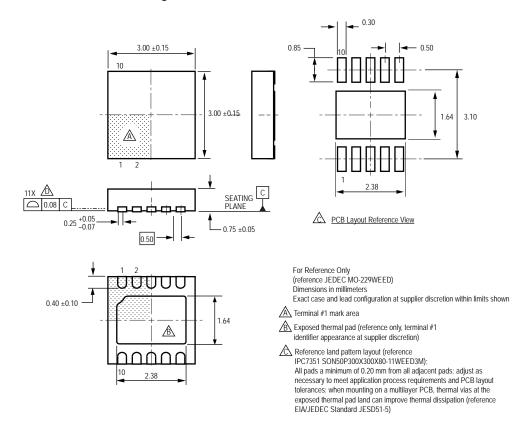

# Package CG, 12-Ball WLCSP

### Package EJ, 3 mm x 3 mm 10-Contact DFN/MLP

CG Package Marking

Line 1:

Bump A1 mark

NN – last two digits of the device number (37)

Line 2: Date code

Y – last digit of year of manufacture

WW – week of manufacture

(Marks on substrate side, exact appearance at supplier discretion)

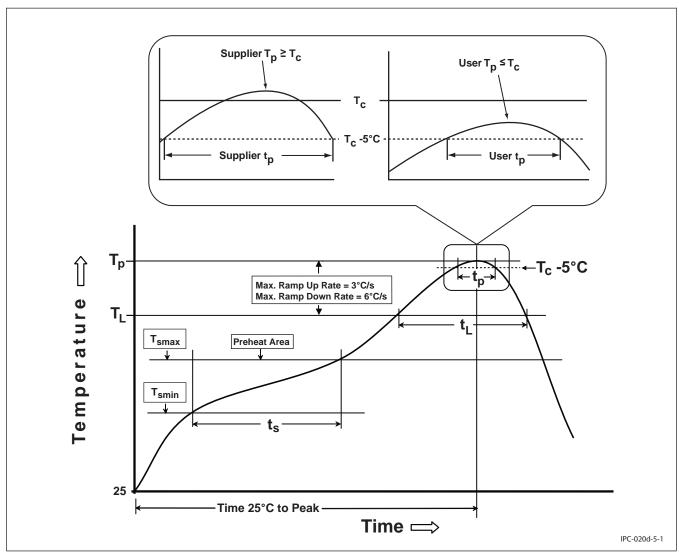

Typical Reflow Profile per J-STD-020D

JSTD020D-01, Figure 5-1 Classification Profile (Not to scale)

### Typical Reflow Profile per J-STD-020D

### JSTD020D-01 Table 5-2 Classification Reflow Profiles

| Profile Feature                                                                                                    | Sn-Pb Eutectic Assembly                                                                 | Pb-Free Assembly                                                                        |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                                                                                                    | 100 °C<br>150 °C<br>60-120 seconds                                                      | 150 °C<br>200 °C<br>60-120 seconds                                                      |

| Ramp-up rate (T <sub>L</sub> to T <sub>p</sub> )                                                                   | 3 °C/second max.                                                                        | 3 °C/second max.                                                                        |

| Liquidous temperature (T <sub>L</sub> )<br>Time (t <sub>L</sub> ) maintained above T <sub>L</sub>                  | 183 °C<br>60-150 seconds                                                                | 217 °C<br>60-150 seconds                                                                |

| Peak package body temperature (T <sub>p</sub> )                                                                    | For users T <sub>p</sub> must not exceed the Classification temp in Table 4-1.          | For users T <sub>p</sub> must not exceed the Classification temp in Table 4-2.          |

|                                                                                                                    | For suppliers T <sub>p</sub> must equal or exceed the Classification temp in Table 4-1. | For suppliers T <sub>p</sub> must equal or exceed the Classification temp in Table 4-2. |

| Time (t <sub>p</sub> )* within 5 °C of the specified classification temperature (T <sub>c</sub> ), see Figure 5-1. | 20* seconds                                                                             | 30* seconds                                                                             |

| Ramp-down rate (T <sub>p</sub> to T <sub>L</sub> )                                                                 | 6 °C/second max.                                                                        | 6 °C/second max.                                                                        |

| Time 25 °C to peak temperature                                                                                     | 6 minutes max.                                                                          | 8 minutes max.                                                                          |

| * Tolerance for peak profile temperature (T <sub>p</sub> ) is defined as a supplier minimum and a user maximum.    |                                                                                         |                                                                                         |

- Note 1: All temperatures refer to the center of the package, measured on the package body surface that is facing up during assembly reflow (e.g., live-bug). If parts are reflowed in other than the normal live-bug assembly reflow orientation (i.e., dead-bug), T<sub>p</sub> shall be within ± 2 °C of the live-bug T<sub>p</sub> and still meet the T<sub>c</sub> requirements, otherwise, the profile shall be adjusted to achieve the latter. To accurately measure actual peak package body temperatures refer to JEP140 for recommended thermocouple use.

- **Note 2:** Reflow profiles in this document are for classification/preconditioning and are not meant to specify board assembly profiles. Actual board assembly profiles should be developed based on specific process needs and board designs and should not exceed the parameters in Table 5-2.

- For example, if  $T_c$  is 260 °C and time  $t_p$  is 30 seconds, this means the following for the supplier and the user.

- For a supplier: The peak temperature must be at least 260 °C. The time above 255 °C must be at least 30 seconds.

- For a user: The peak temperature must not exceed 260 °C. The time above 255 °C must not exceed 30 seconds.

- Note 3: All components in the test load shall meet the classification profile requirements.

- Note 4: SMD packages classified to a given moisture sensitivity level by using Procedures or Criteria defined within any previous version of J-STD-020, JESD22-A112 (rescinded), IPC-SM-786 (rescinded) do not need to be reclassified to the current revision unless a change in classification level or a higher peak classification temperature is desired.

Copyright ©2006-2010, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.