### MAX14616/MAX14616A

# Micro-USB Interface Circuit Plus Intelligent Li+ Battery Chargers

### **General Description**

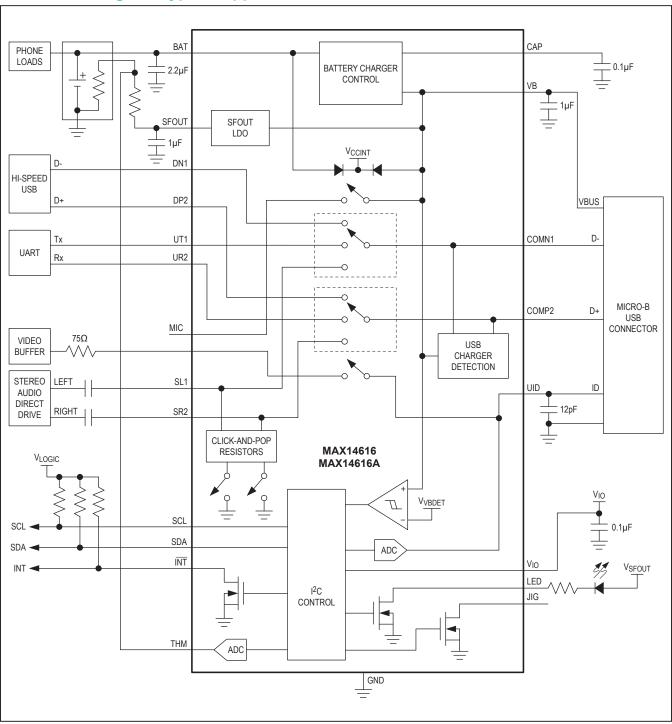

The MAX14616/MAX14616A are a complete solution for interfacing to a micro-USB connector and include an advanced charger detection block, a linear battery charger, and a switch block capable of multiplexing USB, UART, audio, and composite video signals. The devices include an LED driver for battery charge status and battery present detection.

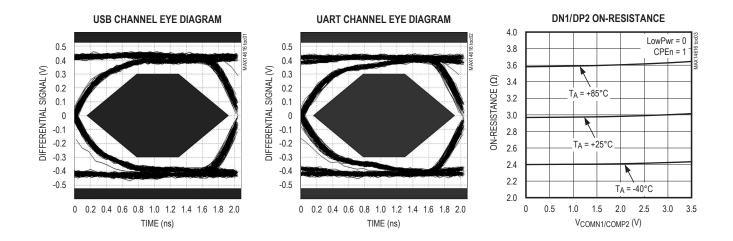

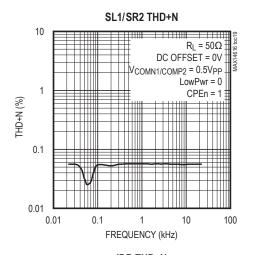

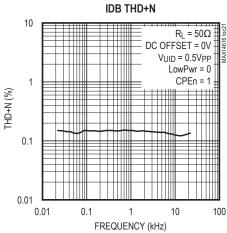

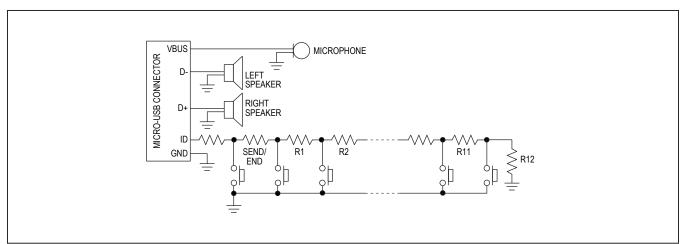

The MAX14616/MAX14616A support multiplexing USB 2.0 Hi-Speed, UART, and stereo audio signals with a single micro-USB connector. The USB channel features low  $3\Omega$  (typ) on-resistance and 7pF (typ) on capacitance to minimize USB signal degradation. The audio inputs feature negative rail signal operation down to -2V and  $0.1\Omega$  on-resistance flatness for low THD.

The MAX14616/MAX14616A charger detection block supports USB Battery Charger Detection Revision 1.1 requirements and also detects many common non-USB-defined power adapters. The SFOUT LDO provides a voltage-limited USB VBUS output for powering devices such as USB transceivers that cannot withstand high voltage. The MAX14616/MAX14616A include a composite video cable unplug detector capable of detecting the removal of a video termination resistor.

The MAX14616/MAX14616A battery charger adds a battery present detector to automatically disable the battery charger in case the battery is removed. They also include an open-drain LED driver to indicate the battery charger operation status.

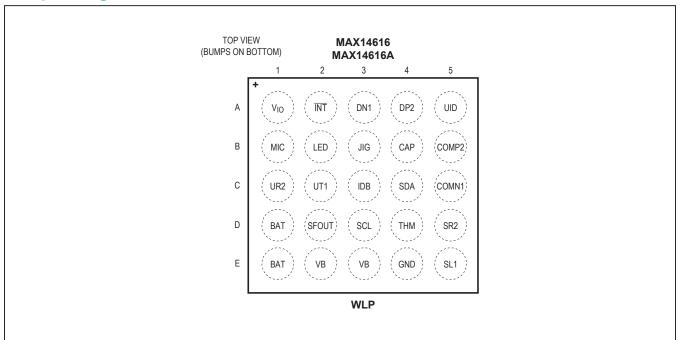

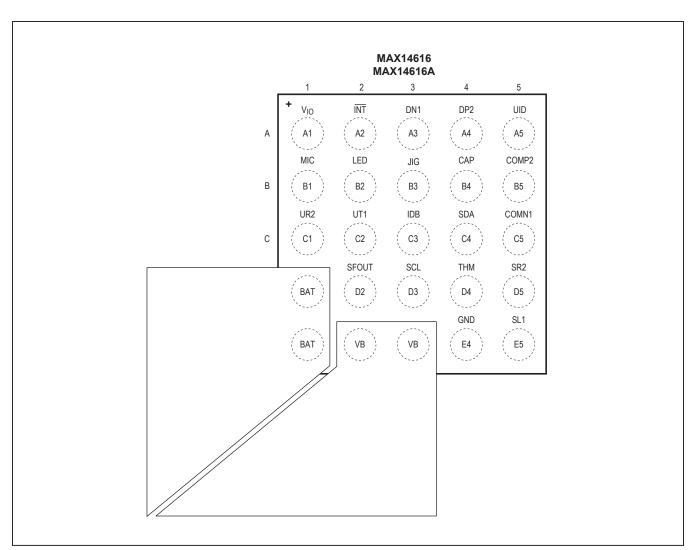

The MAX14616/MAX14616A are available in a 25-bump (2mm x 2mm, 0.4mm pitch) WLP package and operates over the -40°C to +85°C extended temperature range.

### **Applications**

- Media Players

- Cell Phones

- Digital Cameras

- eReaders

- Tablets

### **Benefits and Features**

- High Level of Integration

- Complete Solution for Micro-USB Connector Multiplexing

USB 2.0 Hi-Speed Switch with  $3\Omega$  (typ) On-Resistance

Negative-Rail Audio Inputs with Low THD Detection Logic for Accessory Identification Composite Video Load Removal Detection

- Internal Li+ Battery Charger with +28V (max) Input

- USB Battery Charger Detection

- Supports USB BC1.1 with Advanced Features from USB BC1.2

- · Data Contact Detection (DCD) Support

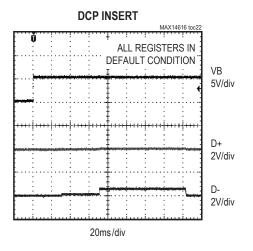

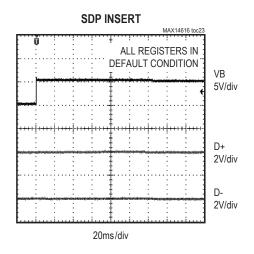

- · USB DCP, SDP, and CDP Detection

- Non-USB Defined Charger Detection Capability

- High-Voltage Protected LDO for USB Transceiver

- Charger Status LED Output Driver

- Battery Presence Monitor

- High-ESD Protection on COMN1, COMP2, and UID ±15kV for Human Body Model ±10kV for IEC 61000-4-2 Air Gap Discharge ±7kV for IEC 61000-4-2 Contact Discharge

- Saves Power in Portable Application

- · Low Supply Current

- Saves Space

- · 25-Bump, 2mm x 2mm, WLP Package

Ordering Information appears at end of data sheet.

### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)    |                                     |

|--------------------------------------|-------------------------------------|

| BAT, JIG, V <sub>IO</sub> , INT, THM | 0.3V to +6V                         |

| LED                                  |                                     |

| VB (Charger Mode)                    | 0.3V to +30V                        |

| VB (Microphone Mode) (Note 1)0.3V    | to $(V_{SWPOS} + 0.3V)$             |

| SFOUT-VB                             | +0.3V                               |

| CAP                                  | 0.3V to +4V                         |

| SDA, SCL0                            | $0.3V \text{ to } (V_{BAT} + 0.3V)$ |

| SWITCH ENABLED or CPEn = 1 (Note 1)  |                                     |

| SL1, SR2, COMN1, COMP2, UID, MIC,    |                                     |

| IDB, DN1, DP22.1V                    | to $(V_{SWPOS} + 0.3V)$             |

| UT1, UR20.3V                         | to $(V_{SWPOS} + 0.3V)$             |

| SWITCH DISABLED and CPEn = 0 (Note 2)<br>SL1, SR2, MIC, IDB, DN1, DP2, |                 |

|------------------------------------------------------------------------|-----------------|

| UT1, UR20.3V to                                                        | (VCCINT + 0.3V) |

| COMN1, COMP2, UID                                                      |                 |

| Continuous Current into COMN1, COMP2                                   | ±200mA          |

| Continuous Current into BAT, VB                                        | ±1300mA         |

| Continuous Current into All Other Bumps                                | ±100mA          |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                  |                 |

| WLP (derate 19.2mW/°C above +70°C)                                     | 1536mW          |

| Operating Temperature Range                                            | 40°C to +85°C   |

| Maximum Junction Temperature                                           | +150°C          |

| Storage Temperature Range                                              |                 |

| Soldering Temperature (reflow) (Note 3)                                | +260°C          |

|                                                                        |                 |

- Note 1:  $V_{SWPOS} = min(V_{CCINT}, +3.3V)$

- Note 2:  $V_{CCINT} = max(V_{BAT}, min(V_{VB}, +4V))$

- Note 3: The WLP package is constructed using a unique set of package techniques that impose a limit on the thermal profile that the device can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 4)**

WLP

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) ........52°C/W

Note 4: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                             | SYMBOL            |                                        | CONDITIONS                                        |     | TYP | MAX  | UNITS |

|---------------------------------------|-------------------|----------------------------------------|---------------------------------------------------|-----|-----|------|-------|

|                                       | $V_{BAT}$         |                                        |                                                   | 2.8 |     | 5.5  |       |

| Supply Voltage                        | $V_{VB}$          |                                        |                                                   | 3.5 |     | 28   | V     |

|                                       | $V_{IO}$          |                                        |                                                   | 1.6 |     | 5.5  |       |

| Allowed VB Input-Voltage Range        | $V_{VB}$          |                                        |                                                   | 0   |     | 28   | V     |

| BAT Undervoltage Lockout<br>Threshold | V <sub>UVLO</sub> |                                        |                                                   | 0.4 | 2.0 | 2.65 | V     |

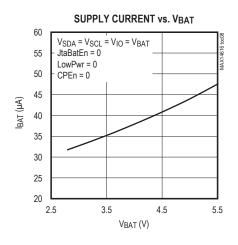

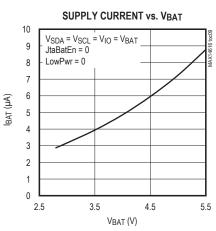

| BAT Supply Current                    |                   | $V_{BAT} = 3.6V,$<br>$V_{VB} = 0V, no$ | Low-power mode, LowPwr<br>= 1, CPEn =0, ADCEn = 0 |     | 3   | 6    |       |

|                                       |                   | accessory                              | LowPwr = 0, CPEn = 0                              |     | 28  | 50   | μA    |

|                                       |                   | attached LowPwr                        | LowPwr = 0, CPEn = 1                              |     | 45  | 65   |       |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                                        | SYMBOL                                         |                                                           | CONDITIONS                                                                    | MIN  | TYP          | MAX  | UNITS |

|--------------------------------------------------|------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|------|--------------|------|-------|

| VB Supply Current                                | h                                              | V <sub>BAT</sub> = 0V,<br>I <sub>OUT</sub> = 0mA,         | V <sub>VB</sub> = 5V, CPEn = 0,<br>MBCHOSTEN = 0, SFOUT<br>is off, UID = open |      | 350          | 500  |       |

| VB Supply Current                                | I <sub>VB</sub>                                | off MB is o                                               | $V_{VB}$ = 5V, CPEn = 0,<br>MBCHOSTEN= 0, SFOUT<br>is on, UID = open          |      | 470          | 3000 | μA    |

| V <sub>IO</sub> Supply Current                   | I <sub>IO</sub>                                | LED = unconne                                             | cted                                                                          |      | 0.1          | 1    | μΑ    |

| Internal VB Regulator Voltage                    | V <sub>PVB</sub>                               |                                                           |                                                                               | 3.3  | 4            | 5.5  | V     |

| Internal Positive Regulator Voltage for Switches | V <sub>SWPOS</sub>                             |                                                           |                                                                               | 3.3  | 3.4          | 3.5  | V     |

| Internal Negative Regulator Voltage for Switches | V <sub>SWNEG</sub>                             |                                                           |                                                                               | -2   | -1.9         | -1.8 | V     |

| CHARGER DETECTION                                |                                                |                                                           |                                                                               |      |              |      |       |

| VB-Detect-Threshold Voltage Rising               | V <sub>VBDET</sub>                             |                                                           |                                                                               | 3.2  | 3.4          | 3.6  | V     |

| VB-Detect-Threshold Voltage<br>Hysteresis        | V <sub>VBDET_HYST</sub>                        |                                                           |                                                                               |      | 0.5          |      | V     |

| DP_SRC and DM_SRC Voltage                        | V <sub>DP_SRC</sub> ,<br>V <sub>DM_SRC</sub>   | 0μA ≤ I <sub>LOAD</sub> ≤ 200μA                           |                                                                               | 0.5  | 0.6          | 0.7  | V     |

| DAT_REF Voltage                                  | V <sub>DAT_REF</sub>                           |                                                           |                                                                               | 0.25 | 0.3          | 0.35 | V     |

| LGC Voltage                                      | V <sub>LGC</sub>                               |                                                           |                                                                               | 1.15 | 1.24         | 1.3  | V     |

| DP and DM Sink Current                           | I <sub>DP_SINK</sub> ,<br>I <sub>DM_SINK</sub> | 0.15V ≤ V <sub>DP</sub> = 1                               | V <sub>DM</sub> ≤ 3.6V                                                        | 55   | 80           | 105  | μΑ    |

| DP Source Current                                | I <sub>DP_SRC</sub>                            | 0V ≤ V <sub>DP</sub> ≤ 2.5                                | /                                                                             | 5.5  | 8            | 10   | μΑ    |

| DP and DM Pulldown<br>Resistance                 | R <sub>DP_DWN</sub> ,<br>R <sub>DM_DWN</sub>   |                                                           |                                                                               | 17   | 20           | 23.3 | kΩ    |

| DP/DM Pulldown Current                           | I <sub>DP_PD</sub> ,<br>I <sub>DM_PD</sub>     | V <sub>DM</sub> = 0.15V or                                | 3.6V                                                                          | 0.01 | 0.15         | 0.5  | μA    |

|                                                  | V <sub>BUS25</sub>                             |                                                           |                                                                               | 22.5 | 25           | 27.5 |       |

| COMN1 to VB Voltage Ratio                        | V <sub>BUS47</sub>                             | V <sub>VB</sub> = 5V                                      |                                                                               | 42.3 | 47           | 51.7 | %     |

|                                                  | V <sub>BUS75</sub>                             |                                                           |                                                                               | 70   | 75           | 80   |       |

| V <sub>IO</sub> Reset Falling Threshold          | V <sub>IO_RST_TH</sub>                         |                                                           |                                                                               | 0.5  | 0.8          | 1.1  | V     |

| Battery Present Detect<br>Threshold              | V <sub>THM</sub>                               | % of V <sub>SFOUT</sub>                                   | V <sub>THM</sub> rising<br>V <sub>THM</sub> falling                           | 18.0 | 18.5<br>18.3 | 19.0 | %     |

| ACCESSORY DETECTION                              | l                                              | I                                                         | 1111111                                                                       |      |              |      |       |

| UID Low-Power Pullup Voltage                     | V <sub>UID_PU</sub>                            | $V_{BAT} = 3.6V, V_{V}$                                   | <sub>/B</sub> = 0V, LowPwr = 1                                                |      | 1.6          |      | V     |

| UID Low-Power Threshold<br>Voltage               | V <sub>UID_LP</sub>                            | V <sub>BAT</sub> = 3.6V, V <sub>VB</sub> = 0V, LowPwr = 1 |                                                                               | 0.4  | 0.7          | 1    | V     |

| UID Low-Power Pullup Resistance                  | R <sub>UID_LP</sub>                            |                                                           |                                                                               | 2    | 3.4          |      | МΩ    |

| ADC Low Threshold                                | R <sub>ADCLow</sub>                            |                                                           |                                                                               | 32   | 40           | 49   | Ω     |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER               | SYMBOL           | CONDITIONS                         | MIN    | TYP   | MAX    | UNITS |

|-------------------------|------------------|------------------------------------|--------|-------|--------|-------|

|                         |                  | V <sub>UID</sub> = 2.55V and 0.9V  | 2.19   | 2.28  | 2.37   |       |

|                         |                  | V <sub>UID</sub> = 2.50V and 0.76V | 5.756  | 6     | 6.24   |       |

| ADC ID Bullium Current  | 1                | V <sub>UID</sub> = 2.35V and 0.70V | 16.032 | 16.7  | 17.368 | μΑ    |

| ADC ID Pullup Current   | I <sub>PUP</sub> | V <sub>UID</sub> = 2.20V and 0.57V | 45.214 | 47    | 48.786 |       |

|                         |                  | V <sub>UID</sub> = 2.12V and 0.05V | 146.88 | 153   | 159.12 |       |

|                         |                  | V <sub>UID</sub> = 2.04V and 0.05V | 2.235  | 2.5   | 2.735  | mA    |

|                         |                  | GND                                | 0      |       | 0.032  |       |

|                         |                  | R <sub>VID</sub>                   | 0.049  | 0.075 | 0.472  |       |

|                         |                  | 1kΩ resistor                       | 0.531  | 1     | 1.433  |       |

|                         |                  | R1                                 | 1.722  | 2     | 2.112  |       |

|                         |                  | R2                                 | 2.465  | 2.604 | 2.684  |       |

|                         |                  | R3                                 | 3.091  | 3.208 | 3.35   |       |

|                         |                  | R4                                 | 3.826  | 4.014 | 4.11   |       |

|                         |                  | R5                                 | 4.67   | 4.82  | 5.05   |       |

|                         |                  | R6                                 | 5.73   | 6.03  | 6.54   |       |

|                         |                  | R7                                 | 7.39   | 8.03  | 8.43   |       |

|                         |                  | R8                                 | 9.5    | 10.03 | 10.31  |       |

|                         |                  | R9                                 | 11.6   | 12.03 | 12.69  |       |

|                         |                  | R10                                | 14.03  | 14.46 | 14.77  |       |

|                         |                  | R11                                | 16.76  | 17.26 | 17.61  |       |

|                         |                  | R12                                | 19.92  | 20.5  | 20.79  | kΩ    |

|                         |                  | R13                                | 23.49  | 24.07 | 24.63  |       |

| ADC Detection Resistors | Pana             | R14                                | 27.8   | 28.7  | 29.3   |       |

| ADC Detection Resistors | R <sub>ADC</sub> | R15                                | 33     | 34    | 34.7   | K22   |

|                         |                  | R16                                | 39     | 40.2  | 43     |       |

|                         |                  | R17                                | 49.6   | 49.9  | 53.4   |       |

|                         |                  | R18                                | 60.4   | 64.9  | 67.6   |       |

|                         |                  | R19                                | 76.3   | 80.07 | 84.9   |       |

|                         |                  | R20                                | 95.6   | 102   | 104    |       |

|                         |                  | R21                                | 117    | 121   | 129    |       |

|                         |                  | R22                                | 143    | 150   | 153    |       |

|                         |                  | R23                                | 173    | 200   | 212    |       |

|                         |                  | R24                                | 239    | 255   | 260    |       |

|                         |                  | R25                                | 293    | 301   | 312    |       |

|                         |                  | R26                                | 350    | 365   | 384    |       |

|                         |                  | R27                                | 425    | 442   | 450    |       |

|                         |                  | R28                                | 508    | 523   | 533    |       |

|                         |                  | R29                                | 601    | 619   | 655    |       |

|                         |                  | R30                                | 737    | 1000  | 1032   |       |

|                         |                  | Open                               | 1158   |       |        |       |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                            | SYMBOL                              | CONDITIONS                                                                                                                                                                                              | MIN  | TYP | MAX                | UNITS |

|--------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|-------|

| USB ANALOG SWITCH (DN1, I            | DP2)                                |                                                                                                                                                                                                         |      |     | '                  |       |

| Apolog Signal Panga                  | \/ <b>-</b> \/==                    | RUID = open, LowPwr = 1 and CPEn = 0 (Note 2)                                                                                                                                                           | 0    |     | V <sub>CCINT</sub> | V     |

| Analog Signal Range                  | V <sub>DN1</sub> , V <sub>DP2</sub> | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1 (Note 1)                                                                                                                                                     | 0    |     | V <sub>SWPOS</sub> | V     |

| On-Resistance                        | R <sub>ONUSB</sub>                  | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $0V \le V_{COMN1}$ , $V_{COMP2} \le 3.0V$                                                               |      | 3   | 6                  | Ω     |

| On-Resistance Match Between Channels | ΔR <sub>ONUSB</sub>                 | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $V_{COMN1}$ , $V_{COMP2}$ = 400mV                                                                       |      |     | 0.5                | Ω     |

| On-Resistance Flatness               | R <sub>FLATUSB</sub>                | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $0V \le V_{COMN1}$ , $V_{COMP2} \le 3.3V$                                                               |      | 0.1 | 0.3                | Ω     |

| Off-Leakage Current                  | ILUSB (OFF)                         | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 4.2V, switch open, V <sub>DN1</sub> , V <sub>DP2</sub> = 0.3V or 2.5V and V <sub>COMN1</sub> , V <sub>COMP2</sub> = 2.5V or 0.3V | -360 |     | +360               | nA    |

| On-Leakage Current                   | l <sub>USB(ON)</sub>                | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 4.2V, switch closed, V <sub>DN1</sub> , V <sub>DP2</sub> = 0.3V or 2.5V                                                          | -360 |     | +360               | nA    |

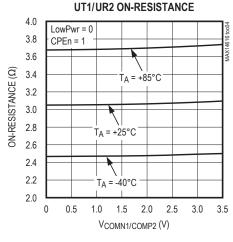

| UART ANALOG SWITCHES (U              | T1, UR2)                            |                                                                                                                                                                                                         |      |     |                    |       |

| Analog Signal Range                  | V V                                 | RUID = open, LowPwr = 1 and CPEn = 0 (Note 2)                                                                                                                                                           | 0    |     | V <sub>CCINT</sub> | V     |

| Arialog Signal Nange                 | V <sub>UT1</sub> , V <sub>UR2</sub> | (RUID < $1050$ kΩ or LowPwr = 0) and CPEn = 1 (Note 1)                                                                                                                                                  | 0    |     | V <sub>SWPOS</sub> | V     |

| On-Resistance                        | R <sub>ONUART</sub>                 | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $0V \le V_{COMN1}$ , $V_{COMP2} \le 3.0V$                                                               |      | 3   | 6                  | Ω     |

| On-Resistance Match Between Channels | ΔRONUART                            | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 3.0V, I <sub>COMN1</sub> , I <sub>COMP2</sub> = 10mA, V <sub>COMN1</sub> , V <sub>COMP2</sub> = 1.5V                             |      |     | 0.5                | Ω     |

| On-Resistance Flatness               | R <sub>FLATUART</sub>               | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $0V \le V_{COMN1}$ , $V_{COMP2} \le 3.0V$                                                               |      | 0.1 | 0.3                | Ω     |

| Off-Leakage Current                  | I <sub>LUART(OFF)</sub>             | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 4.2V, switch open, V <sub>UT1</sub> , V <sub>UR2</sub> = 0.3V or 2.5V and V <sub>COMN1</sub> , V <sub>COMP2</sub> = 2.5V or 0.3V | -360 |     | +360               | nA    |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                            | SYMBOL                  | CONDITIONS                                                                                                                                                                  | MIN                | TYP | MAX                | UNITS |

|--------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-------|

| On-Leakage Current                   | I <sub>LUART</sub> (ON) | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 4.2V, switch closed, $V_{UT1}$ , $V_{UR2}$ = 0.3V or 2.5V                                                           | -360               |     | +360               | nA    |

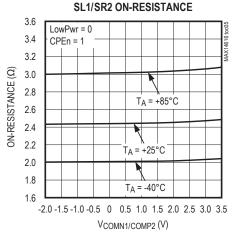

| <b>AUDIO ANALOG SWITCHES (S</b>      | SL1, SR2)               |                                                                                                                                                                             |                    |     |                    |       |

| Analog Cianal Danas                  | .,,                     | RUID = open, LowPwr = 1 and CPEn = 0 (Note 2)                                                                                                                               | 0                  |     | V <sub>CCINT</sub> |       |

| Analog Signal Range                  | Vaudio                  | (RUID < $1050$ kΩ or LowPwr=0) and CPEn = 1 (Note 1)                                                                                                                        | V <sub>SWNEG</sub> |     | V <sub>SWPOS</sub> | V     |

| On-Resistance                        | R <sub>ONA</sub>        | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $0V \le V_{COMN1}$ , $V_{COMP2} \le 3.0V$                                   |                    | 3   | 6                  | Ω     |

| On-Resistance Match Between Channels | ΔR <sub>ONA</sub>       | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 3.0V, I <sub>COMN1</sub> , I <sub>COMP2</sub> = 10mA, V <sub>COMN1</sub> , V <sub>COMP2</sub> = 1.5V |                    |     | 0.5                | Ω     |

| On-Resistance Flatness               | R <sub>FLATA</sub>      | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{COMN1}$ , $I_{COMP2}$ = 10mA, $0V \le V_{COMN1}$ , $V_{COMP2} \le 3.0V$                                   |                    | 0.1 | 0.3                | Ω     |

| Audio Off-Leakage Current            | I <sub>LA(OFF)</sub>    | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 4.2V, switch open, $V_{SL1}$ , $V_{SR2}$ = 0.3V or 2.5V, $V_{COMN1}$ , $V_{COMP2}$ = 2.5V or 0.3V                   | -360               |     | +360               | nA    |

| Audio On-Leakage Current             | I <sub>LA(ON)</sub>     | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 4.2V, switch closed, V <sub>SL1</sub> , V <sub>SR2</sub> = 0.3V or 2.5V                              | -360               |     | +360               | nA    |

| Shunt Resistor                       | RSHUNT                  | I <sub>SHUNT</sub> = 10mA                                                                                                                                                   | 30                 | 100 | 170                | Ω     |

| MIC ANALOG SWITCHES (MIC             | ;)                      |                                                                                                                                                                             |                    |     |                    |       |

| Analog Signal Danga                  | V <sub>2</sub>          | RUID = open, LowPwr = 1 and CPEn = 0 (Note 2)                                                                                                                               | 0                  |     | V <sub>CCINT</sub> | V     |

| Analog Signal Range                  | V <sub>MIC</sub>        | (RUID < $1050$ kΩ or LowPwr = 0) and CPEn = 1                                                                                                                               | 0                  |     | 2.5                | V     |

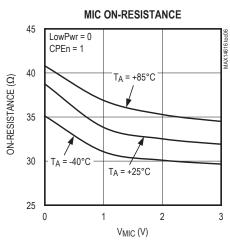

| On-Resistance                        | R <sub>ONMIC</sub>      | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 3.0V, I <sub>MIC</sub> = 10mA, 0V ≤ V <sub>MIC</sub> ≤ 3.0V                                          |                    | 30  | 50                 | Ω     |

| On-Resistance Flatness               | R <sub>FLATMIC</sub>    | (RUID < 1050k $\Omega$ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 3.0V, I <sub>MIC</sub> = 10mA, 0V ≤ V <sub>MIC</sub> ≤ 3.0V                                          |                    | 3   | 10                 | Ω     |

| MIC Off-Leakage Current              | ILMIC(OFF)              | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 4.2V, switch open, $V_{MIC}$ = 0.3V or 2.5V, $V_{VB}$ = 2.5V or 0.3V                                                | -360               |     | +360               | nA    |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                     | SYMBOL                                                       | CONDITIONS                                                                                                                                               | MIN                | TYP   | MAX                | UNITS |

|-------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|--------------------|-------|

| MIC On-Leakage Current        | I <sub>LMIC(ON)</sub>                                        | (RUID < $1050$ kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 4.2V, switch closed, $V_{MIC}$ = 0.3V or 2.5V                                                 |                    | 32    | 60                 | μA    |

| ID BYPASS ANALOG SWITCH       | (IDB)                                                        |                                                                                                                                                          |                    |       |                    |       |

| Angles Signal Dangs           | V                                                            | RUID = open, LowPwr = 1 and CPEn = 0 (Note 2)                                                                                                            | 0                  |       | V <sub>CCINT</sub> | V     |

| Analog Signal Range           | V <sub>IDB</sub>                                             | (RUID < $1050$ kΩ or LowPwr = 0) and CPEn =1                                                                                                             | V <sub>SWNEG</sub> |       | V <sub>SWPOS</sub> | V     |

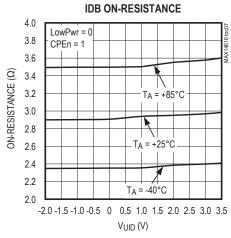

| On-Resistance                 | RONIDB                                                       | (RUID < $1050$ kΩ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = $3.0$ V, I <sub>IDB</sub> = $10$ mA, $0$ V ≤ V <sub>IDB</sub> ≤ $2.5$ V                |                    | 3     | 6                  | Ω     |

| On-Resistance Flatness        | R <sub>FLATIDB</sub>                                         | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 3.0V, $I_{IDB}$ = 10mA, $0V \le V_{IDB} \le$ 2.5V                                                |                    | 0.1   | 0.3                | Ω     |

| IDB Off-Leakage Current       | I <sub>LIDB</sub> (OFF)                                      | (RUID < $1050$ kΩ or LowPwr = 0) and CPEn = 1, V <sub>BAT</sub> = 4.2V, switch open, V <sub>IDB</sub> = 0.3V or 2.5V and V <sub>UID</sub> = 2.5V or 0.3V | -360               |       | +360               | nA    |

| IDB On-Leakage Current        | I <sub>LIDB(ON)</sub>                                        | (RUID < 1050kΩ or LowPwr = 0) and CPEn = 1, $V_{BAT}$ = 4.2V, switch closed, $V_{IDB}$ = 0.3V or 2.5V                                                    | -360               |       | +360               | nA    |

| DIGITAL SIGNALS (INT, SCL,    | SDA, JIG, BOO                                                | Γ, LED)                                                                                                                                                  |                    |       |                    |       |

| Input Logic-High              | VIH                                                          |                                                                                                                                                          | 1.4                |       |                    | V     |

| Input Logic-Low               | V <sub>IL</sub>                                              |                                                                                                                                                          |                    |       | 0.4                | V     |

| Input Leakage Current         | INLEAK                                                       |                                                                                                                                                          | -250               |       | +250               | nA    |

| Open-Drain Output-Voltage Low | V <sub>INTL</sub> , V <sub>JIGL</sub> ,<br>V <sub>LEDL</sub> | I <sub>SINK</sub> = 3mA                                                                                                                                  |                    |       | 0.4                | V     |

| DYNAMIC PERFORMANCE           |                                                              |                                                                                                                                                          |                    |       |                    |       |

| Analog Switch Turn-On Time    | toN                                                          | I <sup>2</sup> C STOP to switch on, $R_L = 50\Omega$                                                                                                     |                    | 0.2   | 0.5                | ms    |

| Analog Switch Turn-Off Time   | toff                                                         | I <sup>2</sup> C STOP to switch off, $R_L = 50Ω$                                                                                                         |                    | 0.1   | 0.5                | ms    |

| Break-Before-Make Delay Time  | t <sub>BBM</sub>                                             | $R_L = 50\Omega$ , $T_A = +25^{\circ}C$ (Note 6)                                                                                                         | 0                  |       |                    | μs    |

| MUIC Clock Period             | t <sub>CK</sub>                                              |                                                                                                                                                          |                    | 14.64 |                    | μs    |

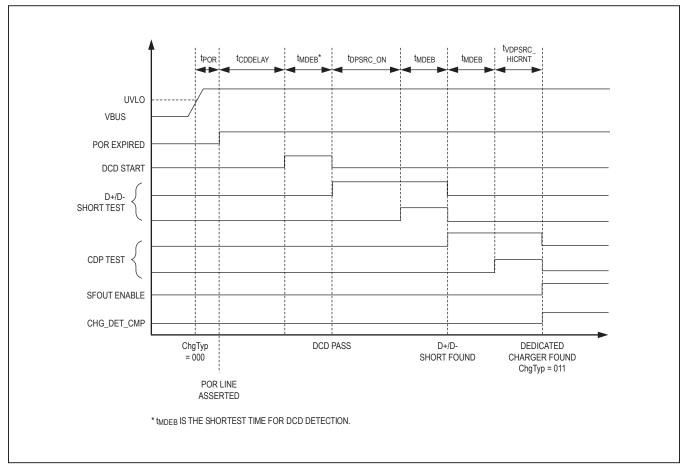

| USB Charger Detect Time       | tDPSRC_ON                                                    |                                                                                                                                                          | 40                 | 46    | 60                 | ms    |

| JIG Assertion Time            |                                                              | Resistor attached to ID until JIG assert (Note 7)                                                                                                        |                    | 0.5   |                    | ms    |

| Charger Detect Current Delay  | tVDPSRC_HICRNT                                               |                                                                                                                                                          | 46                 |       | 60                 | ms    |

| VBUS Debounce Time            | t <sub>MDEB</sub>                                            |                                                                                                                                                          | 20                 | 30    | 40                 | ms    |

| DCD Debounce Time             |                                                              |                                                                                                                                                          | 36                 | 40    | 44                 | ms    |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                               | SYMBOL                      | CONDIT                                                                                            | IONS                                                                                                                |                 | MIN | TYP  | MAX               | UNITS |

|-----------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------|-----|------|-------------------|-------|

| DOD Time and                            |                             | DCDCpl = 0                                                                                        |                                                                                                                     |                 | 1.8 | 2    | 2.2               | sec   |

| DCD Timeout                             |                             | DCDCpl = 1                                                                                        |                                                                                                                     |                 |     |      | 900               | ms    |

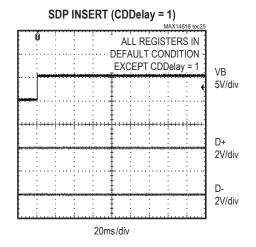

| Charger Detection Delay<br>Timeout      |                             | CDDelay = 1                                                                                       | CDDelay = 1                                                                                                         |                 |     | 500  |                   | ms    |

| COMN1, COMP2<br>On Capacitance          | CONCOM                      | Applied voltage is 0.5V <sub>F</sub><br>f = 240MHz, COMN1/CO<br>DN1/DP2                           | -                                                                                                                   |                 |     | 7    |                   | pF    |

| UID On Capacitance                      | C <sub>ONUID</sub>          |                                                                                                   | Applied voltage is 0.5V <sub>PP</sub> , DC bias = 0V, f = 1MHz, UID connected to MIC                                |                 |     | 7    |                   | pF    |

|                                         |                             |                                                                                                   |                                                                                                                     | UT1, UR2        |     | 3    |                   |       |

| Off Canacitanas                         | 0                           | Applied voltage is 0.5V <sub>F</sub>                                                              | P,                                                                                                                  | DN1, DP2        |     | 3    |                   |       |

| Off Capacitance                         | C <sub>OFF</sub>            | DC bias = 0V,<br>f = 1MHz                                                                         |                                                                                                                     | MIC             |     | 3    |                   | pF    |

|                                         |                             |                                                                                                   |                                                                                                                     | IDB             |     | 3    |                   |       |

| Off-Isolation                           |                             | $R_L = 50\Omega$ , $f = 20kHz$ ,<br>$V_{COMN1}$ , $V_{COMP2} = 0.5V_{PP}$ UT1, UR2                |                                                                                                                     |                 | -60 |      | dB                |       |

| MIC Isolation                           |                             | · · · · · · · · · · · · · · · · · · ·                                                             | BAT to MIC, MIC to UID switch enabled,<br>$R_L = 600\Omega$ , $100Hz \le f \le 6kHz$ ,<br>$V_{RAT} = 3.6V \pm 0.5V$ |                 |     | 80   |                   | dB    |

| BAT Supply PSRR                         |                             | Noise from BAT to COMN1, COMP2 or MIC, $R_L = 50\Omega$ , $f = 10kHz$ , $V_{BAT} = 3.6V \pm 0.2V$ |                                                                                                                     |                 |     | 90   |                   | dB    |

| Crosstalk                               |                             | Any switch to any switch f = 20kHz, V <sub>COMN1</sub> , V <sub>C</sub>                           |                                                                                                                     |                 |     | 100  |                   | dB    |

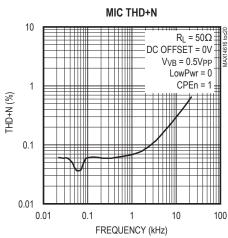

| MIC Total Harmonic Distortion           | THD                         | MIC channel, $20Hz \le f \le V_{COMP2} = 0.5V_{PP}$ , $R_L = T_A = +25^{\circ}C$                  |                                                                                                                     |                 |     | 0.05 |                   | %     |

| BATTERY CHARGER (V <sub>VB</sub> = 5)   | /, V <sub>BAT</sub> = 4V, 1 | Γ <sub>A</sub> = -40°C to +85°C, unle                                                             | ss ot                                                                                                               | herwise specifi | ed) |      |                   |       |

| VBUS Charger Operating Range            | V <sub>BUSOP</sub>          |                                                                                                   |                                                                                                                     |                 | 4.0 |      | V <sub>OVLO</sub> | V     |

|                                         |                             | V <sub>VB</sub> – V <sub>BAT</sub> , rising                                                       |                                                                                                                     |                 | 150 | 250  | 350               |       |

| VBUSOK Trip Point                       | $V_{BTP}$                   | V <sub>VB</sub> – V <sub>BAT</sub> , falling                                                      |                                                                                                                     |                 | 20  | 45   | 100               | mV    |

|                                         |                             | V <sub>VB</sub> – V <sub>BAT</sub> , hysteresis                                                   |                                                                                                                     |                 |     | 205  |                   |       |

| Input-Undervoltage Threshold            | $V_{BUVLO}$                 | VB rising                                                                                         |                                                                                                                     |                 | 3.8 | 3.9  | 4.0               | V     |

| Input-Undervoltage Threshold Hysteresis |                             |                                                                                                   |                                                                                                                     |                 |     | 600  |                   | mV    |

|                                         |                             | ОТ                                                                                                | PCGI                                                                                                                | HCVS = 00       | 7.1 | 7.5  | 7.8               |       |

| Input-Overvoltage Protection            | tion V <sub>OVLO</sub> V    | OT OT                                                                                             | PCGI                                                                                                                | HCVS = 01       | 6.0 |      |                   | V     |

| hreshold                                |                             | VB rising OTPCGHCVS = 10                                                                          |                                                                                                                     |                 | 6.5 |      | ] '               |       |

|                                         |                             | ОТ                                                                                                | PCGI                                                                                                                | HCVS = 11       |     | 7.0  |                   |       |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                              | SYMBOL              | CON                                          | DITIONS                                       | MIN   | TYP  | MAX   | UNITS |

|----------------------------------------|---------------------|----------------------------------------------|-----------------------------------------------|-------|------|-------|-------|

| Input-Overvoltage Threshold Hysteresis | Vovlo_HYS           |                                              |                                               |       | 200  |       | mV    |

| CEOLIT I DO Voltogo                    |                     | V <sub>VB</sub> = 6.0V, I <sub>SFOUT</sub>   | = 0mA                                         | 5.0   | 5.25 | 5.5   | V     |

| SFOUT LDO Voltage                      | Vsfout              | V <sub>VB</sub> = 5.0V, I <sub>SFOUT</sub>   | = 15mA                                        |       | 4.9  |       | ] v   |

| VB to BAT Input Resistance             |                     | V <sub>VB</sub> = 4.1V, V <sub>BAT</sub> = 4 | 1.0V                                          |       | 0.5  |       | Ω     |

| BAT Battery Regulation Voltage         |                     | $I_{BAT} = 5mA$ ,                            | T <sub>A</sub> = +25°C                        | 4.179 | 4.2  | 4.221 | V     |

| DAT Dattery Negulation Voltage         |                     | MBCCVWRC = 0000                              | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | 4.158 | 4.2  | 4.242 | V     |

| BAT Regulation Programmable            | V <sub>BATREG</sub> | $I_{BAT} = 5mA$                              | MBCCVWRC = 0001                               |       | 4.0  |       | V     |

| Range                                  | VBAIREG             | (Note 8)                                     | MBCCVWRC = 1111                               |       | 4.35 |       |       |

| BAT Restart Fast-Charge<br>Threshold   | V <sub>BATRS</sub>  | From BAT regulation when AUTOSTOP is         |                                               | -150  |      | mV    |       |

| BAT Restart Fast-Charge<br>Debounce    |                     |                                              |                                               |       | 62   |       | ms    |

|                                        |                     | V <sub>BAT</sub> = 3.5V                      | MBCICHWRCL = 0                                |       | 90   |       |       |

|                                        |                     |                                              | MBCICHWRCH = 0000                             |       | 200  |       |       |

|                                        |                     |                                              | MBCICHWRCH = 0001                             |       | 250  |       |       |

|                                        |                     |                                              | MBCICHWRCH = 0010                             |       | 300  |       | 1     |

|                                        |                     |                                              | MBCICHWRCH = 0011                             |       | 350  |       |       |

|                                        |                     |                                              | MBCICHWRCH = 0100                             |       | 400  |       |       |

|                                        |                     |                                              | MBCICHWRCH = 0101                             | 414   | 450  | 486   | ]     |

|                                        |                     |                                              | MBCICHWRCH = 0110                             |       | 500  |       |       |

| Battery Fast-Charge Current            | I <sub>BAT</sub>    | $V_{BAT} = 3.5V,$                            | MBCICHWRCH = 0111                             |       | 550  |       | mA    |

|                                        |                     |                                              | MBCICHWRCH = 1000                             |       | 600  |       | 1     |

|                                        |                     |                                              | MBCICHWRCH = 1001                             |       | 650  |       |       |

|                                        |                     |                                              | MBCICHWRCH = 1010                             |       | 700  |       | 1     |

|                                        |                     |                                              | MBCICHWRCH = 1011                             |       | 750  |       |       |

|                                        |                     |                                              | MBCICHWRCH = 1100                             |       | 800  |       | 1     |

|                                        |                     |                                              | MBCICHWRCH = 1101                             |       | 850  |       | 1     |

|                                        |                     |                                              | MBCICHWRCH = 1110                             |       | 900  |       | 1     |

|                                        |                     |                                              | MBCICHWRCH = 1111                             |       | 950  |       | 1     |

## **Electrical Characteristics (continued)**

( $V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                             | SYMBOL              | CON                                        | IDITIONS                  | MIN | TYP  | MAX | UNITS |  |

|---------------------------------------|---------------------|--------------------------------------------|---------------------------|-----|------|-----|-------|--|

|                                       |                     |                                            | EOCS = 0000               |     | 50   |     |       |  |

|                                       |                     |                                            | EOCS = 0001               |     | 60   |     |       |  |

|                                       |                     |                                            | EOCS = 0010               |     | 70   |     |       |  |

|                                       |                     |                                            | EOCS = 0011               |     | 80   |     |       |  |

|                                       |                     |                                            | EOCS = 0100               |     | 90   |     |       |  |

| Battery End-of-Charge<br>Threshold    |                     |                                            | EOCS = 0101               |     | 100  |     |       |  |

|                                       |                     |                                            | EOCS = 0110               |     | 110  |     | ]     |  |

|                                       |                     | I <sub>BAT</sub> falling, battery          | EOCS = 0111               |     | 120  |     |       |  |

|                                       | IBAT_STOP           | is charged                                 | EOCS = 1000               |     | 130  |     | mA    |  |

|                                       |                     |                                            | EOCS = 1001               |     | 140  |     |       |  |

|                                       |                     |                                            | EOCS = 1010               |     | 150  |     |       |  |

|                                       |                     |                                            | EOCS = 1011               |     | 160  |     |       |  |

|                                       |                     |                                            | EOCS = 1100               |     | 170  |     |       |  |

|                                       |                     |                                            | EOCS = 1101               |     | 180  |     |       |  |

|                                       |                     |                                            | EOCS = 1110               |     | 190  |     |       |  |

|                                       |                     |                                            | EOCS = 1111               |     | 200  |     |       |  |

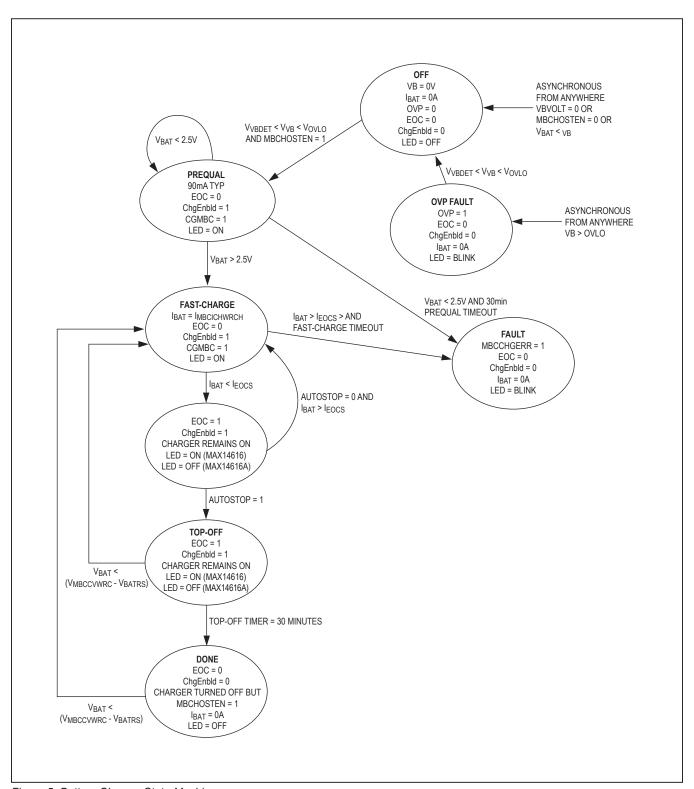

| VB Prequalification Charge<br>Current | IPRECHG             | V <sub>BAT</sub> = 2V, V <sub>VB</sub> = 5 | V                         |     | 93   |     | mA    |  |

| Battery Charger Soft-Start Time       |                     | Ramp time from 93n                         | nA to fast-charge current |     | 1.2  |     | ms    |  |

| Precharge Threshold                   | V <sub>PRECHG</sub> |                                            |                           |     | 2.5  |     | V     |  |

| Precharge Threshold<br>Hysteresis     |                     |                                            |                           |     | 170  |     | mV    |  |

| Precharge Watchdog Timeout            |                     |                                            |                           |     | 30   |     | min   |  |

|                                       |                     | TCHW = 000,001, 0                          | 10, 101, or 110           |     | 5    |     |       |  |

| Fast-Charge Timer                     |                     | TCHW = 011                                 |                           |     | 6    |     | Hour  |  |

|                                       |                     | TCHW = 100                                 |                           |     | 7    |     | ]     |  |

| Top-Off Timer                         |                     |                                            |                           |     | 30   |     | min   |  |

| Die Temperature Thermal Limit         | TJ                  | Die temperature risi                       | ng (Note 9)               |     | +105 |     | °C    |  |

### **Electrical Characteristics (continued)**

$(V_{BAT}$  = 2.8V to 5.5V,  $V_{VB}$  = 3.5V to 5.5V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = 3.6V,  $V_{VB}$  = 5.0V,  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                                       | SYMBOL           | CONDITIONS               | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|------------------|--------------------------|-----|-----|-----|-------|

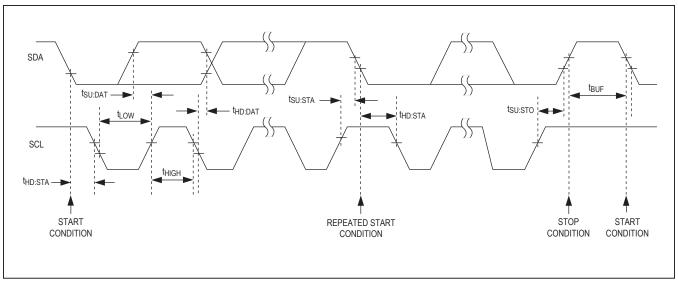

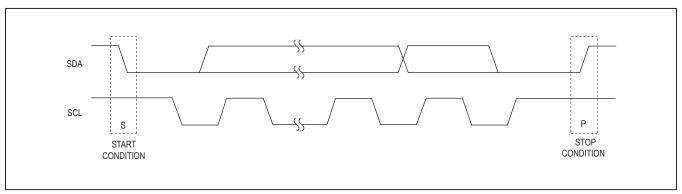

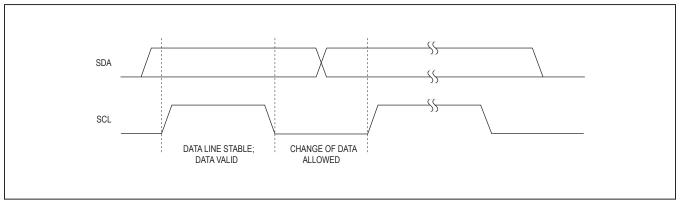

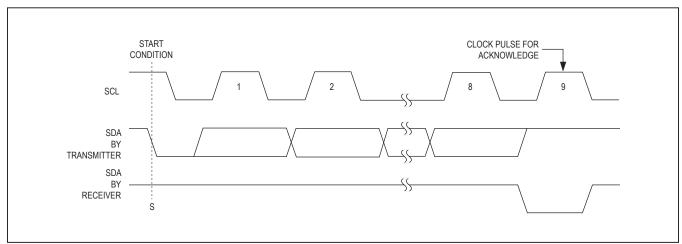

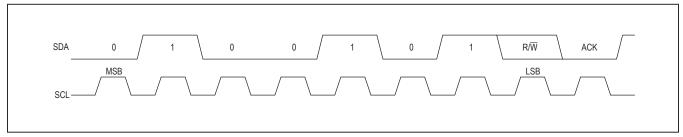

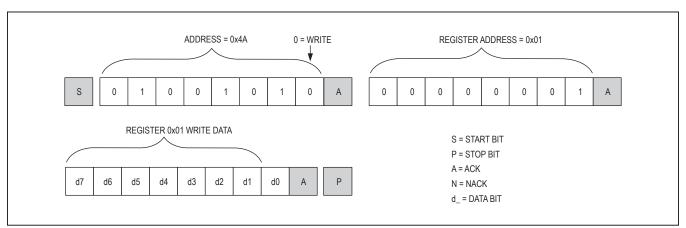

| I <sup>2</sup> C TIMING SPECIFICATIONS (        | Figure 1)        |                          |     |     |     |       |

| I <sup>2</sup> C Maximum Clock Frequency        | fl2CCLK          |                          |     | 400 |     | kHz   |

| Bus Free Time Between STOP and START Conditions | <sup>t</sup> BUF |                          | 1.3 |     |     | μs    |

| Repeated Start (SR) Condition<br>Setup Time     | tsu:sta          | 90% to 90%               | 0.6 |     |     | μs    |

| START Condition Hold Time                       | thd:sta          | 10% of SDA to 90% of SCL | 0.6 |     |     | μs    |

| STOP Condition Setup Time                       | tsu:sto          | 90% of SCL to 10% of SDA | 0.6 |     |     | μs    |

| Clock Low Period                                | t <sub>LOW</sub> | 10% to 10%               | 1.3 |     |     | μs    |

| Clock High Period                               | tHIGH            | 90% to 90%               | 0.6 |     |     | μs    |

| Data Valid to SCL Rise Time                     | tsu:dat          | Data setup time          | 100 |     |     | ns    |

| Data Setup Time to SCL Fall                     | thd:dat          | Data hold time           | 0   |     |     | ns    |

| ESD PROTECTION                                  |                  |                          |     |     |     |       |

|                                                 |                  | Human Body Model         |     | ±15 |     |       |

| COMN1, COMP2, UID, BC                           |                  | IEC61000-4-2 Air Gap     |     | ±10 |     | kV    |

|                                                 |                  | IEC61000-4-2 Contact     |     | ±7  |     |       |

| All Other Pins                                  |                  | Human Body Model         |     | ±2  |     | kV    |

- Note 5: All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

- Note 6: Not production tested. Guaranteed by design.

- Note 7: The JIG assertion time is a function of the ADC debounce time. Set the ADCDbSet bits in the CONTROL3 register to adjust this delay.

- Note 8: Set the MBCCVWRC bits in the CHGCTRL3 register to adjust the battery regulation voltage, VBATREG.

- Note 9: The battery charge current is reduced when the die temperature reaches this limit.

Figure 1. I<sup>2</sup>C Timing Diagram

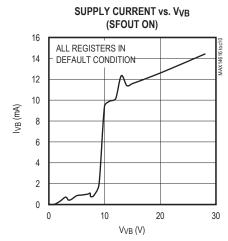

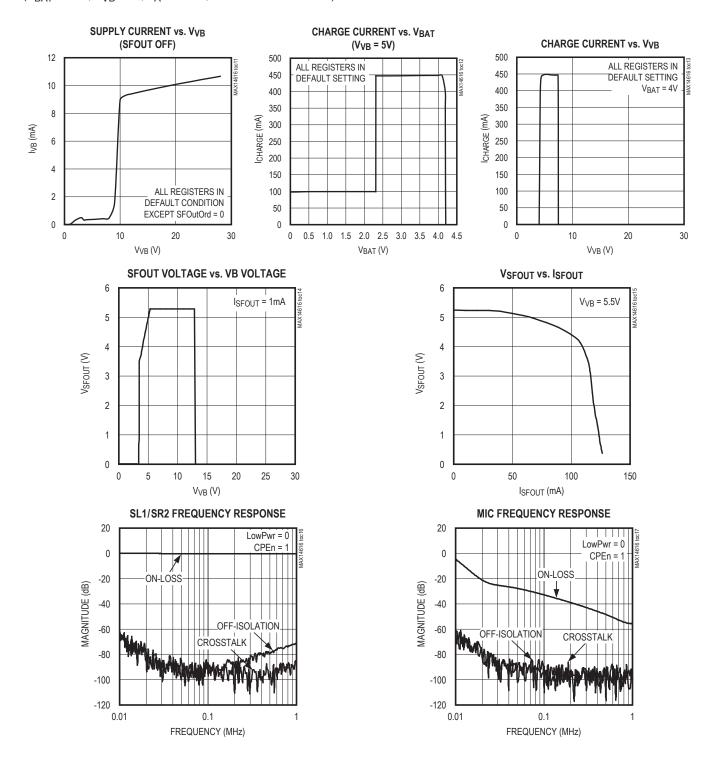

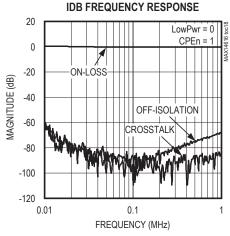

## **Typical Operating Characteristics**

$(V_{BAT} = 4.0V, V_{VB} = 0V, T_{A} = +25^{\circ}C, \text{ unless otherwise noted.})$

# **Bump Configuration**

## **Bump Description**

| BUMP | NAME            | FUNCTION                                                                                                                                           |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | V <sub>IO</sub> | I <sup>2</sup> C Reset Input. A falling edge on V <sub>IO</sub> causes the I <sup>2</sup> C registers to reset.                                    |

| A2   | ĪNT             | Active-Low Open-Drain Interrupt Output. Connect INT to an external pullup resistor.                                                                |

| А3   | DN1             | USB D- Input/Output                                                                                                                                |

| A4   | DP2             | USB D+ Input/Output                                                                                                                                |

| A5   | UID             | USB ID Input. Connect UID to ID on micro-USB connector. Maximum capacitance allowed from UID to ground is 1nF.                                     |

| B1   | MIC             | Microphone Output                                                                                                                                  |

| B2   | LED             | Open-Drain LED Driver. LED is controlled by the battery charger status (Table 4) or the BTLDSet bits in the CONTROL3 register.                     |

| В3   | JIG             | Factory-Mode Open-Drain Output. JIG is controlled by the internal state machine or manually controlled by the JIGSet register bits.                |

| B4   | CAP             | Internal LDO Bypass Output. Bypass CAP to GND with a 0.1µF (typ) ceramic capacitor for proper operation. Do not use CAP to drive an external load. |

| B5   | COMP2           | Common Input/Output 2. Connect COMP2 to D+ on the micro-USB connector.                                                                             |

## MAX14616/MAX14616A

# Micro-USB Interface Circuit Plus Intelligent Li+ Battery Chargers

# **Bump Description (continued)**

| BUMP   | NAME  | FUNCTION                                                                                                                                                                                                       |

|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1     | UR2   | UART Receiver Input/Output                                                                                                                                                                                     |

| C2     | UT1   | UART Transmitter Input/Output                                                                                                                                                                                  |

| C3     | IDB   | USB ID Bypass. IDB is used to sense ID of the micro-USB connector for USB OTG transceivers and the pass composite video.                                                                                       |

| C4     | SDA   | I <sup>2</sup> C Serial Data Input/Output. Connect SDA to external pullup resistor.                                                                                                                            |

| C5     | COMN1 | Common Input/Output 1. Connect COMN1 to D- on the micro-USB connector.                                                                                                                                         |

| D1, E1 | BAT   | Battery Charger Output and Chip-Power Input. Bypass BAT to GND with a 2.2µF (min) ceramic capacitor.                                                                                                           |

| D2     | SFOUT | Overvoltage-Protected LDO Output. Internal LDO is powered from VB. Bypass SFOUT to GND with a $1\mu F$ (min) ceramic capacitor.                                                                                |

| D3     | SCL   | I <sup>2</sup> C Serial Clock Input. Connect SCL to an external pullup resistor.                                                                                                                               |

| D4     | THM   | Battery Presence Detection                                                                                                                                                                                     |

| D5     | SR2   | Stereo Audio Input/Output 2                                                                                                                                                                                    |

| E2, E3 | VB    | USB VBUS Input. VB provides power for internal circuitry when $V_{BAT}$ is less than $V_{VB}$ . VB is also the input source for the battery charger. Bypass VB to GND with a $1\mu F$ (min) ceramic capacitor. |

| E4     | GND   | Ground                                                                                                                                                                                                         |

| E5     | SL1   | Stereo Audio Input/Output 1                                                                                                                                                                                    |

## **Functional Diagram/Typical Application Circuit**

## **Register Map**

| ADDRESS | NAME      | b7       | b6        | b5       | b4         | b3         | b2         | b1         | b0       |  |

|---------|-----------|----------|-----------|----------|------------|------------|------------|------------|----------|--|

| 0x00    | DEVICEID  |          |           | ChipID   | )          |            |            | DeviceID   |          |  |

| 0x01    | INT1      | 0        | 0         | 0        | 0          | ADC1KI     | ADCErrorl  | ADCLowl    | ADCI     |  |

| 0x02    | INT2      | 0        | 0         | VidRmI   | VBVoltI    | DXOVPI     | DCDTmrl    | ChgDetRunI | ChgTypl  |  |

| 0x03    | INT3      | 0        | 0         | BatDetl  | ChgEnbldl  | MBCCHGERRI | OVPI       | CGMBCI     | EOCI     |  |

| 0x04    | STATUS1   | ADC1K    | ADCError  | ADCLow   |            |            | ADC        |            |          |  |

| 0x05    | STATUS2   | VidRm    | VBVolt    | DXOVP    | DCDTmr     | ChgDetRun  |            | ChgTyp     |          |  |

| 0x06    | STATUS3   | 0        | Batt      | Det      | ChgEnbld   | MBCCHGERR  | OVP        | CGMBC      | EOC      |  |

| 0x07    | INTMASK1  | 0        | 0         | 0        | 0          | ADC1KM     | ADCErrorM  | ADCLowM    | ADCM     |  |

| 80x0    | INTMASK2  | 0        | 0         | VidRmM   | VBVoltM    | DXOVPM     | DCDTmrM    | ChgDetRunM | ChgTypM  |  |

| 0x09    | INTMASK3  | 0        | 0         | BatDetM  | ChgEnbldM  | MBCCHGERRM | OVPM       | CGMBCM     | EOCM     |  |

| 0x0A    | CDETCTRL1 | CDPDet   | 0         | DCDCpl   | CDDelay    | DCD2sCt    | DCDEn      | ChgTypMan  | ChgDetEn |  |

| 0x0B    | CDETCTRL2 | 0        | 0         | 0        | 0          | DxOVPEn    | JtaBatEn   | VidRmEn    | FrcChg   |  |

| 0x0C    | CONTROL1  | IDBEn    | MicEn     |          | COMP2Sw    | 1          |            | COMN1Sw    |          |  |

| 0x0D    | CONTROL2  | RCPS     | USBCpInt  | AccDet   | SFOutOrd   | SFOutAsrt  | CPEn       | ADCEn      | LowPwr   |  |

| 0x0E    | CONTROL3  | 0        | 0         | ADC      | DbSet      | BTLDS      | et         | JIGS       | Set      |  |

| 0x0F    | CHGCTRL1  | 0        |           | TCHW     |            | 0          | 1          | 0          | 0        |  |

| 0x10    | CHGCTRL2  | VCHGR_RC | MBCHOSTEN | 0        | 1          | 0          | 1          | 0          | 0        |  |

| 0x11    | CHGCTRL3  | 1        | 0         | 1        | 0          |            | MBCCVWRC   |            |          |  |

| 0x12    | CHGCTRL4  | 0        | 0         | 0        | MBCICHWRCL |            | MBCICHWRCH |            |          |  |

| 0x13    | CHGCTRL5  | 0        | 0         | 1        | 0          |            | EOC        | S          |          |  |

| 0x14    | CHGCTRL6  | 0        | 1         | AUTOSTOP | 1          | 0          | 0          | 0          | 1        |  |

| 0x15    | CHGCTRL7  | 0        | 0         | 0        | 0          | 0          | 0          | OTPCG      | HCVS     |  |

## **Detailed Register Map**

| FIELD NAME         | READ/WRITE | BITS  | DEFAULT | DESCRIPTION           |

|--------------------|------------|-------|---------|-----------------------|

| DEVICEID (0x00)    |            |       |         |                       |

| ChipID (MAX14616)  | Read Only  | [7:3] | 01110   | Chip Version          |

| ChipID (MAX14616A) | Read Only  | [7:3] | 10010   | Chip Version          |

| DeviceID           | Read Only  | [2:0] | 101     | Device Identification |

### INT1 (0x01) (All bits are cleared after a read)

Bits in this register are set when associated bits in the STATUS1 register change. INT is asserted when any bit in the INT1 register is set, unless masked in the INTMASK1 register.

## **Detailed Register Map (continued)**

| FIELD NAME | READ/WRITE | BITS  | DEFAULT   | DESCRIPTION                                                                  |

|------------|------------|-------|-----------|------------------------------------------------------------------------------|

| RFU        | Read Only  | [7:4] | 0000      | Reserved                                                                     |

| ADC1KI     | Read Only  | [3]   | (Note 10) | ADC 1K Detected or Removed Interrupt 0 = No change 1 = ADC1K bit has changed |

| ADCErrorl  | Read Only  | [2]   | (Note 10) | ADC Error Interrupt 0 = No change 1 = ADCError bit has changed               |

| ADCLowl    | Read Only  | [1]   | (Note 10) | ADC Low-Bit Change Interrupt 0 = No change 1 = ADCLow bit has changed        |

| ADCI       | Read Only  | [0]   | (Note 10) | ADC Change Interrupt 0 = No change 1 = ADC bits have changed                 |

#### INT2 (0x02) (All bits are cleared after a read)

Bits in this register are set when associated bits in the STATUS2 register change. INT is asserted when any bit in the INT2 register is set, unless masked in the INTMASK2 register.

| RFU        | Read Only | [7:6] | 00        | Reserved                                                                               |

|------------|-----------|-------|-----------|----------------------------------------------------------------------------------------|

| VidRml     | Read Only | [5]   | (Note 10) | Video Cable Removal Interrupt 0 = No change 1 = VidRm bit has changed                  |

| VBVoltI    | Read Only | [4]   | (Note 10) | VB Voltage Interrupt 0 = No change 1 = VBVolt bit has changed                          |

| DXOVPI     | Read Only | [3]   | (Note 10) | D+/D- OVP Interrupt 0 = No change 1 = DXOVP bit has changed                            |

| DCDTmrl    | Read Only | [2]   | (Note 10) | DCD Timer Interrupt 0 = No change 1 = DCDTmr bit has changed                           |

| ChgDetRunI | Read Only | [1]   | (Note 10) | Charger Detection Running Status Interrupt 0 = No change 1 = ChgDetRun bit has changed |

| ChgTypI    | Read Only | [0]   | (Note 10) | Charger Type Interrupt 0 = No change 1 = ChgTyp bits have changed                      |

### INT3 (0x03) (All bits are cleared after a read)

Bits in this register are set when associated bits in the STATUS3 register change.  $\overline{\text{INT}}$  is asserted when any bit in the INT3 register is set, unless masked in the INTMASK3 register.

# **Detailed Register Map (continued)**

| FIELD NAME                             | READ/WRITE        | BITS        | DEFAULT          | DESCRIPTION                                                                                                                                                                                                                                                                                                                 |

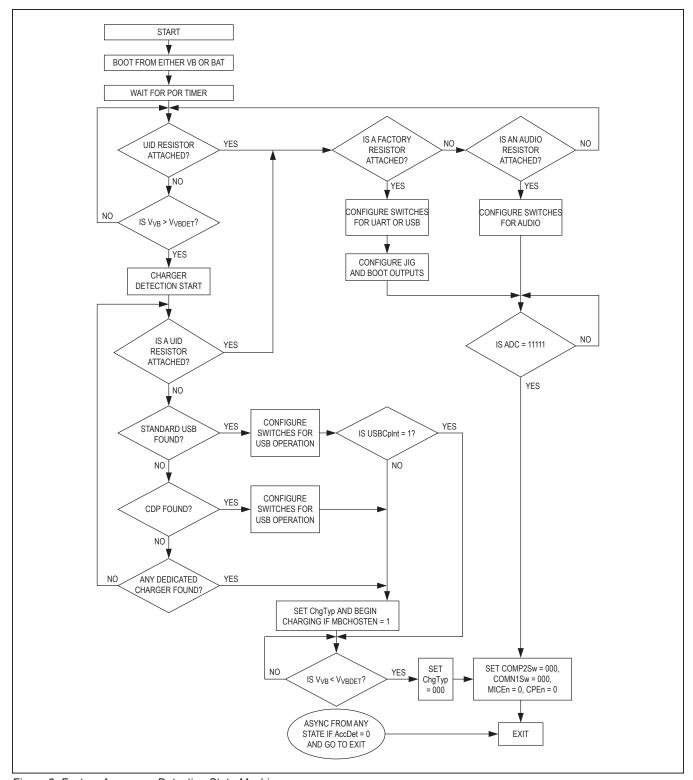

|----------------------------------------|-------------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|