## **High Efficiency Single Synchronous Buck PWM Controller**

#### **Purpose**

The RT8129A integrates a Constant-On-Time (COT) PWM controller and MOSFET driver so that the external circuit is easily designed and the components are reduced.

The controller provides the PWM signal which relies on the FB voltage comparing with internal reference voltage. The synchronous UGATE driver is turned on at the beginning of each cycle. After the internal one-shot timer expires, the UGATE driver will be turned off. The pulse width of this one-shot is determined by the controller's input voltage and the output voltage to keep the frequency fairly constant over the input voltage and output voltage range. Another one-shot sets a minimum off-time.

## **Table of Contents**

| Purpose                                      | 1  |

|----------------------------------------------|----|

| ntroduction                                  | 2  |

| Key Performance Summary Table                | 2  |

| Bench Test Setup Conditions                  | 3  |

| Schematic, Bill of Materials & Board Layout  | 4  |

| More Information                             | 11 |

| mportant Notice for Richtek Evaluation Board | 11 |

#### Introduction

#### General Product Information

The RT8129A is a high efficiency single phase synchronous buck controller with 5V/12V supply voltage. The RT8129A integrates a Constant-On-Time (COT) PWM controller and a MOSFET drivers with internal bootstrap diodes, which is specifically designed to improve converter efficiency at light load condition. At light load condition, it automatically operates in the diode emulation mode to reduce switching frequency and improve conversion efficiency. Other features include power good indication, enable/disable control and internal soft-start function. The RT8129A also provide protection functions including Over Voltage Protection (OVP), Under Voltage Protection (UVP), current limit and thermal shutdown.

This device uses lossless low-side MOSFET R<sub>DS(ON)</sub> current sense technique for current limit with adjustable threshold set by connecting a resistor between the LGATE/OCSET and GND.

With above functions, the RT8129A provides customers a cost-effective solution for high efficiency power conversion. The RT8129A is available in the WDFN-10L 3x3 package.

#### **Product Feature**

- Wide Input Voltage Range: 2.5V to 25V

- · High Light Load Efficiency

- Integrated High Driving Capability N-MOSFET Gate

- . Drivers and Embedded Switching Boot Diode

- Single IC Supply Voltage: 4.5V to 13.2V

- Power-Good Indicator

- Enable/Disable Control

- Internal Soft-Start

- Programmable Current Limit Threshold

- Under Voltage Protection

- Over Voltage Protection

- Thermal Shutdown

## **Key Performance Summary Table**

| Key Features                   | Evaluation Board Number : PCB047_V1 |  |  |  |

|--------------------------------|-------------------------------------|--|--|--|

| Input Voltage Range            | 2.5V to 25V                         |  |  |  |

| Max Output Current             | Programmable                        |  |  |  |

| Default Output Voltage         | 1.5V                                |  |  |  |

| Default Marking & Package Type | RT8129AGQW, WDFN-10L 3x3            |  |  |  |

| Operation Frequency            | 300kHz                              |  |  |  |

## **Bench Test Setup Conditions**

## Headers Description and Placement

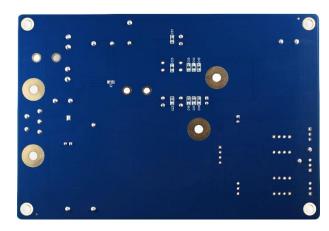

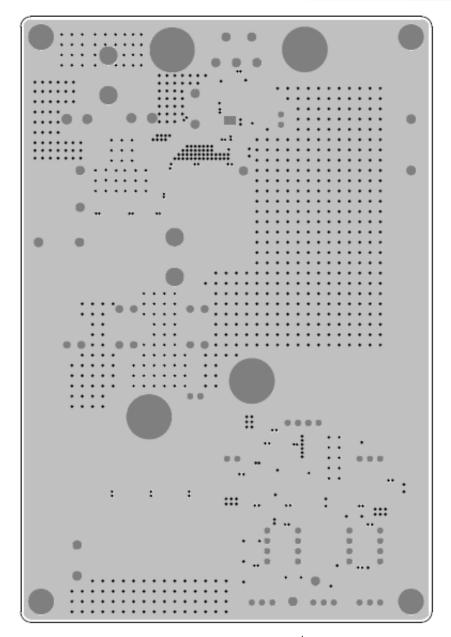

Top View

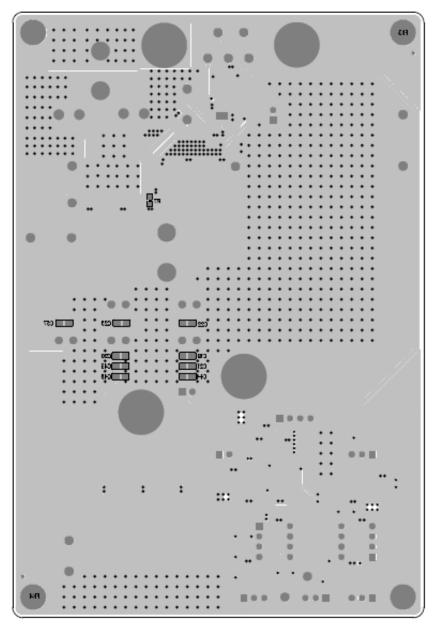

**Bottom View**

Please carefully inspect the EVB IC and external components, comparing them to the following Bill of Materials, to ensure that all components are installed and undamaged. If any components are missing or damaged during transportation, please contact the distributor or send e-mail to <a href="mailto:evb\_service@richtek.com">evb\_service@richtek.com</a>

#### **Test Points**

The EVB is provided with the test points and pin names listed in the table below.

| Test point/<br>Pin name | Signal                           | Comment (expected waveforms or voltage levels on test points)                                                                                     |

|-------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN                     | Input voltage                    | Power input. Support 2.5V to 25V Input Voltage. Must bypass with a suitable large ceramic capacitor at this pin.                                  |

| COMP                    | Enable test point                | High = Enable.                                                                                                                                    |

| GND                     | Ground                           | Ground.                                                                                                                                           |

| FB                      | Feedback voltage input           | The pin is used to set the output voltage of the converter to regulate to the desired voltage via a resistive divider. Feedback reference = 0.8V. |

| VCC                     | Supply voltage input             | 5V bias supply input. Connect a 4.7μF capacitor to ground                                                                                         |

| воот                    | Bootstrap supply test point      | Bootstrap supply for high-side gate driver. Connect a 0.1µF ceramic capacitor between the BOOT and PHASE pins.                                    |

| PHASE                   | Switch node test point           | Connect this pin to an external L-C filter.                                                                                                       |

| UG                      | High-side switch node test point | High-side MOSFET gate driver output. Connect this pin to the Gate of high-side MOSFET.                                                            |

| LG                      | Low-side switch node test point  | Low-side MOSFET gate driver output. Connect this pin to the Gate of low-side MOSFET.                                                              |

| PGOOD                   | Power good indication test point | The PGOOD voltage goes high to indicate the output voltage is in regulation.                                                                      |

#### Power-up & Measurement Procedure

- 1. Connect input power (2.5V < V<sub>IN</sub> < 25V and 4.5V < V<sub>CC</sub> < 13.2V).

- 2. Connect positive end and negative terminals of load to VOUT and GND test pins respectively.

- 3. EN pin is internal high, let JP1 open (JP1 short will turn off IC).

- 4. Verify the output voltage (VOUT approximately 1.5V, and FB approximately 0.8V) between VOUT to GND, and FB to GND.

- 5. Connect an external load up to 10A to the VOUT and GND terminals and verify the output voltage and current.

#### **Output Voltage Setting**

Set the output voltage with the resistive divider (R8, R10) between VOUT and GND with the midpoint connected to FB. The output is set by the following formula:

$$Vout = VFB x \left(1 + \frac{R8}{R10}\right)$$

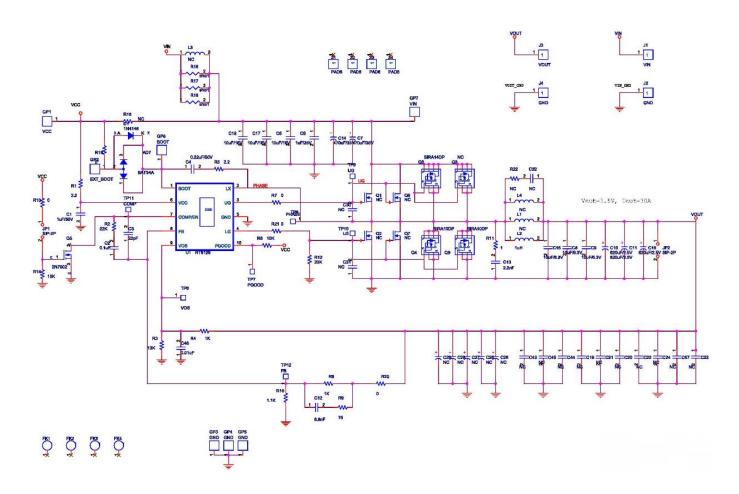

### Schematic, Bill of Materials & Board Layout

#### EVB Schematic Diagram

#### Bill of Materials

| Reference                                        | Qty | Part Number | Description | Package            | Manufacture |

|--------------------------------------------------|-----|-------------|-------------|--------------------|-------------|

| AD7                                              | 1   | BAT54A      | BAT54A      | SOT-23_123         |             |

| C1                                               | 1   |             | 1μF/50V     | C-0805             |             |

| C2                                               | 1   |             | 0.1µF       | C-0603             |             |

| C3                                               | 1   |             | 22pF        | C-0603             |             |

| C4                                               | 1   |             | 0.22µF/50V  | C-0603             |             |

| C5, C17, C18                                     | 3   |             | 10μF/16V    | C-1206_3-3         |             |

| C6                                               | 1   |             | 1μF/16V     | C-1206_3-3         |             |

| C7, C14                                          | 2   |             | 470µF/16V   | EC-2P/10           |             |

| C8, C9, C15                                      | 3   |             | 10µF/6.3V   | C-0805             |             |

| C10, C11, C16                                    | 3   |             | 820µF/2.5V  | EC-2P_8_1          |             |

| C12                                              | 1   |             | 6.8nF       | C-0603             |             |

| C13                                              | 1   |             | 2.2nF       | C-0603             |             |

| C19, C20, C21, C22, C23, C24, C43, C44, C45, C57 | 10  |             | NC          | C-0805             |             |

| C25, C26                                         | 2   |             | NC          | EC-2P_8_1          |             |

| C27, C28, C29                                    | 3   |             | NC          | c-2512             |             |

| C30, C31, C32                                    | 3   |             | NC          | C-0603             |             |

| C46                                              | 1   |             | 0.01µF      | C-0603             |             |

| D1                                               | 1   | 1N4148      | 1N4148      | D-0805_2-3368      |             |

| FK1, FK2, FK3, FK4                               | 4   |             | SIP-1P-TP   | FK_1               |             |

| GP1                                              | 1   |             | VCC         | SIP-1P-GP          |             |

| GP2                                              | 1   |             | EXT_BOOT    | SIP-1P-GP          |             |

| GP3, GP4, GP5                                    | 3   |             | GND         | SIP-1P-GP          |             |

| GP6                                              | 1   |             | воот        | SIP-1P-GP          |             |

| GP7                                              | 1   |             | VIN         | SIP-1P-GP          |             |

| JP1, JP2                                         | 2   |             | SIP-2P      | SIP-2P             |             |

| J1, J2, J3, J4                                   | 4   |             | NC          | sip-1p_p441d165    |             |

| J12, J13, J19, J20                               | 4   |             | NC          | SIP-4P-PW-2        |             |

| L1                                               | 1   |             | NC          | L-2P/387           |             |

| L2                                               | 1   |             | 1µH         | L-GSDRH127         |             |

| L3                                               | 1   |             | NC          | I-2p/9.82          |             |

| L4                                               | 1   |             | NC          | L-GMAR-V3R2-151311 |             |

| Q1, Q6                                           | 2   | IPD09N03LA  | IPD09N03LA  | DPAK_GDS           |             |

| Q2, Q7                                           | 2   | IPD06N03LA  | IPD06N03LA  | DPAK_GDS           |             |

| Q3, Q4, Q8, Q9                                   | 4   |             | NC          | Q-TDSON-8          |             |

| Q5                                               | 1   |             | 2N7002      | SOT-23_123         |             |

| R1, R5                                           | 2   |             | 2.2         | R-0603             |             |

| R2                                               | 1   |             | 22K         | R-0603             |             |

# RT8129AGQW Evaluation Board

| Reference              | Qty | Part Number | Description | Package      | Manufacture |

|------------------------|-----|-------------|-------------|--------------|-------------|

| R3                     | 1   |             | 13K         | R-0603       |             |

| R4, R8                 | 2   |             | 1K          | R-0603       |             |

| R6, R14                | 2   |             | 10K         | R-0603       |             |

| R7, R13, R19, R20, R21 | 5   |             | 0           | R-0603       |             |

| R9                     | 1   |             | 75          | R-0603       |             |

| R10                    | 1   |             | 1.1K        | R-0603       |             |

| R11                    | 1   |             | 1           | R-0603       |             |

| R12                    | 1   |             | 20K         | R-0603       |             |

| R15, R22               | 2   |             | NC          | R-0603       |             |

| R16, R17, R18          | 3   |             | short       | CP-0805C     |             |

| TP6                    | 1   |             | vos         | SIP-1P-TP    |             |

| TP7                    | 1   |             | PGOOD       | SIP-1P-TP    |             |

| TP8                    | 1   |             | PHASE       | SIP-1P-TP    |             |

| TP9                    | 1   |             | UG          | SIP-1P-TP    |             |

| TP10                   | 1   |             | LG          | SIP-1P-TP    |             |

| TP11                   | 1   |             | COMP        | SIP-1P-TP    |             |

| TP12                   | 1   |             | FB          | SIP-1P-TP    |             |

| U1                     | 1   | RT8129      | RT8129      | WDFN-10L 3x3 | RICHTEK     |

| Z1, Z2, Z3, Z4         | 4   |             | PAD6        | SIP-1P-M     |             |

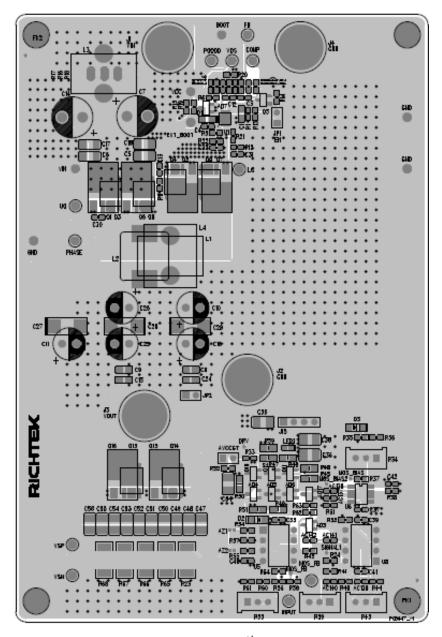

## PCB Layout

Top View (1st layer)

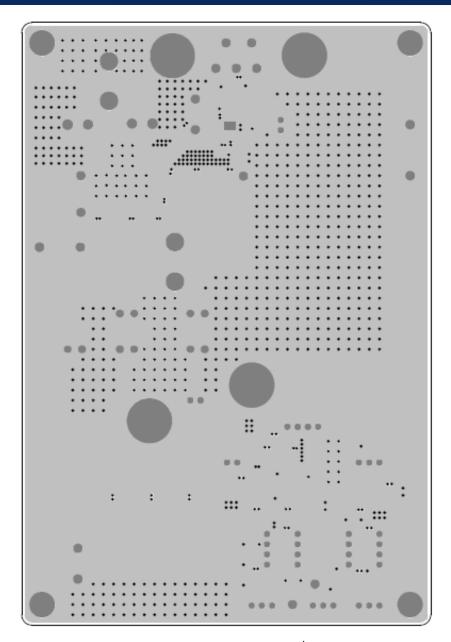

PCB Layout—Inner Side (2<sup>nd</sup> Layer)

PCB Layout—Inner Side (3<sup>rd</sup> Layer)

Bottom View (4<sup>th</sup> Layer)

#### More Information

For more information, please find the related datasheet or application notes from Richtek website <a href="http://www.richtek.com">http://www.richtek.com</a>.

## Important Notice for Richtek Evaluation Board

THIS DOCUMENT IS FOR REFERENCE ONLY, NOTHING CONTAINED IN THIS DOCUMENT SHALL BE CONSTRUED AS RICHTEK'S WARRANTY, EXPRESS OR IMPLIED, UNDER CONTRACT, TORT OR STATUTORY, WITH RESPECT TO THE PRESENTATION HEREIN. IN NO EVENT SHALL RICHTEK BE LIABLE TO BUYER OR USER FOR ANY AND ALL DAMAGES INCLUDING WITHOUT LIMITATION TO DIRECT, INDIRECT, SPECIAL, PUNITIVE OR CONSEQUENTIAL DAMAGES.