# TVS Diode Array for ESD Protection of 12V Data and Power Lines

#### PROTECTION PRODUCTS

#### Description

The SDC15 transient voltage suppressor (TVS) is designed to protect components which are connected to data and transmission lines from voltage surges caused by electrostatic discharge (ESD), electrical fast transients (EFT), and lightning.

TVS diodes are characterized by their high surge capability, low operating and clamping voltages, and fast response time. This makes them ideal for use as board level protection of sensitive semiconductor components. The dual-junction common-cathode design allows the user to protect one data or power line operating at ±12 volts. The low profile SOT23 package allows flexibility in the design of "crowded" circuit boards.

The SDC15 TVS will meet the surge requirements of IEC 61000-4-2 (Formerly IEC 801-2), Level 4, "Human Body Model" for air and contact discharge.

#### **Features**

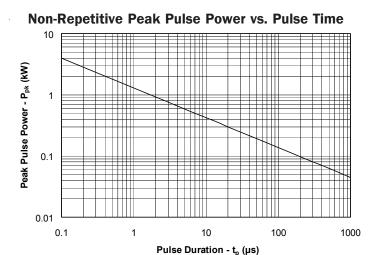

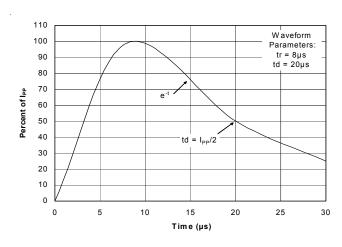

- 300 watts peak pulse power ( $t_p = 8/20\mu s$ )

- 40 watts peak pulse power ( $t_n = 10/1000 \mu s$ )

- ◆ Transient protection for data and power lines to IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 12A (1.2/50μs)

- Protects one bidirectional line

- Low clamping voltage

- Low leakage current

- High surge capability

- Solid-state silicon avalanche technology

#### Mechanical Characteristics

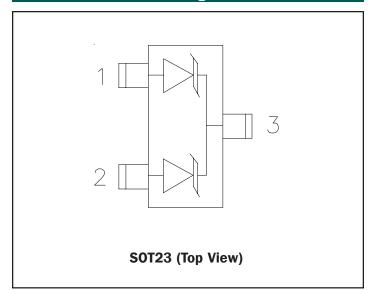

- ◆ JEDEC SOT23 package

- ◆ Molding compound flammability rating: UL 94V-0

- Marking : DC15

- Packaging: Tape and Reel per EIA 481

#### **Applications**

- ◆ RS-232 Data Lines

- Portable Electronics

- ◆ Industrial Controls

- Set-Top Box

- Servers, Notebook, and Desktop PC

- 12V DC Supply Protection

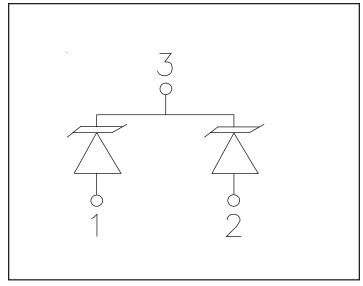

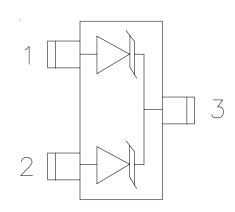

#### Circuit Diagram

# Schematic & PIN Configuration

# Absolute Maximum Rating

| Rating                                         | Symbol                | Value         | Units |

|------------------------------------------------|-----------------------|---------------|-------|

| Peak Pulse Power (tp = 8/20μs)                 | $P_{pk}$              | 300           | Watts |

| Peak Pulse Current (tp = 8/20μs)               | I <sub>PP</sub>       | 10            | А     |

| Non-Repetitive Peak Forward Current (tp=100μs) | I <sub>FSMAX</sub>    | 4             | А     |

| Thermal Resistance, Junction to Ambient        | $\theta_{	extsf{JA}}$ | 556           | °C/W  |

| Lead Soldering Temperature                     | T <sub>L</sub>        | 260 (10 sec.) | °C    |

| Operating Temperature                          | T <sub>J</sub>        | -55 to +125   | °C    |

| Storage Temperature                            | T <sub>STG</sub>      | -55 to +150   | °C    |

# **Electrical Characteristics**

| SDC15                          |                       |                                                                                |         |         |         |       |

|--------------------------------|-----------------------|--------------------------------------------------------------------------------|---------|---------|---------|-------|

| Parameter                      | Symbol                | Conditions                                                                     | Minimum | Typical | Maximum | Units |

| Reverse Stand-Off Voltage      | $V_{_{\mathrm{RWM}}}$ |                                                                                |         |         | 12.8    | V     |

| Reverse Breakdown Voltage      | $V_{BR}$              | I <sub>t</sub> = 1mA, 14.3 Between Pin 1 and 2 (each direction)                |         |         | 16.4    | V     |

| Reverse Leakage Current        | I <sub>R</sub>        | V <sub>RWM</sub> = 12.8V, T=25°C<br>Between Pin 1 and 2<br>(each direction)    |         | 100     | nA      |       |

| Forward Voltage                | V <sub>F</sub>        | I <sub>F</sub> = 100mA,<br>Pin 1 to 3 and<br>Pin 2 to 3                        |         |         | 1.3     | V     |

| Temperature Coefficient of VBR | αVBR                  |                                                                                |         |         | 12      | mV/°C |

| Clamping Voltage               | V <sub>c</sub>        | $I_{pp}$ = 1.9A,<br>tp = 10/10000µs<br>Between Pin 1 and 2<br>(each direction) |         | 21.2    | V       |       |

| Junction Capacitance           | C <sub>j</sub>        | V <sub>R</sub> = 0V, f = 1MHz<br>Pin 1 to 2                                    |         |         | 120     | pF    |

# Typical Characteristics

#### **Power Derating Curve** % of Rated Power or Ipp Ambient Temperature - T<sub>A</sub> (°C)

#### **Pulse Waveform**

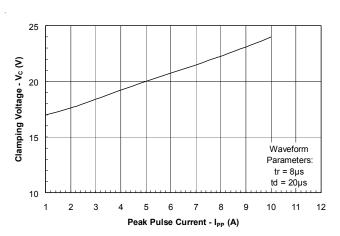

#### Clamping Voltage vs. Peak Pulse Current

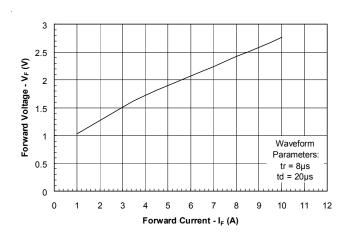

#### Forward Voltage vs. Forward Current

## **Applications Information**

#### **Device Connection for Protection of One Data Line**

The SDC15 is designed to protect one data or I/O line operating at  $\pm 12$  volts. Connection options are as follows:

- Common mode protection: Pin 1 is connected to the data line and pin 2 is connected to ground. For best results, this pin should be connected directly to a ground plane on the board. The path length should be kept as short as possible to minimize parasitic inductance. Pin 3 is not connected.

- Differential protection: Pin 1 is connected to one line and pin 2 is connected to the second line. Pin 3 is not connected.

# Circuit Board Layout Recommendations for Suppression of ESD.

Good circuit board layout is critical for the suppression of fast rise-time transients such as ESD. The following guidelines are recommended:

- Place the SDC15 near the input terminals or connectors to restrict transient coupling.

- Minimize the path length between the SDC15 and the protected line.

- Minimize all conductive loops including power and ground loops.

- The ESD transient return path to ground should be kept as short as possible.

- Never run critical signals near board edges.

- Use ground planes whenever possible.

#### **Matte Tin Lead Finish**

Matte tin has become the industry standard lead-free replacement for SnPb lead finishes. A matte tin finish is composed of 100% tin solder with large grains. Since the solder volume on the leads is small compared to the solder paste volume that is placed on the land pattern of the PCB, the reflow profile will be determined by the requirements of the solder paste. Therefore, these devices are compatible with both lead-free and SnPb assembly techniques. In addition, unlike other lead-free compositions, matte tin does not have any added alloys that can cause degradation of the solder joint.

#### **Device Schematic and Pin Configuration**

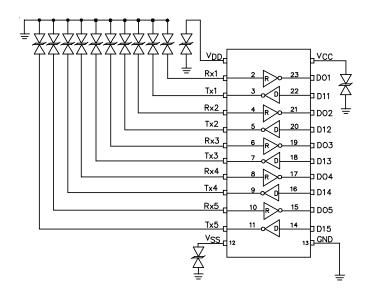

#### **RS-232 Transceiver Protection Example**

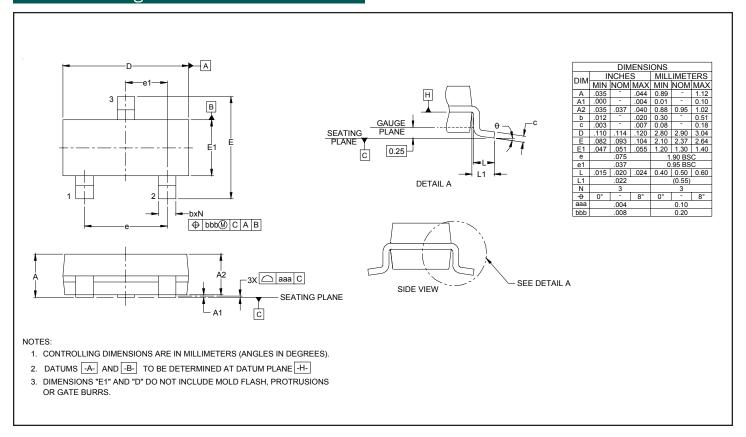

# Outline Drawing - SOT23

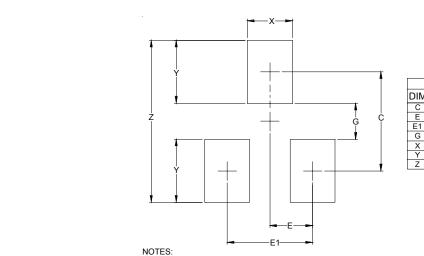

# Land Pattern - SOT23

| DIMENSIONS |        |             |  |

|------------|--------|-------------|--|

| DIM        | INCHES | MILLIMETERS |  |

| С          | (.087) | (2.20)      |  |

| E          | .037   | 0.95        |  |

| E1         | .075   | 1.90        |  |

| G          | .031   | 0.80        |  |

| Х          | .039   | 1.00        |  |

| Υ          | .055   | 1.40        |  |

| Z          | .141   | 3.60        |  |

THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

Note 1 : Grid placement courtyard is 8 elements (4mm x 4mm) in accordance with the international grid detailed in IEC Publication 97.

# Ordering Information

| Part Number | Lead<br>Finish | Qty per<br>Reel | Reel Size |

|-------------|----------------|-----------------|-----------|

| SDC15.TC    | SnPb           | 3,000           | 7 Inch    |

| SDC15.TCT   | Pb Free        | 3,000           | 7 Inch    |

# **Contact Information**

Semtech Corporation Protection Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804