## 27 to 930MHz Transceiver Evaluation Board Description

#### Features

| Single chip solution with only a few external | FSK/ASK mode selection                         |

|-----------------------------------------------|------------------------------------------------|

| components                                    | RSSI output for signal strength indication and |

| Stand-alone fixed-frequency user mode         | ASK reception                                  |

| Programmable multi-channel user mode          | ASK detection normal or with peak detector     |

| Low current consumption in active mode and    | Switchable LNA gain for improved dynamic       |

| very low standby current                      | range                                          |

| PLL-stabilized RF VCO (LO) with internal      | Automatic PA turn-on after PLL lock            |

| varactor diode                                | ASK modulation achieved by PA on/off keying    |

| Lock detect output in programmable            | 3wire bus serial control interface             |

| user mode                                     | EVB comes with a cable to connect to a PC's    |

|                                               |                                                |

LPT port

- On-chip AFC for extended input frequency acceptance range

- ☐ FSK for digital data or FM for analog signal reception

- ☐ EVB programming software is available on Melexis web site

### **Ordering Information**

#### Part No.

EVB7122-315-FSK-C EVB7122-433-FSK-C EVB7122-868-FSK-C EVB7122-915-FSK-C

# Application Examples

- General bi-directional half duplex digital data RF signaling or analog signal communication

- ☐ Tire Pressure Monitoring Systems (TPMS)

- □ Remote Keyless Entry (RKE)

- □ Low-power telemetry systems

- □ Alarm and security systems

- □ Wireless access control

- □ Garage door openers

- Networking solutions

- ☐ Active RFID tags

- □ Remote controls

- Home and building automation

## **Evaluation Board Example**

# General Description

The TH7122 is a single chip FSK/FM/ASK transceiver IC. It is designed to operate in low-power multi-channel programmable or single-channel stand-alone, half-duplex data transmission systems. It can be used for applications in automotive, industrial-scientific-medical (ISM), short range devices (SRD) or similar applications operating in the frequency range of 300 MHz to 930 MHz. In programmable user mode, the transceiver can operate down to 27 MHz by employing an external VCO varactor diode.

<sup>\*</sup> EVB7122-XXX-YYY-C with XXX = Reception frequency (315, 433.92, 868.3 or 915MHz) and YYY = Modulation (FSK or ASK).

<sup>\*\*</sup> EVB default population is FSK, ASK modifications according to paragraph 4.2 and 4.3.

<sup>\*\*\*</sup> The evaluation board is supplied with a SMA connector.

### **Document Content**

| 1 | The            | ory of Operation                                                             | 3  |

|---|----------------|------------------------------------------------------------------------------|----|

|   | 1.1            | General                                                                      | 3  |

|   | 1.2            | Technical Data Overview                                                      | 3  |

|   | 1.3            | Note on ASK Operation                                                        | 3  |

|   | 1.4            | Block Diagram                                                                | 4  |

|   | 1.5            | User Mode Features                                                           | 4  |

| 2 | Des            | cription of User Modes                                                       | £  |

|   | 2.1            | · Stand-alone User Mode Operation                                            |    |

|   | 2.1.1          | Frequency Selection                                                          |    |

|   | 2.1.2          | ,                                                                            |    |

|   | 2.1.3          | <b>71</b>                                                                    |    |

|   | 2.1.4          |                                                                              |    |

|   | 2.2            | Programmable User Mode Operation                                             |    |

|   | 2.2.1          | Serial Control Interface Description                                         | 6  |

| 3 | Reg            | ister Description                                                            | 7  |

|   | 3.1            | Register Overview                                                            | 8  |

|   | 3.1.1          | Default Register Settings for FS0, FS1                                       | 8  |

|   | 3.1.2          | A – word                                                                     |    |

|   | 3.1.3<br>3.1.4 |                                                                              |    |

|   | 3.1.4<br>3.1.5 |                                                                              |    |

| 4 |                | lication Circuits                                                            |    |

|   | 4.1            | FSK Application Circuit Programmable User Mode (internal AFC option)         |    |

|   | 4.1.1          | Board Component Values for FSK Reception                                     |    |

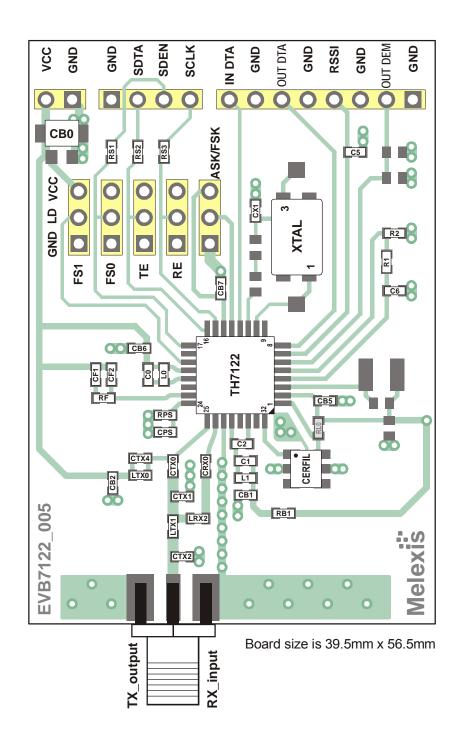

|   | 4.1.2          | Component Arrangement Top Side for FSK Reception                             |    |

|   | 4.2            | ASK Application Circuit Programmable User Mode (normal data slicer option)   | 16 |

|   | 4.2.1          | Board Component Values for ASK (normal data slicer option)                   | 17 |

|   | 4.2.2          | Component Arrangement Top Side for ASK Reception (normal data slicer option) | 18 |

|   | 4.3            | ASK Application Circuit with Peak Detector Option                            | 19 |

|   | 4.3.1          | Board Component Values for ASK (peak detector option)                        |    |

|   | 4.3.2          | Component Arrangement Top Side for ASK Reception (peak detector option)      | 21 |

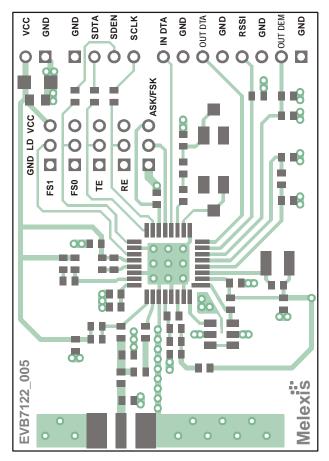

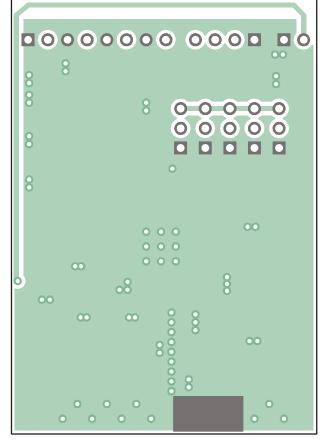

| 5 | Eva            | uation Board Layouts                                                         | 22 |

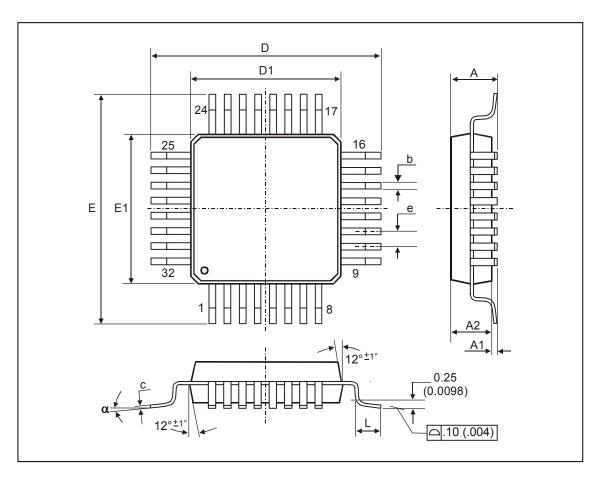

| 6 | Pac            | kage Description                                                             | 23 |

|   | 6.1            | Soldering Information                                                        | 23 |

| 7 | Disa           | laimer                                                                       | 24 |

## 27 to 930MHz Transceiver Evaluation Board Description

### 1 Theory of Operation

#### 1.1 General

The main building block of the transceiver is a programmable PLL frequency synthesizer that is based on an integer-N topology. The PLL is used for generating the carrier frequency during transmission and for generating the LO signal during reception. The carrier frequency can be FSK-modulated by pulling the crystal and ASK-modulated by on/off keying of the power amplifier. The receiver is based on the principle of a single conversion superhet. Therefore the VCO frequency has to be changed between transmit and receive mode. In receive mode, the preferred LO injection type is low-side injection.

The TH7122 transceiver IC consists of the following building blocks:

- Low-noise amplifier (LNA) for high-sensitivity RF signal reception with switchable gain

- Mixer (MIX) for RF-to-IF down-conversion

- IF amplifier (IFA) to amplify and limit the IF signal and for RSSI generation

- Phase-coincidence demodulator with external ceramic discriminator (FSK Demodulator)

- Operational amplifier (OA1), connected to demodulator output

- Operational amplifier (OA2), for geral use

- Peak detector (PKDET) for ASK detection

- Control logic with 3wire bus serial control interface (SCI)

- Reference oscillator (RO) with external crystal

- Reference divider (R counter)

- Programmable divider (N/A counter)

- Phase-frequency detector (PFD)

- Charge pump (CP)

- Voltage controlled oscillator (VCO) with internal varactor

- Power amplifier (PA) with adjustable output power

#### 1.2 Technical Data Overview

| Frequency range: 300 MHz to 930 MHz in           | Sensitivity: -107 dBm at ASK with 180 kHz        |

|--------------------------------------------------|--------------------------------------------------|

| programmable user mode                           | IF filter BW                                     |

| Extended frequency range with external VCO       | Max. data rate with crystal pulling: 20 kbps NRZ |

| varactor diode: 27 MHz to 930 MHz                | Max. data rate with direct VCO modulation:       |

| 315 MHz, 433 MHz, 868 MHz or 915 MHz fixed-      | 115 kbps NRZ                                     |

| frequency settings in stand-alone mode           | Max. input level: -10 dBm at FSK                 |

| Power supply range: 2.2 V to 5.5 V               | and -20 dBm at ASK                               |

| Temperature range: -40 °C to +85 °C              | Input frequency acceptance: ± 10 to ± 150 kHz    |

| Standby current: 50 nA                           | (depending on FSK deviation)                     |

| Operating current in receive: 6.5 mA (low gain)  | FM/FSK deviation range: ±2.5 to ±80 kHz          |

| Operating current in transmit: 12 mA (at -2 dBm) | Analog modulation frequency: max. 10 kHz         |

| Adjustable RF power range: -20 dBm to            | Crystal reference frequency: 3 MHz to 12 MHz     |

| +10dBm                                           | External reference frequency: 1 MHz to 16 MHz    |

| Sensitivity: -105 dBm at FSK with 180 kHz        | ,                                                |

### 1.3 Note on ASK Operation

IF filter BW

Optimum ASK performance can be achieved by using an 8-MHz crystal for operation at 315 MHz, 434 MHz and 915 MHz. For details please refer to the software settings shown in sections 4.2 and 4.3. FSK operation is the preferred choice for applications in the European 868MHz band.

For more detailed information, please refer to the latest TH7122 data sheet revision

### 1.4 Block Diagram

Fig. 1: TH7122 block diagram

### 1.5 User Mode Features

The transceiver can operate in two different user modes. It can be used either as a 3wire-bus-controlled programmable or as a stand-alone fixed-frequency device. After power up, the transceiver is set to Stand-alone User Mode (SUM). In this mode, pins FS0/SDEN and FS1/LD must be connected to  $V_{\text{EE}}$  or  $V_{\text{CC}}$  in order to set the desired frequency of operation. There are 4 pre-defined frequency settings: 315MHz, 433.92MHz, 868.3MHz and 915MHz. The logic level at pin FS0/SDEN must not be changed after power up in order to remain in fixed-frequency mode.

After the first logic level change at pin FS0/SDEN, the transceiver enters into Programmable User Mode (PUM). In this mode, the user can set any PLL frequency or mode of operation by the SCI. In SUM pins FS0/SDEN and FS1/LD are used to set the desired frequency, while in PUM pin FS0/SDEN is part of the 3-wire serial control interface (SCI) and pin FS1/LD is the look detector output signal of the PLL synthesizer.

A mode control logic allows several operating modes. In addition to standby, transmit and receive mode, two idle modes can be selected to run either the reference oscillator only or the whole PLL synthesizer. The PLL settings for the PLL idle mode are taken over from the last operating mode which can be either receive or transmit mode.

The different operating modes can be set in SUM and PUM as well. In SUM the user can program the transceiver via control pins RE/SCLK and TE/SDTA. In PUM the register bits OPMODE are used to select the modes of operation while pins RE/SCLK and TE/SDTA are part of the SCI.

### 2 Description of User Modes

### 2.1 Stand-alone User Mode Operation

After power up the transceiver is set to stand-alone user mode. In this mode, pins FS0/SDEN and FS1/LD must be connected to  $V_{\text{EE}}$  or  $V_{\text{CC}}$  to set the desired frequency of operation. The logic level at pin FS0/SDEN must not be changed after power up in order to remain in stand-alone user mode. The default settings of the control word bits in stand-alone user mode are described in the frequency selection table. Detailed information about the default settings can be found in the tables of section 5.

### 2.1.1 Frequency Selection

| Channel frequency               | 433.92 MHz | 868.3 MHz  | 315 MHz    | 915 MHz    |

|---------------------------------|------------|------------|------------|------------|

| FS0/SDEN                        | 1          | 0          | 1          | 0          |

| FS1/LD                          | 0          | 0          | 1          | 1          |

|                                 |            |            |            |            |

| Reference oscillator frequency  |            | 7.150      | 5 MHz      |            |

| R counter ratio in RX mode (RR) | 32         | 16         | 18         | 32         |

| PFD frequency in RX mode        | 223.45 kHz | 446.91 kHz | 397.25 kHz | 223.45 kHz |

| N counter ratio in RX mode (NR) | 1894       | 1919       | 766        | 4047       |

| VCO frequency in RX mode        | 423.22 MHz | 857.60 MHz | 304.30 MHz | 904.30 MHz |

| RX frequency                    | 433.92 MHz | 868.30 MHz | 315.00 MHz | 915.00 MHz |

| R counter ratio in TX mode (RT) | 32         | 16         | 18         | 32         |

| PFD frequency in TX mode        | 223.45 kHz | 446.91 kHz | 397.25 kHz | 223.45 kHz |

| N counter ratio in TX mode (NT) | 1942       | 1943       | 793        | 4095       |

| VCO frequency in TX mode        | 433.92 MHz | 868.30 MHz | 315.00 MHz | 915.00 MHz |

| TX frequency                    | 433.92 MHz | 868.30 MHz | 315.00 MHz | 915.00 MHz |

| IF in RX mode                   | 10.7 MHz   | 10.7 MHz   | 10.7 MHz   | 10.7 MHz   |

In stand-alone user mode, the transceiver can be set to Standby, Receive, Transmit or Idle mode (only PLL synthesizer active) via control pins RE/SCLK and TE/SDTA. The modulation scheme and the LNA gain are set by pins ASK/FSK and GAIN\_LNA, respectively.

### 2.1.2 Operation Mode

| Operation mode | Standby | Receive | Transmit | ldle |

|----------------|---------|---------|----------|------|

| RE/SCLK        | 0       | 1       | 0        | 1    |

| TE/SDTA        | 0       | 0       | 1        | 1    |

Note: Pins with internal pull-down

### 2.1.3 Modulation Type

| Modulation type | ASK | FSK |

|-----------------|-----|-----|

| ASK / FSK       | 0   | 1   |

#### 2.1.4 LNA Gain Mode

| LNA gain | high | low |

|----------|------|-----|

| GAIN_LNA | 0    | 1   |

### 2.2 Programmable User Mode Operation

The transceiver can also be used in programmable user mode. After power-up the first logic change at pin FS0/SDEN enters into this mode. Now full programmability can be achieved via the Serial Control Interface (SCI).

### 2.2.1 Serial Control Interface Description

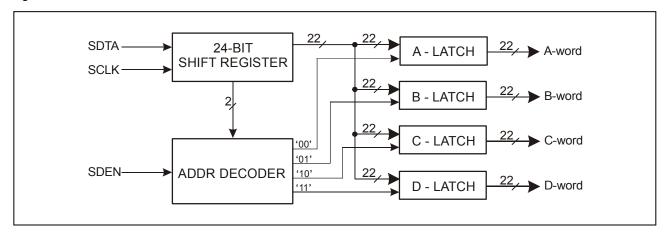

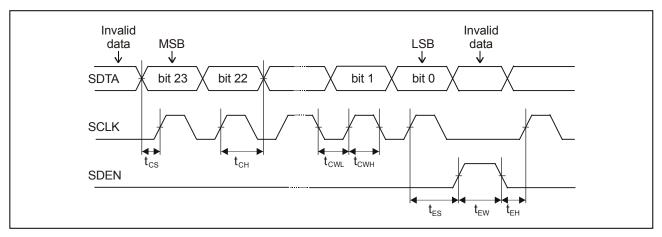

A 3-wire (SCLK, SDTA, SDEN) Serial Control Interface (SCI) is used to program the transceiver in programmable user mode. At each rising edge of the SCLK signal, the logic value on the SDTA pin is written into a 24-bit shift register. The data stored in the shift register are loaded into one of the 4 appropriate latches on the rising edge of SDEN. The control words are 24 bits lengths: 2 address bits and 22 data bits. The first two bits (bit 23 and 22) are latch address bits. As additional leading bits are ignored, only the least significant 24 bits are serial-clocked into the shift register. The first incoming bit is the most significant bit (MSB). To program the transceiver in multi-channel application, four 24-bit words may be sent: A-word, B-word, C-word and D-word. If individual bits within a word have to be changed, then it is sufficient to program only the appropriate 24-bit word. The serial data input timing and the structure of the control words are illustrated in Fig. 2 and 3.

Fig. 2: SCI Block Diagram

## 27 to 930MHz Transceiver Evaluation Board Description

Due to the static CMOS design, the SCI consumes virtually no current and it can be programmed in active as well as in standby mode.

If the transceiver is set from standby mode to any of the active modes (idle, receive, transmit), the SCI settings remain the same as previously set in one of the active modes, unless new settings are done on the SCI while entering into an active mode.

Fig. 3: Serial Data Input Timing

### 3 Register Description

As shown in the previous section there are four control words which stipulate the operation of the whole chip. In Stand-alone User Mode SUM the intrinsic default values with respect to the applied levels at pins FS0 and FS1 lay down the configuration of the transceiver. In Programmable User Mode (PUM) the register settings can be changed via 3-wire interface SCI. The default settings which vary with the desired operating frequency depend on the voltage levels at the frequency selection pins FS0 and FS1 before entering the PUM. Table 5.1.1 shows the default register settings of different frequency selections. It should be noted that the channel frequency listed below will be achieved with a crystal frequency of 7.1505 MHz. The following table depicts an overview of the register configuration of the TH7122.

### 3.1 Register Overview

| wo | RD |         |          |        |         |          |                                                 |                                                          |                |          |         | DA             | TA    |      |              |       |       |       |       |       |       |    |        |         |

|----|----|---------|----------|--------|---------|----------|-------------------------------------------------|----------------------------------------------------------|----------------|----------|---------|----------------|-------|------|--------------|-------|-------|-------|-------|-------|-------|----|--------|---------|

| MS | В  | _       |          |        |         |          |                                                 |                                                          |                |          |         |                |       |      |              |       |       |       |       |       |       |    | LSB    |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16                                              | 15                                                       | 14             | 13       | 12      | 11             | 10    | 9    | 8            | 7     | 6     | 5     | 4     | 3     | 2     |    | 1 0    | Bit No. |

| 0  | 0  | 0       | 0        | 0      | 0       | 0        | 1                                               | 1 1 1 0 0 Depends on FS0/FS1 voltage level after power u |                |          | wer up  | default        |       |      |              |       |       |       |       |       |       |    |        |         |

| A  | •  | IDLE    | DATAPOL  | MODSEL | CPCUR   | LOCKMODE | PACTRL                                          | TXPOWER                                                  | [1:0]          | Set to 1 | LNAGAIN | OPMODE         | [1:0] |      |              |       |       | RR    | [0:6] |       |       |    |        |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16                                              | 15                                                       | 14             | 13       | 12      | 11             | 10    | 9    | 8            | 7     | 6     | 5     | 4     | 3     | 2     |    | 1 0    | Bit No. |

| 0  | 1  | 0       | 1        | 1      | 1       | 0        | 0                                               | 1                                                        | 1              | 1        | 0       | 1              | 0     | Dep  | ends         | on FS | 30/FS | 1 vol | tage  | level | after | ро | wer up | default |

| E  | 8  | PKDET   | Set to 1 | DELPLL | LNAHYST | AFC      | OA2                                             |                                                          | ROMAX<br>[2:0] | ,        |         | ROMIN<br>[2:0] |       |      |              |       |       | RT    | [0:6] |       |       |    |        |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16                                              | 15                                                       | 14             | 13       | 12      | 11             | 10    | 9    | 8            | 7     | 6     | 5     | 4     | 3     | 2     |    | 1 0    | Bit No. |

| 1  | 0  | 0       | 0        |        |         |          |                                                 |                                                          | Dep            | ends     | on F    | S0/F           | S1 vo | tage | level        | after | powe  | r up  |       |       |       |    |        | default |

| (  |    | LNACTRL | PFDPOL   | VCOCUR | [1:0]   | BAND     |                                                 |                                                          |                |          |         |                |       |      | NR<br>[16:0] | •     |       |       |       |       |       |    |        |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16                                              | 15                                                       | 14             | 13       | 12      | 11             | 10    | 9    | 8            | 7     | 6     | 5     | 4     | 3     | 2     |    | 1 0    | Bit No. |

| 1  | 1  | 0       | 0        | 1      | 0       | 0        | Depends on FS0/FS1 voltage level after power up |                                                          |                |          |         | default        |       |      |              |       |       |       |       |       |       |    |        |         |

|    |    | MODCTRL | MLGT     | [1:0]  | ERTM    | [1:0]    |                                                 | NT [16:0]                                                |                |          |         |                |       |      |              |       |       |       |       |       |       |    |        |         |

### 3.1.1 Default Register Settings for FS0, FS1

| FS1 | FS0 | Channel frequency | BAND | VCOCUR<br>[1:0] | RR<br>[9:0] | NR<br>[ 16 :0 ] | RT<br>[9:0] | NT<br>[16:0] |

|-----|-----|-------------------|------|-----------------|-------------|-----------------|-------------|--------------|

| 0   | 0   | 868.30 MHz        | 1    | 11              | 16d         | 1919d           | 16d         | 1943d        |

| 0   | 1   | 433.92 MHz        | 0    | 01              | 32d         | 1894d           | 32d         | 1942d        |

| 1   | 0   | 915.00 MHz        | 1    | 11              | 32d         | 4047d           | 32d         | 4095d        |

| 1   | 1   | 315.00 MHz        | 0    | 00              | 18d         | 766d            | 18d         | 793d         |

**Note:** d – decimal code

A detailed description of the registers function and their configuration can be found in the following sections.

# 27 to 930MHz Transceiver Evaluation Board Description

### $3.1.2 \quad A - word$

| Name     | Bits    |          | Description                                                                                         |                  |  |  |

|----------|---------|----------|-----------------------------------------------------------------------------------------------------|------------------|--|--|

| RR       | [9:0]   |          | Reference divider ratio in RX operation mode                                                        |                  |  |  |

| IXIX     | [9.0]   | 4d       | 1023d                                                                                               |                  |  |  |

|          |         |          | Operation mode                                                                                      |                  |  |  |

| OPMODE   | [44.40] | 00       | Standby mode                                                                                        | #default         |  |  |

| OFWIODE  | [11:10] | 01<br>10 | Receive mode Transmit mode                                                                          |                  |  |  |

|          |         | 11       | Idle mode                                                                                           |                  |  |  |

|          |         |          | LNA gain                                                                                            |                  |  |  |

| LNAGAIN  | [12]    | 0        | low LNA gain                                                                                        |                  |  |  |

|          | ' '     | 1        | high LNA gain                                                                                       | #default         |  |  |

|          | 5407    |          | This selection is valid if bit LNACTR (bit 21 in C-word) is set to internal LNA gain                | control.         |  |  |

| not used | [13]    |          | set to '1' for correct function                                                                     |                  |  |  |

|          |         |          | Output power steps                                                                                  |                  |  |  |

| TXPOWER  | [15:14] | 00<br>01 | P1<br>P2                                                                                            |                  |  |  |

|          | []      | 10       | P3                                                                                                  |                  |  |  |

|          |         | 11       | P4                                                                                                  | #default         |  |  |

|          |         |          | Set the PA-on condition                                                                             |                  |  |  |

| PACTRL   | [16]    | 0        |                                                                                                     |                  |  |  |

|          |         | 1        | PA is always on in TX mode                                                                          | #default         |  |  |

|          |         | 0        | Set the PLL locked state observation mode                                                           | #default         |  |  |

|          | F4 77   | U        | before lock only  Locked state condition will be ascertained only one time afterwards the LD signal |                  |  |  |

| LOCKMODE | [17]    |          | high state.                                                                                         |                  |  |  |

|          |         | 1        | before and after lock                                                                               |                  |  |  |

|          |         |          | locked state will be observed permanently                                                           |                  |  |  |

| 000110   | F4.03   |          | Charge Pump output current                                                                          |                  |  |  |

| CPCUR    | [18]    | 0<br>1   | 260 μA<br>1300 μA                                                                                   | #default         |  |  |

|          |         | •        | Modulation mode                                                                                     |                  |  |  |

|          |         | 0        | ASK                                                                                                 | #default         |  |  |

| MODSEL   | [19]    | 1        | FSK                                                                                                 | <i>n</i> doladic |  |  |

|          |         |          | This selection is valid if bit MODCTRL (bit 21 in D-word) is set to internal control.               | modulation       |  |  |

|          |         |          | Input data polarity                                                                                 |                  |  |  |

|          |         | 0        | normal                                                                                              | #default         |  |  |

| DTAPOL   | [20]    |          | '0' for space at ASK or f <sub>min</sub> at FSK, '1' for mark at ASK or f <sub>max</sub> at FSK     |                  |  |  |

|          |         | 1        | inverse                                                                                             |                  |  |  |

|          |         |          | '1' for space at ASK or f <sub>min</sub> at FSK, '0' for mark at ASK or f <sub>max</sub> at FSK     |                  |  |  |

|          |         |          | Active blocks in IDLE mode                                                                          |                  |  |  |

| IDLESEL  | [21]    | 0        | only RO active                                                                                      | #default         |  |  |

|          |         | 1        | whole PLL active                                                                                    |                  |  |  |

# 27 to 930MHz Transceiver Evaluation Board Description

### 3.1.3 B – word

| Name     | Bits    |                                                      |                                                                           |                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                 |

|----------|---------|------------------------------------------------------|---------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| RT       | [9:0]   |                                                      |                                                                           | Referenc        | e divider ratio in TX operation mode                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                 |

| K I      | [9.0]   | 4d                                                   | 1023d                                                                     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|          |         |                                                      | Set the                                                                   | desired st      | eady state current of the reference oscilla                                                                                                                                                                                                                                                                                                                                                                                               | ator                                                                                                                            |

| ROMIN    | [12:10] | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 0 μA<br>75 μA<br>150 μA<br>225 μA<br>300 μA<br>375 μA<br>450 μA<br>525 μA | #default        | The control circuitry regulates the current of the between the values ROMAX and ROMIN. As the signal the amplitude on pin RO is used. If the sufficient to achieve an amplitude of about 400m current of the reference oscillator core will be Otherwise the current will be permanently regROMAX and ROMIN. If ROMIN and ROMAX regulation of the oscillator current occurs. Please block description of the reference oscillator in para | regulation input<br>ROMIN value is<br>V on pin RO the<br>set to ROMIN.<br>gulated between<br>C are equal no<br>se also note the |

|          |         |                                                      | S                                                                         | Set the star    | t-up current of the reference oscillator                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

| ROMAX    | [15:13] | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 0 μA<br>75 μA<br>150 μA<br>225 μA<br>300 μA<br>375 μA<br>450 μA<br>525 μA | #default        | Set the start-up current of the reference oscillar also note the description of the ROMIN registed description of the reference oscillator which can be                                                                                                                                                                                                                                                                                   | r and the block                                                                                                                 |

|          |         |                                                      |                                                                           |                 | OA2 operation                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                 |

| OA2      | [16]    | 0<br>1                                               | disabled enabled                                                          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           | #default                                                                                                                        |

|          |         |                                                      | OA2 can be e                                                              | nabled in FS    | K receive mode. OA2 is disabled in ASK mode receive                                                                                                                                                                                                                                                                                                                                                                                       | eive.                                                                                                                           |

| AFC      | [17]    | 0                                                    | disabled enabled                                                          |                 | Internal AFC feature                                                                                                                                                                                                                                                                                                                                                                                                                      | #default                                                                                                                        |

|          |         |                                                      |                                                                           | Н               | ysteresis on pin GAIN LNA                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |

| LNAHYST  | [18]    | 0                                                    | disabled enabled                                                          |                 | 40 mV ( $V_{0\rightarrow 1} = 1.56V$ , $V_{1\rightarrow 0} = 1.22V$ )                                                                                                                                                                                                                                                                                                                                                                     | #default                                                                                                                        |

|          |         |                                                      |                                                                           |                 | Delayed start of the PLL                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

| DELPLL   | [19]    | 0                                                    | undelayed                                                                 | start           | PLL starts at the reference oscillator start-up                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|          | [ []    | 1                                                    | starts after                                                              |                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                         | #default                                                                                                                        |

|          |         |                                                      | PLL starts after<br>of the reference                                      |                 | -cycles before entering an active mode to ensure re                                                                                                                                                                                                                                                                                                                                                                                       | eliable oscillation                                                                                                             |

| not used | [20]    |                                                      |                                                                           | S               | set to '1' for correct function                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|          |         |                                                      |                                                                           |                 | RSSI Peak Detector                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                 |

|          |         | 0                                                    | disabled                                                                  |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           | #default                                                                                                                        |

| PKDET    | [21]    |                                                      | The RSSI out                                                              | put signal dire | ectly feeds the data slicer setup by means of OA1.                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                 |

|          |         | 1                                                    | enabled                                                                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|          |         |                                                      | In ASK receive                                                            | e mode the F    | RSSI Peak Detector output is multiplexed to pin INT                                                                                                                                                                                                                                                                                                                                                                                       | 2/PDO.                                                                                                                          |

# 27 to 930MHz Transceiver Evaluation Board Description

### 3.1.4 C – word

| Name    | Bits    | Description                                                                                                             |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------|

| NR      | [16:0]  | Feedback divider ratio in RX operation mode                                                                             |

| INIX    | [10.0]  | 64d 131071d                                                                                                             |

|         |         | Set the desired frequency range                                                                                         |

| BAND    | [17]    | <ul> <li>recommended at f<sub>RF</sub> &lt; 500 MHz</li> <li>recommended at f<sub>RF</sub> &gt; 500MHz</li> </ul>       |

|         |         | Some tail current sources are linked to this bit in order to save current for low frequent operations.                  |

|         |         | VCO active current                                                                                                      |

| VCOCUR  | [19:18] | 00 low current (300 μA) 01 standard current (500 μA) 10 high1 current (700 μA) 11 high2 current (900 μA)                |

|         |         | Phase Detector polarity                                                                                                 |

| PFDPOL  | [20]    | negative #default  vco output FREQUENCY neg vco input voltage                                                           |

|         |         | LNA gain control mode                                                                                                   |

|         |         | 0 external LNA gain control #default                                                                                    |

| LNACTRL | [21]    | LNA gain will be set via pin GAIN_LNA.                                                                                  |

|         |         | 1 internal LNA gain control                                                                                             |

|         |         | LNA gain will be set via bit LNAGAIN (bit 12 in A-word). Nevertheless pin GAIN_LNA mube connected to either VCC or VEE. |

# 27 to 930MHz Transceiver Evaluation Board Description

### 3.1.5 *D* – word

| Name    | Bits    |                      | Description                                                                                                                                       |                             |                                                                                                                      |    |  |  |  |

|---------|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| NT      | [16:0]  |                      | i                                                                                                                                                 | eedback di                  | vider ratio in TX operation mode                                                                                     |    |  |  |  |

| 141     | [10.0]  | 64d                  | 131071d                                                                                                                                           |                             |                                                                                                                      |    |  |  |  |

|         |         |                      | Set the unlock condition of the PLL                                                                                                               |                             |                                                                                                                      |    |  |  |  |

| ERTM    | [18:17] | 00<br>01<br>10<br>11 | O1 4 clocks 10 Set the maximum allowed number of referer (1/f <sub>RO</sub> ) during the phase detector output signals (UP can be in-consecutive. |                             |                                                                                                                      |    |  |  |  |

|         | [20:19] |                      | Set the lock condition of the PLL                                                                                                                 |                             |                                                                                                                      |    |  |  |  |

| LDTM    |         | 00<br>01<br>10<br>11 | 4 clocks<br>16 clocks<br>64 clocks<br>256 clocks                                                                                                  | #default                    | Set the minimum number of consecutive edges of pha detector output cycles, without appearance of any unlo condition. |    |  |  |  |

|         |         |                      |                                                                                                                                                   | Set m                       | ode of modulation control:                                                                                           |    |  |  |  |

|         | [21]    | 0                    | external mo                                                                                                                                       | external modulation control |                                                                                                                      |    |  |  |  |

| MODCTRL |         |                      | Modulation will                                                                                                                                   | be set via pin A            | ASK/FSK.                                                                                                             |    |  |  |  |

|         |         | 1                    | internal modulation control                                                                                                                       |                             |                                                                                                                      |    |  |  |  |

|         |         |                      | Modulation will connected to eit                                                                                                                  |                             | MODSEL (bit 19 in A-word). Nevertheless pin ASK/FSK must EE.                                                         | be |  |  |  |

# 4 Application Circuits

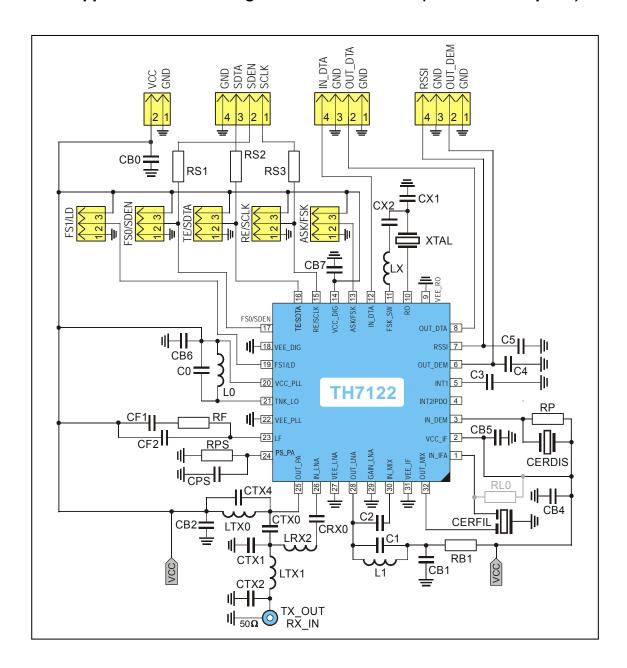

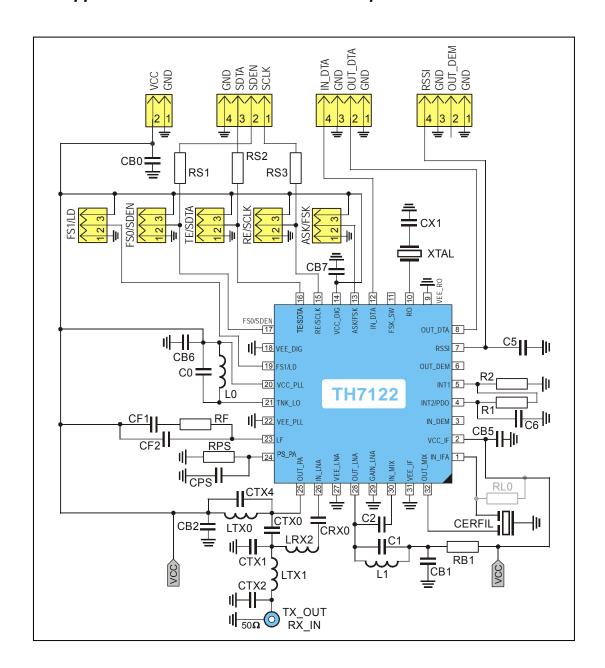

### 4.1 FSK Application Circuit Programmable User Mode (internal AFC option)

# 27 to 930MHz Transceiver Evaluation Board Description

## 4.1.1 Board Component Values for FSK Reception

| Part   | Size               | Value @<br>315 MHz | Value @<br>433.92<br>MHz | Value @<br>868.3 MHz                       | Value @<br>915 MHz                                                                 | Tol. | Description                                                                      |

|--------|--------------------|--------------------|--------------------------|--------------------------------------------|------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------|

| C0     | 0603               | 1.2 pF             | 1.5 pF                   | 1.8 pF                                     | 0.82 pF                                                                            | ±5%  | VCO tank capacitor                                                               |

| C1     | 0603               | 3.9 pF             | 5.6 pF                   | 2.2 pF                                     | 1.8 pF                                                                             | ±5%  | LNA output tank capacitor                                                        |

| C2     | 0603               | 1.5 pF             | 1.5 pF                   | 1.5 pF                                     | 1.5 pF                                                                             | ±5%  | MIX input matching capacitor                                                     |

| C3     | 0603               | 10 nF              | 10 nF                    | 10 nF                                      | 10 nF                                                                              | ±10% | data slicer capacitor                                                            |

| C4     | 0603               | 330 pF             | 330 pF                   | 330 pF                                     | 330 pF                                                                             | ±5%  | demodulator output low-pass capacitor, depending on data rate                    |

| C5     | 0603               | 1.5 nF             | 1.5 nF                   | 1.5 nF                                     | 1.5 nF                                                                             | ±10% | RSSI output low pass capacitor                                                   |

| CB0    | 1210               | 10 µF              | 10 μF                    | 10 μF                                      | 10 µF                                                                              | ±20% | de-coupling capacitor                                                            |

| CB1    | 0603               | 10 nF              | 10 nF                    | 10 nF                                      | 10 nF                                                                              | ±10% | de-coupling capacitor                                                            |

| CB2    | 0603               | 330 pF             | 330 pF                   | 330 pF                                     | 330 pF                                                                             | ±10% | de-coupling capacitor                                                            |

| CB4    | 0603               | 10 nF              | 10 nF                    | 10 nF                                      | 10 nF                                                                              | ±10% | de-coupling capacitor                                                            |

| CB5    | 0603               | 100 nF             | 100 nF                   | 100 nF                                     | 100 nF                                                                             | ±10% | de-coupling capacitor                                                            |

| CB6    | 0603               | 100 pF             | 100 pF                   | 100 pF                                     | 100 pF                                                                             | ±10% | de-coupling capacitor                                                            |

| CB7    | 0603               | 100 nF             | 100 nF                   | 100 nF                                     | 100 nF                                                                             | ±10% | de-coupling capacitor                                                            |

| CF1    | 0603               | 1 nF               | 1 nF                     | 1 nF                                       | 1 nF                                                                               | ±10% | loop filter capacitor                                                            |

| CF2    | 0603               | 68 pF              | 120 pF                   | 150 pF                                     | 82 pF                                                                              | ±5%  | loop filter capacitor                                                            |

| CPS    | 0603               | 10 nF              | 10 nF                    | 10 nF                                      | 10 nF                                                                              | ±10% | power-select capacitor                                                           |

| CX1    | 0603               | 8.2 pF             | 10 pF                    | 12 pF                                      | 12 pF                                                                              | ±5%  | RO capacitor for FSK ( $\Delta f = \pm 20 \text{ kHz}$ )                         |

| CX2    | 0603               | 150 pF             | 56 pF                    | 18 pF                                      | 15 pF                                                                              | ±5%  | RO capacitor for FSK ( $\Delta f = \pm 20 \text{ kHz}$ )                         |

| CRX0   | 0603               | 100 pF             | 100 pF                   | 100 pF                                     | 100 pF                                                                             | ±5%  | RX coupling capacitor                                                            |

| CTX0   | 0603               | 10 pF              | 10 pF                    | 10 pF                                      | 10 pF                                                                              | ±5%  | TX coupling capacitor                                                            |

| CTX1   | 0603               | 10 pF              | 6.8 pF                   | 5.6 pF                                     | 4.7 pF                                                                             | ±5%  | TX impedance matching capacitor                                                  |

| CTX2   | 0603               | 10 pF              | 6.8 pF                   | 3.9 pF                                     | 3.9 pF                                                                             | ±5%  | TX impedance matching capacitor                                                  |

| CTX4   | 0603               | 12 pF              | 4.7 pF                   | 2.2 pF                                     | 1.8 pF                                                                             | ±5%  | TX impedance matching capacitor                                                  |

| RB1    | 0603               | 100 Ω              | 100 Ω                    | 100 Ω                                      | 100 Ω                                                                              | ±5%  | protection resistor                                                              |

| RF     | 0603               | 47 kΩ              | 47 kΩ                    | 33 kΩ                                      | 33 kΩ                                                                              | ±5%  | loop filter resistor                                                             |

| RP     | 0603               | 3.3 kΩ             | 3.3 kΩ                   | 3.3 kΩ                                     | 3.3 kΩ                                                                             | ±5%  | CERDIS loading resistor                                                          |

| RL0    | 0603               | 390 Ω              | 390 Ω                    | 390 Ω                                      | 390 Ω                                                                              | ±5%  | CERFIL loading, optionally                                                       |

| RPS    | 0603               | 22 kΩ              | 33 kΩ                    | 47 kΩ                                      | 47 kΩ                                                                              | ±5%  | power-select resistor                                                            |

| RS1RS3 | 0603               | 10 kΩ              | 10 kΩ                    | 10 kΩ                                      | 10 kΩ                                                                              | ±5%  | protection resistor                                                              |

| LO     | 0603               | 47 nH              | 22 nH                    | 3.9 nH                                     | 3.9 nH                                                                             | ±5%  | VCO tank inductor from Würth-Elektronik (WE-KI series) or equivalent part        |

| L1     | 0603               | 33 nH              | 15 nH                    | 4.7 nH                                     | 4.7 nH                                                                             | ±5%  | LNA output tank inductor from Würth-Elektronik (WE-KI series) or equivalent part |

| LRX2   | 0603               | 82 nH              | 56 nH                    | 15 nH                                      | 15 nH                                                                              | ±5%  | impedance matching inductor                                                      |

| LTX0   | 0603               | 15 nH              | 15 nH                    | 3.9 nH                                     | 3.9 nH                                                                             | ±5%  | from Würth-Elektronik (WE-KI series)                                             |

| LTX1   | 0603               | 33 nH              | 33 nH                    | 10 nH                                      | 10 nH                                                                              | ±5%  | or equivalent part                                                               |

| LX     | 0603               | 0 Ω                | 0 Ω                      | 10 nH                                      | 10 nH                                                                              | ±5%  | RO inductor                                                                      |

| XTAL   | HC49<br>SMD<br>7x5 |                    | ±20pp                    |                                            | fundamental-mode crystal from:<br>Telcona/Hong Kong X'tals<br>C5L7150500D10F3EHK02 |      |                                                                                  |

| CERFIL | SMD<br>3.45x3.1    |                    | SI                       | FECF10M7HA00<br>B <sub>3dB</sub> = 180 kHz |                                                                                    |      | ceramic filter from Murata,<br>or equivalent part                                |

| CERDIS | SMD<br>4.5x2       |                    | CD                       | SCB10M7GA136                               | 3                                                                                  |      | ceramic Discriminator from Murata,<br>or equivalent part                         |

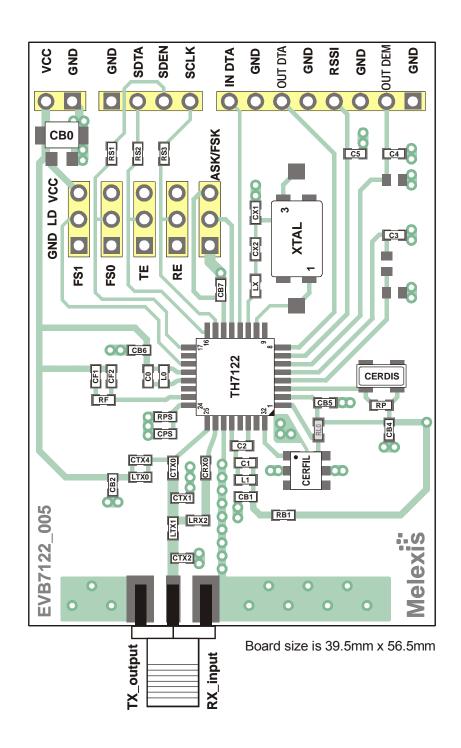

### 4.1.2 Component Arrangement Top Side for FSK Reception

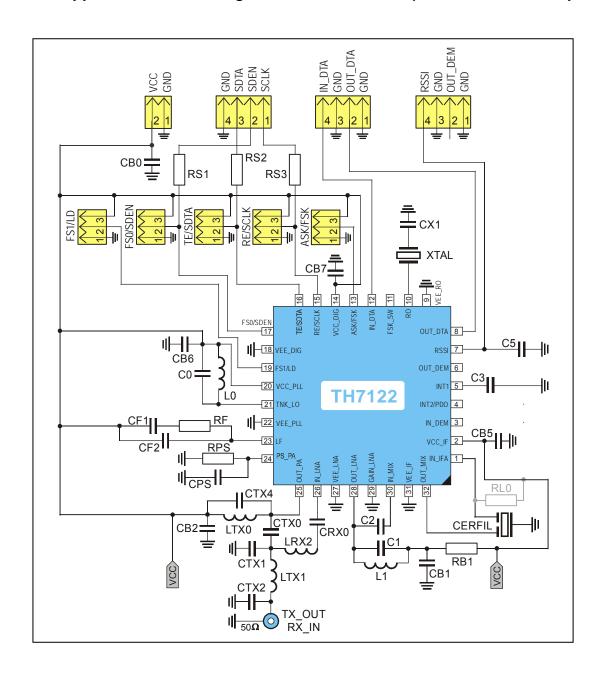

### 4.2 ASK Application Circuit Programmable User Mode (normal data slicer option)

### Software Settings for ASK

| Channel    |    | f <sub>RO</sub> = 8.0 | 000MHz | СРО | CUR   | VCOCUR |       |       |

|------------|----|-----------------------|--------|-----|-------|--------|-------|-------|

| frequency  | RR | NR                    | RT     | NT  | RX    | TX     | RX    | TX    |

| 315.00 MHz | 80 | 3043                  | 8      | 315 | 260µA | 1300µA | 300µA | 900µA |

| 434.00 MHz | 80 | 4233                  | 8      | 434 | 260µA | 1300µA | 300µA | 900µA |

| 915.00 MHz | 80 | 9043                  | 8      | 915 | 260µA | 1300µA | 300µA | 900µA |

# 27 to 930MHz Transceiver Evaluation Board Description

### 4.2.1 Board Component Values for ASK (normal data slicer option)

| Part   | Size               | Value @<br>315 MHz | Value @<br>434 MHz                 | Value @<br>915 MHz | Tol. | Description                                                                        |

|--------|--------------------|--------------------|------------------------------------|--------------------|------|------------------------------------------------------------------------------------|

| C0     | 0603               | 1.5 pF             | 1.8 pF                             | 1 pF               | ±5%  | VCO tank capacitor                                                                 |

| C1     | 0603               | 3.9 pF             | 5.6 pF                             | 1.8 pF             | ±5%  | LNA output tank capacitor                                                          |

| C2     | 0603               | 1.5 pF             | 1.0 pF                             | 1.5 pF             | ±5%  | MIX input matching capacitor                                                       |

| C3     | 0603               | 10 nF              | 10 nF                              | 10 nF              | ±10% | data slicer capacitor                                                              |

| C5     | 0603               | 1.5 nF             | 1.5 nF                             | 1.5 nF             | ±10% | RSSI output low pass capacitor                                                     |

| CB0    | 1210               | 10 μF              | 10 μF                              | 10 μF              | ±20% | de-coupling capacitor                                                              |

| CB1    | 0603               | 10 nF              | 10 nF                              | 10 nF              | ±10% | de-coupling capacitor                                                              |

| CB2    | 0603               | 330 pF             | 330 pF                             | 330 pF             | ±10% | de-coupling capacitor                                                              |

| CB5    | 0603               | 100 nF             | 100 nF                             | 100 nF             | ±10% | de-coupling capacitor                                                              |

| CB6    | 0603               | 100 pF             | 100 pF                             | 100 pF             | ±10% | de-coupling capacitor                                                              |

| CB7    | 0603               | 100 nF             | 100 nF                             | 100 nF             | ±10% | de-coupling capacitor                                                              |

| CF1    | 0603               | 100 pF             | 100 pF                             | 100 pF             | ±10% | loop filter capacitor                                                              |

| CF2    | 0603               | 39 pF              | 39 pF                              | 39 pF              | ±5%  | loop filter capacitor                                                              |

| CPS    | 0603               | 1 nF               | 1 nF                               | 1 nF               | ±10% | power-select capacitor, depending ondata rate                                      |

| CX1    | 0603               | 18 pF              | 18 pF                              | 18 pF              | ±5%  | RO capacitor                                                                       |

| CRX0   | 0603               | 100 pF             | 100 pF                             | 10 pF              | ±5%  | RX coupling capacitor                                                              |

| CTX0   | 0603               | 10 pF              | 10 pF                              | 10 pF              | ±5%  | TX coupling capacitor                                                              |

| CTX1   | 0603               | 10 pF              | 6.8 pF                             | 4.7 pF             | ±5%  | TX impedance matching capacitor                                                    |

| CTX2   | 0603               | 10 pF              | 6.8 pF                             | 3.9 pF             | ±5%  | TX impedance matching capacitor                                                    |

| CTX4   | 0603               | 12 pF              | 4.7 pF                             | 1.8 pF             | ±5%  | TX impedance matching capacitor                                                    |

| RB1    | 0603               | 100 Ω              | 100 Ω                              | 100 Ω              | ±5%  | protection resistor                                                                |

| RF     | 0603               | 33 kΩ              | 33 kΩ                              | 33 kΩ              | ±5%  | loop filter resistor                                                               |

| RP     | 0603               | 3.3 ΚΩ             | 3.3 ΚΩ                             | 3.3 ΚΩ             | ±5%  | CERDIS loading resistor                                                            |

| RL0    | 0603               | 390 Ω              | 390 Ω                              | 390 Ω              | ±5%  | CERFIL loading, optionally                                                         |

| RPS    | 0603               | 18 kΩ              | 33 kΩ                              | 43 kΩ              | ±5%  | power-select resistor                                                              |

| RS1RS3 | 0603               | 10 kΩ              | 10 kΩ                              | 10 kΩ              | ±5%  | protection resistor                                                                |

| LO     | 0603               | 47 nH              | 27 nH                              | 3.9 nH             | ±5%  | VCO tank inductor from Würth-Elektronik (WE-KI series) or equivalent part          |

| L1     | 0603               | 33 nH              | 15 nH                              | 4.7 nH             | ±5%  | LNA output tank inductor from Würth-Elektronik (WE-KI series) or equivalent part   |

| LRX2   | 0603               | 82 nH              | 56 nH                              | 15 nH              | ±5%  | impedance matching inductor                                                        |

| LTX0   | 0603               | 15 nH              | 15 nH                              | 3.9 nH             | ±5%  | from Würth-Elektronik (WE-KI series)                                               |

| LTX1   | 0603               | 33 nH              | 33 nH                              | 10 nH              | ±5%  | or equivalent part                                                                 |

| XTAL   | HC49<br>SMD<br>7x5 |                    | 8.0000 N<br>±20ppm cal., ±20       |                    |      | fundamental-mode crystal from:<br>Telcona/Hong Kong X'tals<br>C5L8000000D10F3EHK01 |

| CERFIL | SMD<br>3.45x3.1    |                    | SFECF10M<br>B <sub>3dB</sub> = 180 |                    |      | ceramic filter from Murata, or equivalent part                                     |

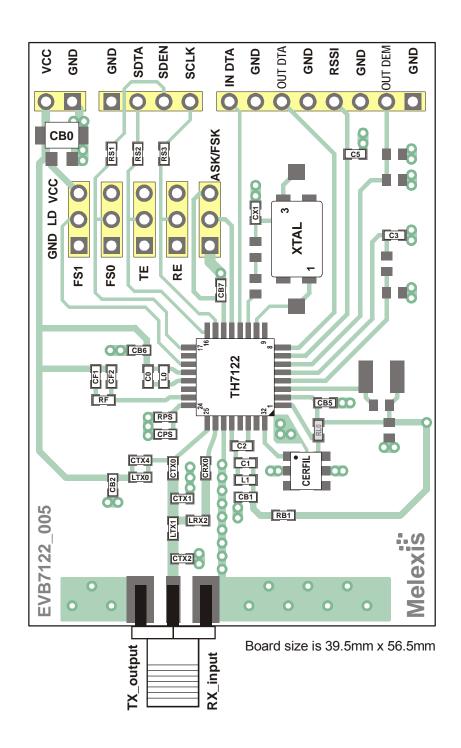

### 4.2.2 Component Arrangement Top Side for ASK Reception (normal data slicer option)

### 4.3 ASK Application Circuit with Peak Detector Option

### Software Settings for ASK

| Channel frequency |    | f <sub>RO</sub> = 8.0 | 000MHz | СРО | CUR   | VCOCUR |        |       |

|-------------------|----|-----------------------|--------|-----|-------|--------|--------|-------|

|                   | RR | NR                    | RT     | NT  | RX    | TX     | RX     | TX    |

| 315.00 MHz        | 80 | 3043                  | 8      | 315 | 260µA | 1300µA | 300 µA | 900µA |

| 434.00 MHz        | 80 | 4233                  | 8      | 434 | 260µA | 1300µA | 300 µA | 900µA |

| 915.00 MHz        | 80 | 9043                  | 8      | 915 | 260µA | 1300µA | 300 µA | 900µA |

# 27 to 930MHz Transceiver Evaluation Board Description

### 4.3.1 Board Component Values for ASK (peak detector option)

| Part   | Size               | Value @<br>315 MHz | Value @<br>434 MHz                 | Value @<br>915 MHz                                                                 | Tol. | Description                                                                      |

|--------|--------------------|--------------------|------------------------------------|------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------|

| C0     | 0603               | 1.8 pF             | 2.2 pF                             | 1 pF                                                                               | ±5%  | VCO tank capacitor                                                               |

| C1     | 0603               | 3.9 pF             | 5.6 pF                             | 1.8 pF                                                                             | ±5%  | LNA output tank capacitor                                                        |

| C2     | 0603               | 1.5 pF             | 1.0 pF                             | 1.5 pF                                                                             | ±5%  | MIX input matching capacitor                                                     |

| C5     | 0603               | 1.5 nF             | 1.5 nF                             | 1.5 nF                                                                             | ±10% | RSSI output low pass capacitor                                                   |

| C6     | 0603               | 100 nF             | 100 nF                             | 100 nF                                                                             | ±10% | PKDET capacitor                                                                  |

| CB0    | 1210               | 10 μF              | 10 μF                              | 10 μF                                                                              | ±20% | de-coupling capacitor                                                            |