# Application Notes

# **BG2G – Universal Gate Drive Prototype Board**

Figure 1: BG2G Direct Mounted on NX Package

### **Description:**

The BG2G is a two-channel gate drive circuit board that utilizes a VLA567-01R dual Powerex hybrid gate driver with built-in DC-to-DC converters. The BG2G was designed to provide efficient switching of all Powerex dual modules rated up to 1000A/1200V. The two onboard 0.1" two-pin output connectors make it easy to tie in twisted pair wires for attachment to any module package. In the case of the dual NX series isolated gate bipolar transistor (IGBT), the gate and emitter pins can be soldered directly into this board, as depicted in Figure 1 above. The BG2G hybrid gate driver includes high-speed opto-couplers for control signal isolation, an isolated fault feedback signal, desaturation detection circuitry to protect the IGBT from short circuit conditions, and built-in DC-to-DC converters to provide fully isolated control power for each driving channel.

### Features:

- ±8A peak output current

- 2500VRMS isolation for control power and signals

- Standard AMP MTA .100" input and output connectors

- Single 15VDC power supply required for operation

- Wide output voltage swing +16.8V/-8.5V

- Compact PCB Size 101mm x 70mm

### **Applications:**

Gate driver for Powerex dual IGBT modules.

- Direct solder connections available for NX modules.

- Output connectors available for other module types.

### Benefits:

- Reduced prototyping and design time

- Reduced prototyping and deisgn cost

- Reduced risk to high value IGBTs via built in protection circuits

- Simplified gate drive solution, just provide the 5V logic signal and a single 15VDC power supply.

Ordering Information: BG2G-8015 is a kit with a bare BG2G board, and one VLA567-01R gate drive IC.

## Circuit Explanation:

The BG2G is a basic two-channel gate drive board designed around the recommended application circuit for the Powerex VLA567-01R core IGBT gate driver with built-in isolated DC-to-DC converters.

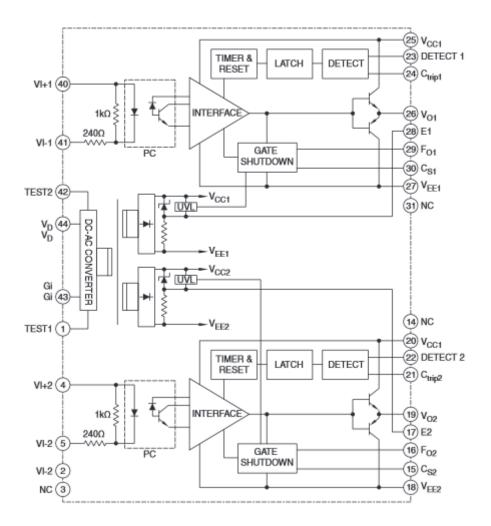

A functional block diagram of the VLA567-01R is shown for reference in Figure 2. This gate drive is optimized for use with Powerex 600V and 1200V dual IGBT modules rated up to 1000A. The driver uses a high speed open collector type opto-coupler to provide 2500VRMS isolation of control signals. The output stage is designed to provide high current gate drive with the appropriate on and off-state bias voltages for large IGBT modules. The gate driver includes a desaturation detection circuit to provide protection against short circuit conditions. For additional detailed information on the characteristics and operation of the gate driver please refer to the <a href="VLA567-01R datasheet">VLA567-01R datasheet</a>.

Figure 2: VLA567-01R Functional Block Diagram

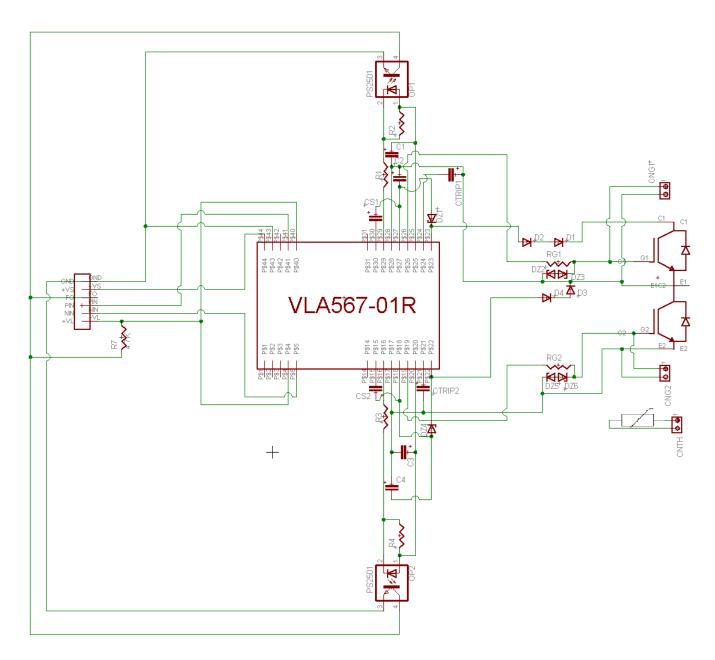

A complete schematic and component selection guide for the BG2G is shown in Figure 3.

# **Component Selection Guidance:**

| <u>Designation</u> | Typical Value | <u>Description</u>                                    | Example: Mfg./PN      |

|--------------------|---------------|-------------------------------------------------------|-----------------------|

| D1, D2, D3, D4     | 0.5 A, 1000V  | V <sub>CE</sub> detection diode – Ultra fast recovery | ON Semi MUR1100E      |

| DZ2, DZ3, DZ5, DZ6 | 16V, 1W       | Gate Voltage Surge Protection                         | 1N4745                |

| DZ1, DZ4           | 30V, 1W       | Detect input pin surge voltage protection             | 1N4751                |

| C1, C2, C3, C4     | 82μF, 35V     | Power supply filter – Electrolytic, low Impedance     | Panasonic EEU-FC1V820 |

| CTRIP1, CTRIP2*    | 0-47 pF, 40V  | Adj. Trip time – Multilayer ceramic or film*          | EPCOS B37979          |

| CS1, CS2*          | 0-650 pF, 40V | Adj. Trip time – Multilayer ceramic or film*          | EPCOS B37979          |

| OP1, OP2           | NEC PS2501    | Opto-coupler for fault signal isolation               | NEC PS2501            |

| CN1                | MTA .100"     | Input and gate drive connectors                       | AMP 641216-6          |

| CNG1, CNG2, CNTH   | MTA .100"     | Input and gate drive connectors                       | AMP 641216-2          |

<sup>\*</sup> Only required in certain specific applications. See VLA567-01R datasheet for more details.

Figure 3: Schematic and Component Selection Guide for the BG2G

Publication Date: May 29, 2015

Rev. 0

The board will normally be operated with two input voltage sources. A 5V logic source ( $+V_L$ ) provides drive for the high speed opto-couplers inside the hybrid gate driver and pull-up voltage for the fault signal isolation optos OP1 and OP2. A control power supply ( $+V_S$ ) provides power for the gate driver and is connected to the primary side of the DC-to-DC converters across Pins 43 and 44. The  $+V_S$  source is decoupled internally a low impedance electrolytic capacitor and therefore an external decoupling capacitor is not required to provide a stable, well-filtered DC source. The built-in DC-to-DC converters provide isolated gate drive power which consists of +16.8V ( $V_{CC}$ ), and -8.5 ( $V_{EE}$ ). The gate drive power supplies are decoupled using the low impedance electrolytic capacitors C1, C2, C3, and C4. It is very important that these capacitors have low enough impedance and sufficient ripple current capability to provide the required high current gate drive pulses. The  $100\mu F$  low impedance capacitors used on the BG2G are sized to supply 8A gate pulses at a 20kHz rate. If the application is operating at lower frequency or lower peak current it may be possible to reduce the size of these capacitors.

The hybrid gate driver amplifies the control input signal and produces high current gate drive at Pins 19 and 26. The gate drive current is adjusted by selecting the appropriate series gate resistance (R<sub>G</sub>). R<sub>G</sub> will normally be adjusted to provide suitable drive for the module being used considering dynamic performance, losses and switching noise. For more information on selecting R<sub>G</sub> see the "Driving IGBT Modules" application note. Protection against gate voltage surges is provided by DZ2, DZ3, DZ5, and DZ6. These zener diodes also help to control short circuit currents by shunting miller current away from the gate.

Short circuit protection is provided by means of desaturation detection. For details on the operation of this circuit consult the VLA567-01R datasheet. The collector voltage of each IGBT is detected through the series connected high voltage blocking diodes D1, D2 and D3, D4. The combined blocking voltage of the series connected diodes must be equal to or greater than the V<sub>CES</sub> rating of the IGBT. For applications using lower voltage IGBT modules, it is possible to use a single detection diode in each channel. DZ1 and DZ4 protect the gate driver's detect input (Pins 22 and 23) from voltage surges during reverse recovery of the high voltage blocking diodes. The capacitors CTRIP1 and CTRIP2 are used to adjust the driver's protection circuit trip time. The driver's default settings are sufficient for many applications so it may be possible to omit these capacitors. For details on the use of CTRIP1 and CTRIP2, consult the VLA567-01R datasheet.

If the gate driver's short circuit protection is activated, it immediately shuts down the gate drive and pulls the fault output pin low. Current flows from Vcc and through the LED in the fault isolation opto (OP1, OP2) causing the transistor in the fault isolation opto to turn on and pull the fault signal line (FO) at Pin 4 of CNIN low. This opto-isolated signal can now be used by the controller to detect the fault condition.

Publication Date: May 29, 2015

Rev. 0

# **Interface Circuit Requirements:**

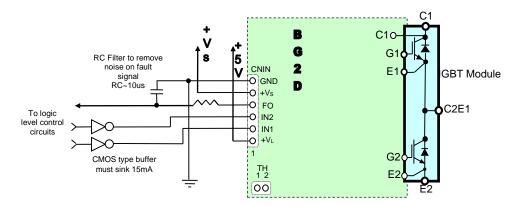

A typical interface circuit for the BG2G is shown in Figure 4.

Figure 1: BG2G External Wiring Diagram

A single control power supply  $(+V_S)$  is connected to Pin 5 of CNIN with its common at Pin 6. This supply provides all of the gate drive power for both channels. The current drawn from the  $+V_S$  supply will vary from less than 100mA to more than 500mA depending on the switching frequency and size of IGBT being driven. Consult the <u>hybrid gate driver application notes</u> for details on determining the required supply current for the gate driver. The gate driver supply current can then be converted into current drawn from the  $+V_S$  supply using the load current versus input current specification on the VLA567-01R datasheet.

A 5V logic supply is connected at Pin 1 of CNIN and shares the same common at Pin 6 of CNIN as the 15V control supply. The 5V supply is directly connected to Pins 4 and 40 of the VLA567-01R, which are internally connected to the respective anode of the LED in the high-speed opto-coupler. The 5V supply is also used to pull the output side of the fault isolation opto-couplers high.

The control signal interface is designed for use with standard 5V CMOS logic. The control input signals at Pins 2 and 3 of connector CNIN are used to turn the IGBTs on and off. These signals are active low which means that the gate driver output will be high (IGBT on) when they are pulled low. These control pins are connected directly to Pins 5 and 41 of the driver which are connected internally through a 240Ω limiting resistor to the cathode of the LED in the high speed opto-coupler (see Figure 1). When the control signal is pulled low, current flows from the 5V logic supply through the LED to turn on the gate driver's output. The control Pins must be pulled low with a buffer that is capable of sinking at least 16mA in order to turn on the high speed opto-coupler inside the hybrid gate driver. A CMOS buffer that actively pulls its output high in the off state (74HC04 or similar) is recommended for maintaining good common mode noise immunity. Open collector drive that allows IN1 and IN2 to float will degrade common mode noise immunity and is therefore not recommended.

The fault signal line on Pin 4 of CNIN is active low, which means that a fault condition will be indicated by a low level signal. During normal operation, Pin 4 is pulled high to the  $+V_L$  supply by the  $4.7k\Omega$  resistor R7. If either half of the hybrid gate driver detects a short circuit condition its fault isolation opto (OP1, OP2) will turn on and pull Pin 4 of CNIN low. When a fault is detected, the gate driver disables the output and produces a fault signal for a minimum of 1ms. Any signal on the fault line that is significantly shorter than 1ms cannot be a legitimate fault, so it should be ignored. Therefore, for a robust noise immune design, it is recommended that an RC filter with a time constant of approximately 10 $\mu$ s be added between Pin 4 and the controller as shown in Figure 4.

### **Thermistor Connection:**

The case temperature of the NX series device can be monitored by reading the resistance value of the built in NTC Thermistor. This is accessed on the BG2G board by the CNTH connector. The relationship between the resistance and the temperature measurement is given by the B constant as shown in Equation 1. The B constant can be found on the datasheet for the IGBT module. Solving for temperature of any given point Tx, with a reference temperature of 25°C we can derive Equation 2. Equation 2 is very useful because R<sub>25</sub>, the resistance with a case temperature of 25°C, can be easily measured. It is important to note that this equation is valid for temperatures measured in Kelvin (K) in which case  $T_{25} = 25+273 = 298K$ .

**EQ.1:** B =

$$(lnR_1 - lnR_2) / (1/T_1-1/T_2)$$

**EQ.2:**

$$T_x = B / (InR_x - InR_{25}) + T_{25}$$

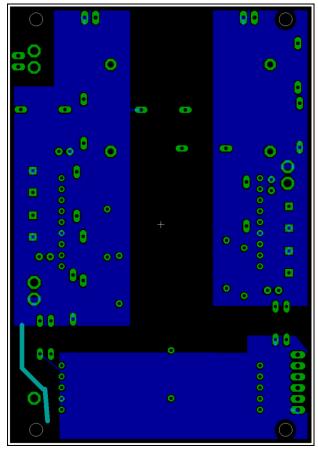

### **Printed Circuit Layout:**

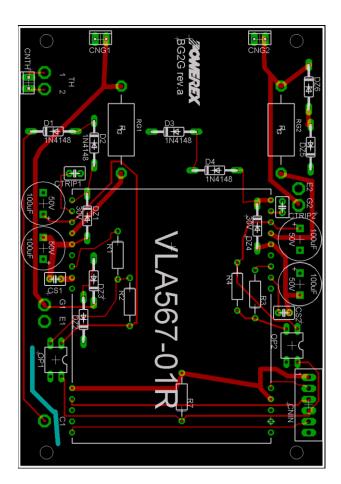

Figure 5 shows the layout of the BG2G two channel gate driver board. The compact 101mm x 70mm circuit board with few components clearly demonstrates the advantage of using the VLA567-01R. One important feature is the use of three ground plane islands for the regions of the PCB having high voltage differences. Two of the islands are tied to the IGBT emitter/circuit common of each output channel. The third island is connected to logic interface common at Pin 6 of CNIN. This layout provides shielding to help prevent undesirable coupling of noise between the control side and the gate drive channels.

Figure 2: BG2G PCB Layout

### **Additional Information:**

Detailed information about the operation and electrical characteristics of the  $\frac{VLA567-01R}{C}$  can be found on the datasheet. Information about calculating gate drive current and selection of series gate resistors (R<sub>G</sub>) can be found in the general IGBT module and gate drive application notes. For applications using higher current IGBT modules refer to the application notes for the  $\frac{VLA552-01R}{C}$  hybrid gate driver IC or the  $\frac{VLA553-01R}{C}$  which is a complete gate drive board designed for the 1800A/1700V or 2500A/1200V New Mega Power Dual Modules. For applications using high frequency optimized NFH series IGBT modules refer to the  $\frac{VLA513}{C}$  or  $\frac{VLA502-01}{C}$  application note. All of these documents are available on the Powerex website at  $\frac{www.pwrx.com}{C}$ . For design assistance with any of the products covered in this application note contact your local Powerex representative or Powerex application engineering at (724) 925-7272, Option 3.

Publication Date: May 29, 2015

Rev. 0