IEEE802.3AT POWER-OVER-ETHERNET POWERED DEVICE CONTROLLER

LTC4265

### DESCRIPTION

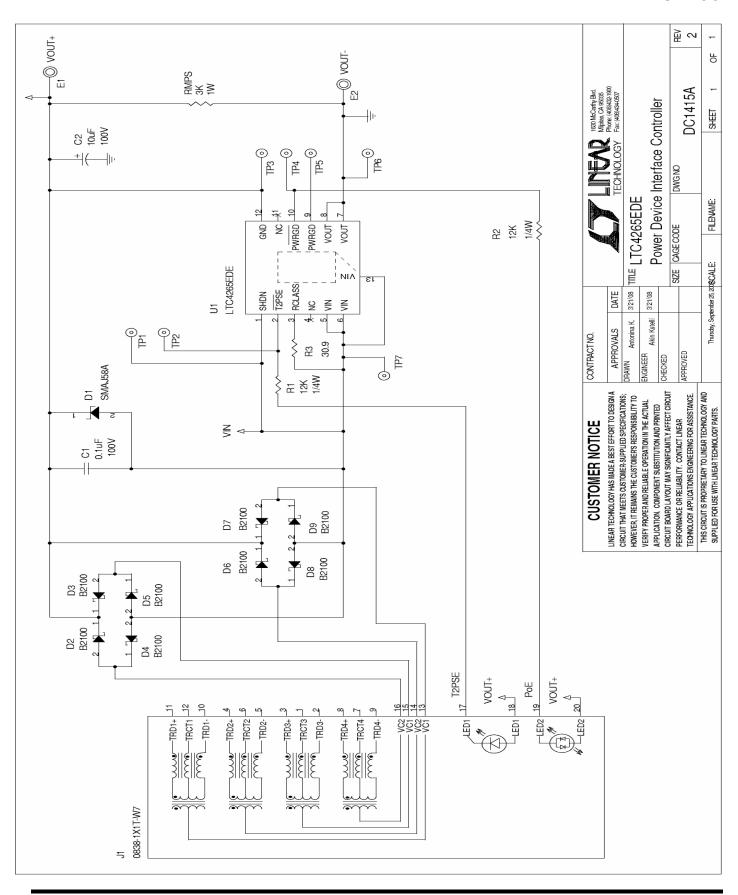

Demonstration circuit DC1415A features the LTC®4265CEDE, a third-generation Powered Device (PD) controller for Power over Ethernet (PoE) applications.

The LTC4265 is compliant to IEEE Standard 802.3at. It can handle up to 25.5W and recognizes 2-event classification.

The LTC4265 includes the PD controller circuitry and power MOSFET integrated into a tiny 3mm×4mm 12-pin DFN package.

The DC1415A board includes the entire front end of a typical PD; RJ45 connector, Ethernet magnetics, bridge rectifiers, surge protection, and PD controller, all in a 1"×2" board. Two status indicator LEDs are also included: one shows the PSE is powering the PD; and the other shows the PSE performed 2-event classification. A small load sufficient to as-

sure the PSE maintains power to the PD is also included.

The LTC4265 features complementary PWRGD and PWRGD outputs to facilitate interface to a wide range of off-the-shelf DC/DC converters.

Simply connect the outputs of the DC1415A to the DC/DC converter that's right for your application. Linear Technology offers many DC/DC converter demo boards that can be used with the DC1415A.

To obtain CAD files for the DC1415A demo board, or inquire about DC/DC converter demo boards, contact your local Linear Technology sales person or field applications engineer.

**17**, LT, and LTC are trademarks of Linear Technology Corporation; all other trademarks are the property of their respective owners.

### **QUICK START PROCEDURE**

- 1. To evaluate the LTC4265 without a load, skip to step 3.

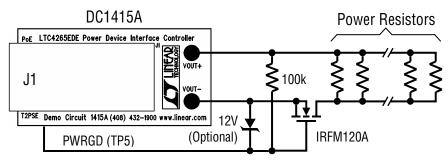

- 2. To evaluating the LTC4265 with a load, choose the connection diagram based on the type of load desired and wire the DC1415A board to the load as shown.

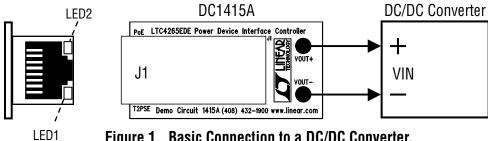

- a. Use Figure 1 if the DC/DC converter has sufficient built-in startup delay. The LTC4265 limits the current to 100mA during startup; if the DC/DC converter tries to draw more than 100mA during this time then startup will fail. The required delay depends on the input capacitance and Under-Voltage Lock Out (UVLO) threshold of the particular converter.

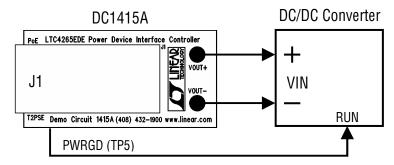

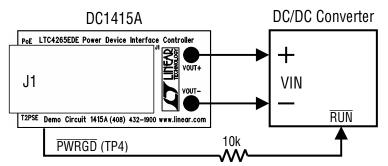

- b. Use Figure 2 or Figure 3 if the startup delay could be an issue.

- c. Use Figure 4 if the load is resistive.

- 3. Connect the output of the PSE to J1 on the DC1415A board with a CAT5e or CAT6 cable.

- Verify LED2 is lit, indicating the PSE has successfully detected and powered the PD. LED1 may also be lit if the PSE performed 2-event classification.

LTC4265

Figure 1. Basic Connection to a DC/DC Converter.

Figure 2. Connecting to a DC/DC Converter with Active-High RUN pin.

Figure 3. Connecting to a DC/DC Converter with Active-Low RUN pin.

Figure 4. Connecting to a Resistive Load.

IEEE802.3AT POWER-OVER-ETHERNET POWERED DEVICE CONTROLLER

LTC4265

#### **OPERATION**

#### **Classification Signature**

The RCLASS resistor (R3) determines the classification signature. The DC1415A board comes with R3=30.9 $\Omega$  for class 4. If a different class signature is desired, simply change R3 according to Table 1.

Table 1. RCLASS Resistor Values.

| PD CLASS | RCLASS ( $\Omega$ , 1%) |

|----------|-------------------------|

| 0        | Open (no resistor)      |

| 1        | 124                     |

| 2        | 69.8                    |

| 3        | 45.3                    |

| 4        | 30.9                    |

#### **LED Indicators**

There are two LEDs on the front of J1 as shown in Figure 1. In a typical PD application a PHY chip would drive these LEDs to indicate the status of the Ethernet link or traffic activity; however, on the DC1415A board the LTC4265 drives the LEDs to indicate PoE status.

The PWRGD pin of the LTC4265 drives LED2. LED2 is lit continuously while the PD is powered by the PSE. To disable LED2 remove R2.

The T2PSE pin drives LED1. LED1 will be lit if the PSE performed 2-event classification, indicating the PSE is Type 2. To disable LED1 remove R1.

#### **Power Supply Startup**

The LTC4265 limits the current to 100mA during startup. If the DC/DC converter attempts to draw more than 100mA while the LTC4265 is still limiting the current then startup will fail.

Many DC/DC converters include startup delay sufficient to prevent this situation. Such a converter may be connected to the DC1415A board as shown in Figure 1.

However, some DC/DC converters have short startup delays. To avoid startup problems it is recommended to use either the PWRGD or PWRGD output to inhibit startup of the DC/DC converter until the LTC4265 finishes limiting the inrush current.

Use PWRGD if the DC/DC converter has an activehigh control input, as shown in Figure 2.

Use PWRGD if the DC/DC converter has an active-low control input, as shown in Figure 3. A 10k resistor limits the current between PWRGD and RUN in the event of a voltage transient at the J1 input. A resistive load may be used to evaluate the thermal properties of the LTC4265; in this case use a series MOSFET to prevent startup problems, as shown in Figure 4. PWRGD holds the MOSFET gate low until the LTC4265 is ready to supply full current.

**CAUTION**: The MOSFET may be destroyed if its gate is pulled all the way to VOUT+ by the pull-up resistor. The MOSFET is protected by a 14V clamp inside the LTC4265; however, if the wire to PWRGD were disconnected – or mistakenly connected to  $\overline{PWRGD}$  – then the MOSFET would not be protected. Therefore it is recommended to use a zener diode connected directly across the gate and source pins of the MOSFET as shown in Figure 4.

IEEE802.3AT POWER-OVER-ETHERNET POWERED DEVICE CONTROLLER

LTC4265

#### **Minimum LOAD**

The PSE may discontinue power if the load current is below 10mA. The DC1415A includes a 3k load (RMPS) across its outputs to prevent the PSE from turning off power. RPMS may be removed is the DC1415A is connected to a load that draws at least 10mA continuously.

#### IEEE802.3AT POWER-OVER-ETHERNET POWERED DEVICE CONTROLLER

# LTC4265