# AK1110AEU

## 2ch Output, Ultra High PSRR, Ultra Low Noise LDO Regulator

#### 1. General Description

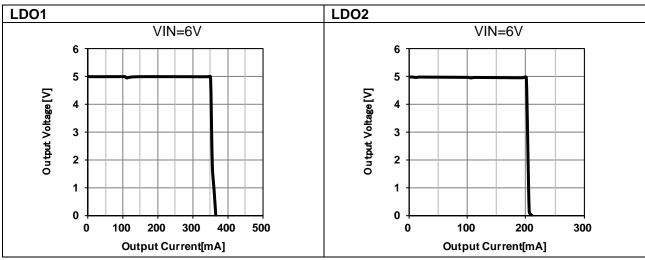

The AK1110AEU is a dual output low dropout linear regulator with ON/OFF control. Each output can supply 100mA and 200mA load current. The AK1110AEU is an integrated circuit achieving excellent ripple rejection and low output noise characteristics with silicon monolithic bipolar structure. In addition, over current and thermal protections are integrated. It is especially well suited for noise sensitive applications. The AK1110AEU is housed in a small and thin type PLP10-2725 package with an exposed pad. It is designed for space saving requiring systems.

#### 2. Feature

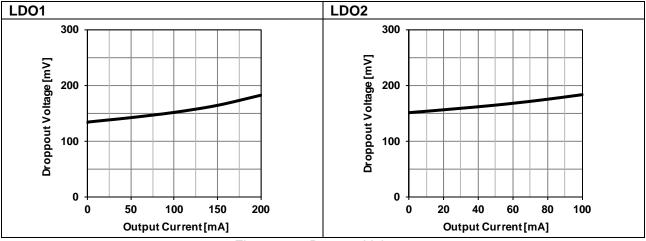

Operating Voltage Range 6V to 14V Maximum Output Current LDO1 200mA LDO2 100mA High Precision output voltage LDO1 5.0V LDO<sub>2</sub> 5.0V Dropout Voltage LDO1 600mV at lo=200mA LDO2 600mV at Io=100mA · Output Noise LDO1  $2\mu V_{RMS}$  at 10Hz to 100kHz LDO2  $1\mu V_{RMS}$  at 10Hz to 100kHz Ripple Rejection Ratio LDO1 83dB at f=1kHz LDO2 100dB at f=1kHz

- · NP terminal to reduce output noise

- On/Off Control Function

- Over Current Protection, Thermal Protection

- Ceramic Capacitor Available

- Small Package PLP10-2725 (2.7mm×2.5mm×0.6mm)

#### 3. Application

· High precision DAC applications, RF, PLL, etc.

## 4. Table of Contents

| 1.  | General Description              | 1  |

|-----|----------------------------------|----|

| 2.  | Feature                          | 1  |

| 3.  | Application                      | 1  |

| 4.  | Table of Contents                | 2  |

| 5.  | Block Diagram                    | 3  |

| 6.  | Pin Configurations and Functions | 4  |

|     | Pin Configurations               | 4  |

|     | Pin Functions                    | 4  |

| 7.  | Absolute Maximum Ratings         | 5  |

| 8.  | Recommended Operating Conditions | 6  |

| 9.  | Electrical Characteristics       | 6  |

|     | Functional Descriptions          |    |

|     | Output Capacitor and Stability   | 8  |

|     | Noise Bypass Capacitor           | 8  |

|     | Output Enable Control            | 8  |

|     | Over Current Protection          | 8  |

|     | Thermal Protection               | 8  |

|     | Attention to PCB Layout          | 8  |

|     | Characteristic Examples          | 9  |

| 11. | Definition of Terms              | 16 |

| 12. | Recommended External Circuits    | 17 |

| 13. | Package                          | 18 |

|     | Outline Dimensions               | 18 |

|     | I Marking                        | 18 |

| 14. | Ordering Guide                   | 18 |

|     | Revision History                 |    |

| IMF | PORTANT NOTICE                   | 19 |

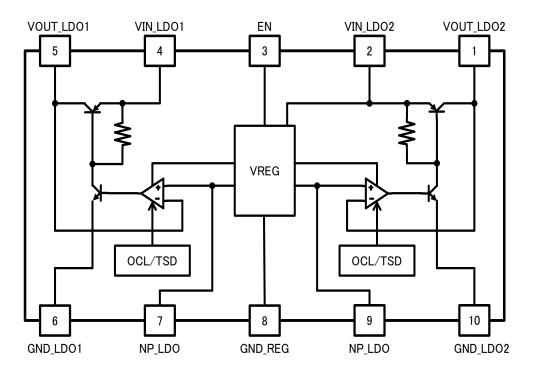

## 5. Block Diagram

Figure 1. Block Diagram

## 6. Pin Configurations and Functions

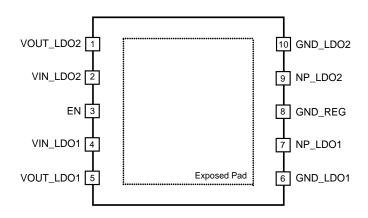

## **■ Pin Configurations**

Figure 2. Pin Configurations (Top View)

## **■ Pin Functions**

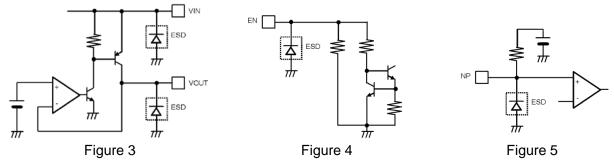

| No. | Name                    | I/O | Internal Equivalent Circuit | Description                                                                                            |

|-----|-------------------------|-----|-----------------------------|--------------------------------------------------------------------------------------------------------|

| 1   | VOUT_LDO2               | 0   | Figure 3                    | LOD2 Output                                                                                            |

| 2   | VIN_LDO2                | Р   | Figure 3                    | LOD2 Input                                                                                             |

| 3   | EN                      | I   | Figure 4                    | On/Off Control Terminal of the LDO1 and LDO2 (High active) The pull-down resister (300kΩ) is built-in. |

| 4   | VIN_LDO1                | Р   | Figure 3                    | LDO1 Input                                                                                             |

| 5   | VOUT_LDO1               | 0   | Figure 3                    | LDO1 Output                                                                                            |

| 6   | GND_LDO1                | -   | -                           | LDO1 Ground                                                                                            |

| 7   | NP_LDO1                 | 0   | Figure 5                    | Noise Bypass Terminal of the LDO1 Connect a bypass capacitor between NP_LDO1 and GND.                  |

| 8   | GND_REG                 | •   | -                           | GND terminal of the internal 5V regulator                                                              |

| 9   | NP_LDO2                 | 0   | Figure 5                    | Noise Bypass Terminal of the LDO2<br>Connect a bypass capacitor between<br>NP_LDO2 and GND.            |

| 10  | GND_LDO2                | -   | -                           | LDO2 Ground                                                                                            |

| -   | Exposed Pad<br>(Note 2) | -   | -                           | Heat Dissipation Pad It is connected to GND internally.                                                |

Note 1. I(Input terminal), O(Output terminal), P(Power terminal)

Note 2. The exposed pad should be connected to the GND plane.

## **Equivalent Circuits**

| 7. Absolute Maximum Ratings                                  |                  |      |      |      |           |  |  |  |

|--------------------------------------------------------------|------------------|------|------|------|-----------|--|--|--|

| (GND_LDO1 = GND_LDO2 = GND_REG =0V)                          |                  |      |      |      |           |  |  |  |

| Parameter                                                    | Symbol           | Min. | Max. | Unit | Condition |  |  |  |

| Supply Voltage<br>(VIN_LDO1, VIN_LDO2)                       | V <sub>IN</sub>  | -0.3 | 16   | V    |           |  |  |  |

| Reverse Bias (VOUT_LDO1, VOUT_LDO2)                          | $V_{REV}$        | -0.3 | 6    | V    |           |  |  |  |

| Np Terminal Voltage (NP_LDO1, NP_LDO2)                       | $V_{NP}$         | -0.3 | 16   | V    |           |  |  |  |

| EN Terminal Voltage (EN)                                     | $V_{EN}$         | -0.3 | 16   | V    |           |  |  |  |

| GND_LDO1- GND_LDO2<br>GND_LDO1- GND_REG<br>GND_LDO2- GND_REG | VGND             | -0.3 | 0.3  | V    |           |  |  |  |

| Junction Temperature                                         | Tj               | -    | 150  | °C   |           |  |  |  |

| Storage Temperature Range                                    | T <sub>STG</sub> | -55  | 150  | °C   |           |  |  |  |

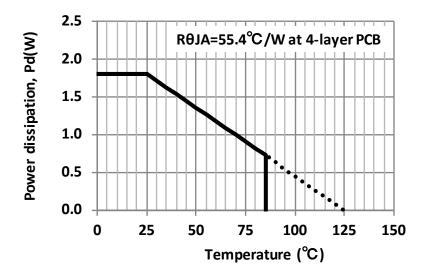

| Power Dissipation                                            | P <sub>D</sub>   | -    | 1800 | mW   | (Note 5)  |  |  |  |

Note 3. All voltages are with respect to GND. GND=0V

Note 5. When the temperature is more than 25°C, derating by -18mW is needed. Thermal resistance  $\theta_{JA}$ = 55.4 °C /W (Mounted on the four-layer board that conforms to the JEDEC51)

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Figure 6. Thermal Derating Curve

Note 4. The exposed pad should be connected to the GND plane.

## 8. Recommended Operating Conditions

| Parameter                      | Symbol   | Min. | Тур. | Max. | Unit | Comments |

|--------------------------------|----------|------|------|------|------|----------|

| Operating Temperature Range    | Ta       | -40  | -    | 85   | °C   |          |

| Operating junction temperature | $T_j$    | -40  |      | 125  | °C   |          |

| Operating Voltage Range        | $V_{IN}$ | 6    | -    | 14   | V    |          |

Note 6. All voltages are with respect to GND. GND=0V

## 9. Electrical Characteristics

$(Ta = -40^{\circ}C \sim +85^{\circ}C, \, V_{\text{IN}} = V_{\text{EN}} = 6.0 \, V, \, C_{\text{IN}} = 1.0 \, uF, \, C_{\text{NP1}} = C_{\text{NP2}} = 10 \, uF, \, C_{\text{OUT1}} = C_{\text{OUT2}} = 10 \, uF)$

| Parameter                               | Symbol               | Test Conditions                              | Min.    | Typ. | Max. | Unit          |

|-----------------------------------------|----------------------|----------------------------------------------|---------|------|------|---------------|

| Common items of LDO1 and LDO            |                      |                                              | 171111. | тур. | wax. | Offic         |

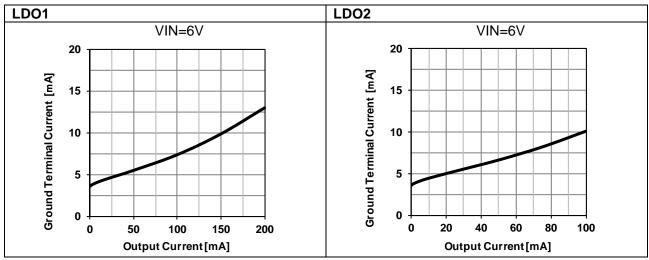

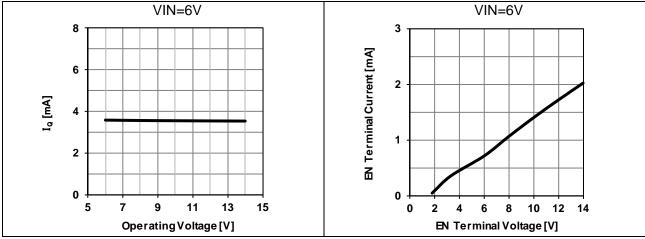

| Quiescent Current                       | IQ                   | I <sub>OUT</sub> = 0mA                       | -       | 3.0  | 5.0  | mA            |

| Ground Terminal<br>Current              | I <sub>GND</sub>     | I <sub>OUT1</sub> +I <sub>OUT2</sub> =32mA   | -       | 5.0  | 7.0  | mA            |

| Standby Current                         | I <sub>STANDBY</sub> | V <sub>EN</sub> =0V                          | -       | 0.01 | 2.0  | μΑ            |

| EN terminal high level                  | $V_{ENH}$            |                                              | 1.8     | -    | -    | V             |

| EN terminal Low level                   | $V_{ENL}$            |                                              | 1       | ı    | 0.35 | V             |

| EN Terminal Current                     | I <sub>ENLKG</sub>   | V <sub>EN</sub> =1.8V                        | -       | 50   | 150  | μΑ            |

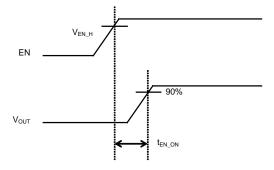

| EN terminal on time (Note 10)           | t <sub>ENON</sub>    |                                              | -       | 55   | 100  | ms            |

| Thermal protection Shutdown Temperature | T <sub>TSD</sub>     |                                              | 135     | -    | 155  | °C            |

| LD01                                    |                      |                                              |         |      |      |               |

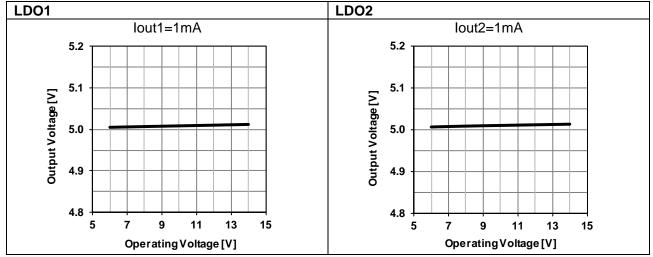

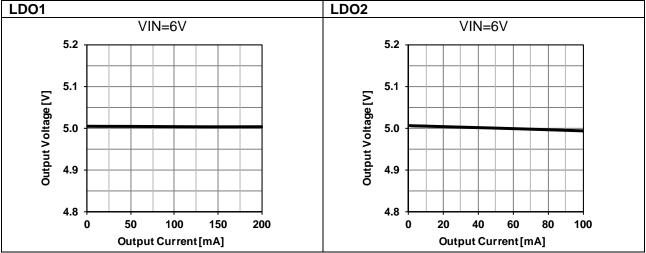

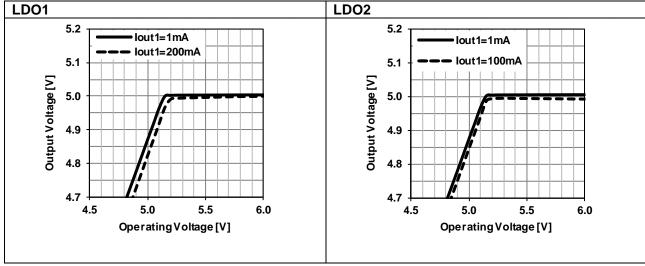

| Output Voltage                          | V <sub>OUT1</sub>    | I <sub>OUT1</sub> = 1mA to 200mA             | 4.90    | 5.0  | 5.10 | V             |

| Line Regulation                         | LinReg₁              | $\Delta V_{IN1} = 5V$                        |         | 6    | 20   | mV            |

| Load Regulation                         | LoaReg <sub>1</sub>  | I <sub>OUT1</sub> = 1mA to 200mA             |         |      | 50   | mV            |

| Dropout Voltage                         | $V_{DROP1}$          | I <sub>OUT1</sub> = 200mA                    |         |      | 600  | mV            |

| Maximum Output<br>Current (Note 9)      | I <sub>OUTMAX1</sub> | $V_{OUT1} = V_{OUT1}(typ) \times 0.9$        | 220     |      |      | mA            |

| Output noise(Note 8)                    | V <sub>noise1</sub>  | I <sub>OUT1</sub> =100mA, f=10Hz<br>to100kHz |         | 2.0  |      | $\mu V_{RMS}$ |

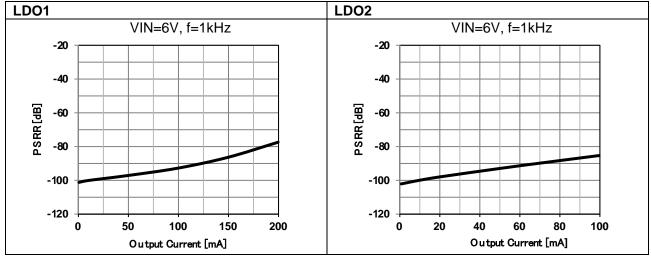

|                                         |                      | I <sub>OUT1</sub> = 100mA, f=1kHz            |         | 83   |      | dB            |

| Ripple rejection (Note 8)               | PSRR₁                | I <sub>OUT1</sub> = 100mA, f=100kHz          |         | 80   |      | dB            |

| (Note o)                                |                      | I <sub>OUT1</sub> = 100mA, f=1MHz            |         | 70   |      | dB            |

| LDO2                                    |                      |                                              |         |      |      |               |

| Output Voltage                          | $V_{OUT2}$           | I <sub>OUT2</sub> = 1mA to 100mA             | 4.90    | 5.0  | 5.10 | V             |

| Line Regulation                         | LinReg <sub>2</sub>  | $\Delta V_{IN2} = 5V$                        |         | 5    | 15   | mV            |

| Load Regulation                         | LoaReg <sub>2</sub>  | $I_{OUT2}$ = 1mA to 100mA                    |         |      | 25   | mV            |

| Dropout Voltage                         | $V_{DROP2}$          | $I_{OUT2} = 100 \text{mA}$                   |         |      | 600  | mV            |

| Maximum Output<br>Current (Note 9)      | I <sub>OUTMAX2</sub> | $V_{OUT2} = V_{OUT2}(typ) \times 0.9$        | 120     |      |      | mA            |

$(Ta = -40^{\circ}C \sim +85^{\circ}C, V_{IN} = V_{EN} = 6.0V, C_{IN} = 1.0uF, C_{NP1} = C_{NP2} = 10uF, C_{OUT1} = C_{OUT2} = 10uF)$

| (1.0 1.0 0.1 1.0 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1.1 0.1 1 |                     |                                    |      |      |      |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------|------|------|---------------|

| Parameter Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | Test Conditions                    | Min. | Тур. | Max. | Unit          |

| Output Noise (Note 8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>noise2</sub> | $I_{OUT2} = 1$ mA, f=10Hz to100kHz |      | 1.0  |      | $\mu V_{RMS}$ |

| Disale Deiestica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · PSRR <sub>2</sub> | I <sub>OUT2</sub> = 1mA, f=1kHz    |      | 100  |      | dB            |

| Ripple Rejection (Note 8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | I <sub>OUT2</sub> = 1mA, f=100kHz  |      | 83   |      | dB            |

| (11010 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | I <sub>OUT2</sub> = 1mA, f=1MHz    |      | 76   |      | dB            |

Note 7. All voltages are with respect to GND. GND=0V

Note 8. Guaranteed by design. This value is not tested.

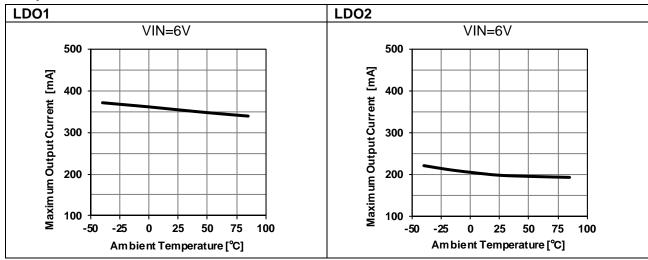

Note 9. The maximum output current is limited by Ta and power dissipation.

Note 10. Definition of rise time is shown below.

#### 10. Functional Descriptions

#### ■ Output Capacitor and Stability

To ensure loop stability, select output capacitors that have more than 3.3uF effective capacitance and  $0.1\Omega$  or less ESR. If the capacity of the output capacitor is increased, peak voltage fluctuation caused by load current variation is reduced. Therefore, the transient response characteristics are improved. DC bias and temperature characteristics must be considered when using ceramic capacitors.

#### ■ Noise Bypass Capacitor

It is recommended that the effective capacitance of the capacitor connected to the NP pin is  $3.3 \, \mu F$  or higher. Increase the capacitance of a capacitor at the NP pin to prioritize the output noise and ripple rejection characteristics in the system design. The NP pin capacitance does not affect output stability.

#### ■ Output Enable Control

Output ON/OFF control is available by the EN pin. When output is turned OFF, IC current consumption can be minimized.

| EN terminal voltage (V <sub>EN</sub> ) | Operating state |

|----------------------------------------|-----------------|

| V <sub>EN</sub> > 1.8V                 | ON              |

| V <sub>EN</sub> < 0.35V                | OFF             |

#### **■** Over Current Protection

The AK1110 limits the output current for IC protection when the output current exceeds the maximum rating such as when it is shorted to ground. The AK1110 automatically returns to normal operation when the output current decreases.

#### **■** Thermal Protection

If the junction temperature exceeds the maximum rating as power loss of the AK1110 is large, the output of the AK1110 is turned off by the thermal protection function. The AK1110 automatically returns to normal operation when the junction temperature decreases.

#### ■ Attention to PCB Layout

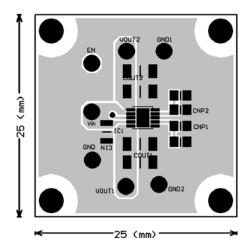

Package: PLP10-2725

Board Material: 4-layer glass epoxy substrate, (x=25mm, y=25mm, t=1.6mm, Copper pattern thickness 18um)

Figure 7. Recommended Layout

- 1. CIN should be located as close as possible to the VIN1, VIN2 pin and GND.

- 2. COUT1, COUT2 should be located as close as possible to the VOUT1, VOUT2 pin and GND.

- 3. CNP1, CNP2 should be located as close as possible to the NP1, NP2 pin and GND.

- 4. GND plane should be large as much as possible.

- 5. The exposed pad is a common ground of the IC. It must be connected to the PCB GND.

- 6. Via halls are effective for heat dissipation to each layer of PCB.

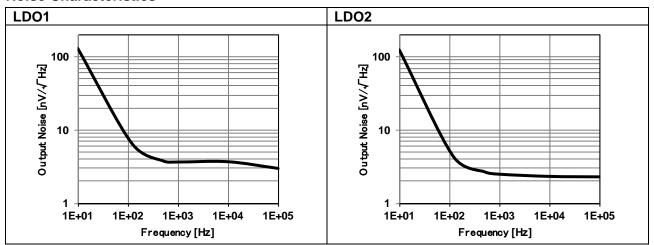

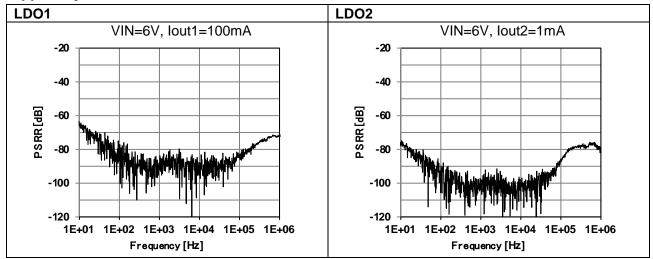

## **■** Characteristic Examples

$C_{IN}=1.0uF, C_{NP1}=C_{NP2}=10uF, C_{OUT1}=C_{OUT2}=10uF$

## **Noise Characteristics**

Figure 8. Output Noise Level (1/f)

To reduce the output noise, increase capacitance of the NP capacitors. A 3.3 uF or higher NP capacitor is recommended.

## **Ripple Rejection Characteristics**

Figure 98. Ripple Rejection

Figure 90. Ripple Rejection vs. lout

The ripple rejection characteristic depends on the capacity and characteristics of the output capacitor. Ripple rejection characteristics over 50 kHz are greatly affected by the output capacitor capacitance and PCB pattern.

## **DC Characteristics**

Figure 101. Input voltage fluctuation

Figure 112. Load fluctuation

Figure 123. Input vs Output Voltage

Figure 134. Dropout Voltage

Figure 145. Ground Terminal Current

Figure 156. Quiescent Current

Figure 167. V<sub>EN</sub> vs. I<sub>EN</sub>

Figure 178. Overcurrent protection characteristics

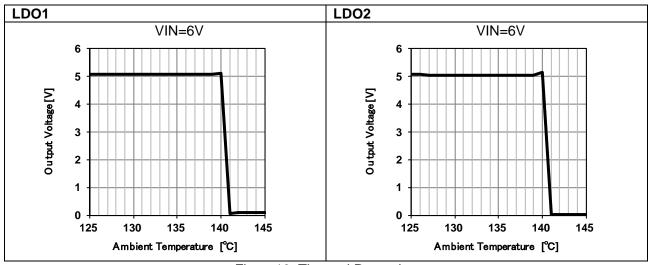

Figure 19. Thermal Protection

## **Temperature Characteristic**

Figure 180. Maximum Output Current

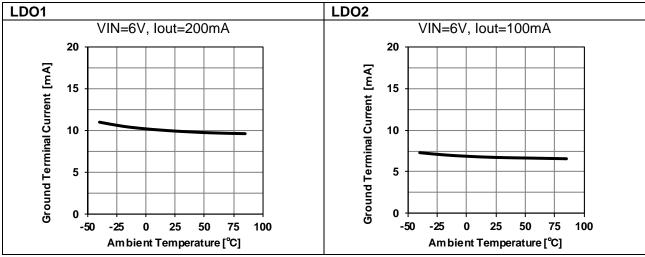

Figure 191. Ground Terminal Current

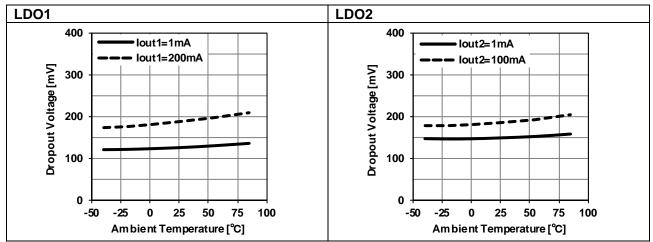

Figure 202. Dropout Voltage

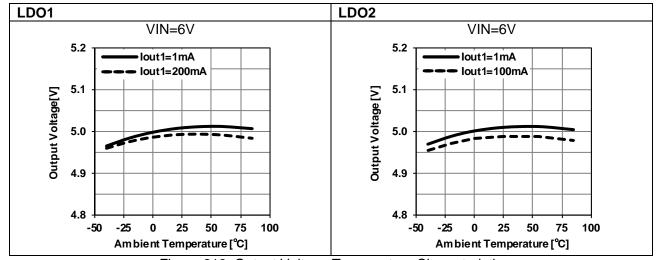

Figure 213. Output Voltage Temperature Characteristic

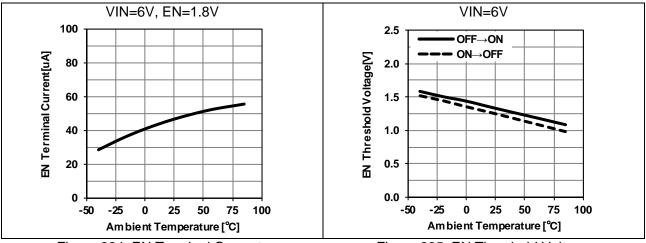

Figure 224. EN Terminal Current

Figure 235. EN Threshold Voltage

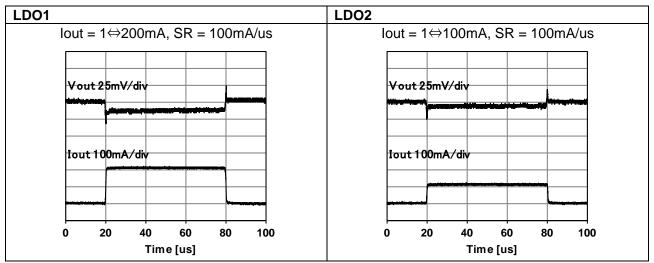

#### **Transient Characteristic**

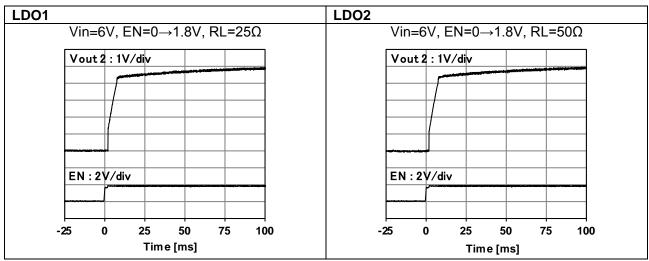

Figure 246. Starting Characteristic

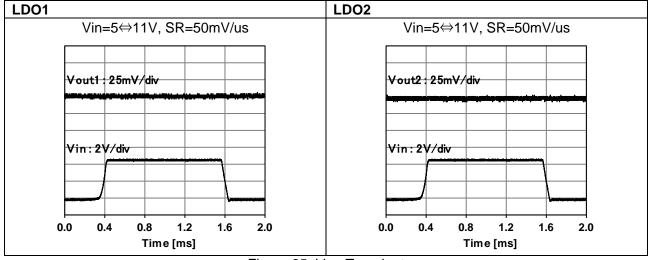

Figure 25. Line Transient

Figure 268. Load Transient

#### 11. Definition of Terms

## Maximum Output Current (I<sub>OUT\_MAX</sub>)

It is defined as the output current that the output voltage with 1mA load current becomes 90%.

## Dropout Voltage (V<sub>DROP</sub>)

It is a difference between the input voltage and the output voltage when the output voltage drops 100mV from its nominal value by decreasing the input voltage gradually.

#### Line Regulation (LinReg)

It is the fluctuation of the output voltage caused by input voltage variation.

#### Load Regulation (LoaReg)

It is the fluctuation of the output voltage with load current variation when assuming the input voltage is 6V.

## Ripple Rejection (PSRR)

It is a voltage ratio between the input and the output waveforms when 200 mVp-p AC input is superimposed to the 6.5V input voltage.

#### Standby Current (I<sub>STANDBY</sub>)

It is the input current that flows when the output voltage is turned OFF by setting the EN pin.

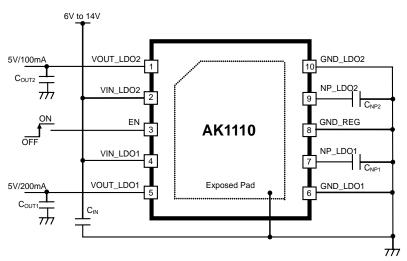

## 12. Recommended External Circuits

## **External Circuit**

Figure 2927. External Circuit (Top View)

Table 1. Recommended External Parts List

|                       | Symbol            | Effective Value | Remarks    |

|-----------------------|-------------------|-----------------|------------|

| Input Capacitor       | C <sub>IN</sub>   | 1.0μF or higher |            |

| LDO1 Output Capacitor | C <sub>OUT1</sub> | 3.3μF or higher | ESR ≤ 0.1Ω |

| LDO2 Output Capacitor | C <sub>OUT2</sub> | 3.3μF or higher | ESR ≤ 0.1Ω |

| LDO1 NP Capacitor     | C <sub>NP1</sub>  | 3.3μF or higher |            |

| LDO2 NP Capacitor     | C <sub>NP2</sub>  | 3.3μF or higher |            |

Note 11. The table above is recommended examples. Please confirm and select optimal values with your system board.

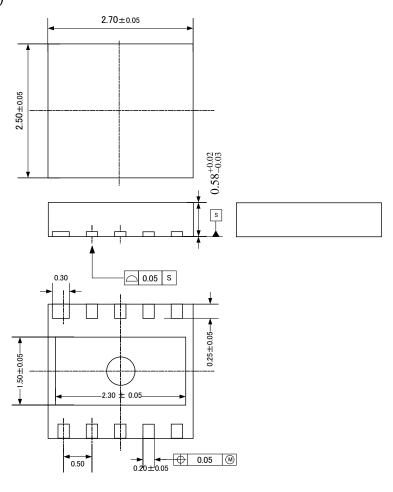

## 13. Package

## **■** Outline Dimensions

• PLP10-2725 (Unit: mm)

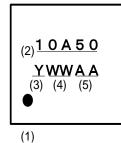

## ■ Marking

- (1) 1pin Indication

- (2) Market No.

- (3) Year code (last1digit)

- (4) Week code

- (5) Management code

## 14. Ordering Guide

AK1110AEU50

Ta = -40 to 85°C

PLP10-2725

| 15. Revision History |  |

|----------------------|--|

|----------------------|--|

| Date (Y/M/D) | Revision | Reason        | Page | Contents |

|--------------|----------|---------------|------|----------|

| 16/12/26     | 00       | First Edition |      |          |

#### **IMPORTANT NOTICE**

- 0. Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

- 1. All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.

- 2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

- 3. Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption.

- 4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

- 6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

- 7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.

016016348-E-00 - 19 - 2016/12