# Semiconductor Devices, Silicon Hybrid Switching Regulators High Reliability Types

|                 | Test Level T <sub>1</sub> | Test Level T <sub>2</sub> |  |  |

|-----------------|---------------------------|---------------------------|--|--|

| PIC 645/646/647 | PIC 7513/7514/7515        | PIC 7531/7532/7533        |  |  |

| PIC 655/656/657 | PIC 7516/7517/7518        | PIC 7534/7535/7536        |  |  |

### Contents

- 1.0 Scope

- 2.0 Applications Documents3.0 Requirements

- 4.0 Quality Assurance Provisions

### 1.0 SCOPE

This specification defines the detail requirements for High Reliability Hybrid Switching regulators. Very extensive 100% testing for parameter stability has been included in the Quality Assurance Provisions.

### 1.1a Absolute Maximum Ratings

|                                                                                                                                                                                                                                                                       | T <sub>1</sub> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                                                                                                                                                                                                                                                                       | PIC7513        | PIC7514        | PIC7515        | PIC7516        | PIC7517        | PIC7518        |

|                                                                                                                                                                                                                                                                       | T <sub>2</sub> |

|                                                                                                                                                                                                                                                                       | PIC7531        | PIC7532        | PIC7533        | PIC7534        | PIC7535        | PIC7536        |

|                                                                                                                                                                                                                                                                       | (PIC645)       | (PIC646)       | (PIC647)       | (PIC655)       | (PIC656)       | (PIC657)       |

| Input Voltage, V <sub>4-2</sub> Output Voltage, V <sub>1-2</sub> Drive-Input Reverse Voltage, V <sub>3-4</sub> Continuous Output Current, I <sub>1</sub> Peak Output Current Drive Current, I <sub>3</sub> Thermal Resistance Junction to Case, $\theta_{\text{J-C}}$ | 60V            | 80V            | 100V           | -60V           | 80V            | -100V          |

|                                                                                                                                                                                                                                                                       | 60V            | 80V            | 100V           | -60V           | 80V            | -100V          |

|                                                                                                                                                                                                                                                                       | 5V             | 5V             | 5V             | -5V            | 5V             | -5V            |

|                                                                                                                                                                                                                                                                       | 15A            | 15A            | 15A            | -15A           | 15A            | -15A           |

|                                                                                                                                                                                                                                                                       | 20A            | 20A            | 20A            | -20A           | 20A            | -20A           |

|                                                                                                                                                                                                                                                                       | -0.4A          | -0.4A          | -0.4A          | 0.4A           | 0.4A           | 0.4A           |

| Power Switch Commutating Diode Case to Ambient, θ <sub>C-A</sub> Operating Temperature Range, T <sub>C</sub> Maximum Junction Temperature, T <sub>j</sub> Storage Temperature Range                                                                                   |                |                | 2°C<br>        | C/W            |                |                |

|    |                             |                       | PIC7513/14/15<br>PIC7531/32/33 |      | PIC7516/17/16<br>PIC7534/35/36 |      |       |        |       |                                                               |

|----|-----------------------------|-----------------------|--------------------------------|------|--------------------------------|------|-------|--------|-------|---------------------------------------------------------------|

|    | Test                        | Symbol                | Min.                           | Тур. | Max.                           | Min. | Тур.  | Max.   | Units | Conditions                                                    |

| 1  | Current Delay Time          | tai                   | -                              | 35   | 60                             | _    | 35    | ഭറ     | ns    | V <sub>III</sub> = 25V (-25V)                                 |

| 2  | Current Rise Time           | t <sub>ri</sub>       |                                | 65   | 150                            | -    | 65    | 175    | ns    | $V_{out} = 5V(-5V)$                                           |

| 3  | Voltage Rise Time           | t <sub>rv</sub>       |                                | 40   | 60                             | -    | 40    | 60     | ns    | ! <sub>out</sub> = 7A (-7A)                                   |

| 4  | Voltage Storage Time        | t <sub>sv</sub>       |                                | 1200 | -                              | _    | 1200  | _      | ns    | I <sub>3</sub> = -30mA (30mA) (Note 5)                        |

| 5  | Voltage Fall Time           | t <sub>fv</sub>       | ~                              | 70   | 175                            | -    | 100   | 300    | ns    | See Figure 1                                                  |

| 6  | Current Fall Time           | t <sub>fi</sub>       |                                | 175  | 300                            | -    | 175   | 300    | ns    | See Notes 1, 2, 4                                             |

| 7  | Efficiency (Notes 2 and 4)  | η                     |                                | 85   | _                              | _    | 85    |        | %     |                                                               |

| 8  | On State Voltage (Note 3)   | V4-1 (On)             |                                | 1.0  | 1.5                            |      | -1.0  | -1.5   | v     | 14 = 7A (-7A), 13 = -0.03A (0.03A)                            |

| 9  | On-State Voltage (Note 3)   | V <sub>4-1</sub> (on) |                                | 2.5  | 3.5                            | _    | - 2.5 | -3.5   | ٧     | $I_4 = 15A (-15A), I_3 = -0.03A (0.03A)$                      |

| 10 | Diode Fwd: Voltage (Note 3) | V <sub>2-1 (on)</sub> |                                | 0.85 | 1.25                           | _    | -0.85 | - 1.25 | ٧     | 12 = 7A (-7A)                                                 |

| 11 | Diode Fwd. Voltage (Note 3) | V <sub>2-1</sub> (on) |                                | 0.95 | 1.75                           |      | -0.95 | -1.75  | V     | I <sub>2</sub> = 15A (-15A)                                   |

| 12 | Off-State Current           | 14-1                  |                                | 0.1  | 10                             | -    | -0.1  | - 10   | μA    | V <sub>4</sub> = Rated input voltage                          |

| 13 | Off-State Current           | 14-1                  | -                              | 10   | 1000                           |      | - 10  | 1000   | μA    | V <sub>4</sub> = Rated input voltage, T <sub>A</sub> = 100°C  |

| 14 | Diode Reverse Current       | 11-2                  | -                              | 1.0  | 10                             |      | - 1.0 | -10    | μA    | V <sub>1</sub> = Rated output voltage                         |

| 15 | Diode Reverse Current       | <sup>1</sup> 1-2      | -                              | 500  | 1000                           | _    | - 500 | - 1000 | μΑ    | V <sub>1</sub> = Rated output voltage, T <sub>A</sub> = 100°C |

## Notes:

- 1. In switching an inductive load, the current will lead the voltage on turn-on and lag the voltage on turn-off (see Figure 1). Therefore, Voltage Delay Time  $(t_{DV})\cong t_{di}+t_{fi}$  and Current Storage Time  $(t_{Si})\cong t_{SV}+t_{fV}$ .

- The efficiency is a measure of internal power losses and is equal to Output Power divided by Input Power. The switching speed circuit of Figure 1, in which the efficiency is measured, is representative of typical operating conditions for the PIC600 series switching regulators.

- 3. Pulse test. Duration =  $\leq$  400  $\mu$ sec.

- 4. As can be seen from the switching waveforms shown in Figure 1, no reverse or forward recovery spike is generated by the commutating diode during switching! This reduces self-generated noise, since no current spike is fed through the switching regulator. It also improves efficiency and reliability, since the power switch only carries current during turn-on.

- 5. To insure safe operation, the absolute value of  $I_3$  should be a minimum of 30 mA during  $I_{\{0n\}}$ . Operation with  $I_3$  below 30 mA can permanently damage the device.

#### **Power Dissipation Considerations**

The total power losses in the switching regulator is the sum of the switching losses, and the power switch and diode D.C. losses. Once total power dissipation has been determined, the Power Dissipation curve, or thermal resistance data may be used to determine the allowable case or ambient temperature for any operating condition.

The switching losses curve presents data for a frequency of 20 kHz. To find losses at any other frequency, multiply by t/20 kHz. The D.C. losses curves present data for a duty cycle of 0.2. To find D.C. losses at any other duty cycle, multiply by D/0.2 for the power switch and by (1-D)/0.8 for the diode.

At frequencies much below 10 kHz the above method for determining the allowable case of ambient temperature becomes invalid and a detailed transient analysis must be performed. Microsomi will supply transient thermal impedance information on request.

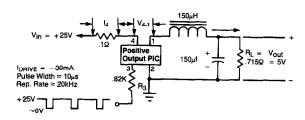

Positive Output Switching Speed Circuit

Note: No Diode Reverse or Forward Recovery Spike (See note 4.)!

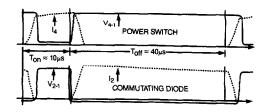

**Positive Output Switching Waveforms**

**Note:** Negative output circuit and waveforms are identical but of opposite polarity  $(V_{in} = -25V, V_{out} = -5V, I_{DRIVE} = +30mA)$ .

Figure 1.

#### 2.0 APPLICABLE DOCUMENTS

The following documents of the issue in effect on the date of invitations for bids, form a part of this specification to the extent specified herein.

MIL-S-19500 — General Specification for Semiconductor Devices

MIL-S-19491 — Preparation for Delivery of Semiconductor Devices

#### 3.0 REQUIREMENTS

#### 3.1 Design and Construction

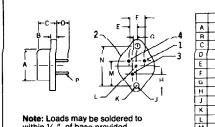

The Hybrid devices supplied under this specification shall have a design and construction such that they will meet all of the requirements specified herein. The dimensions and physical characteristics shall be as specified in Figure 2.

#### 3.2 Performance Characteristics

The performance characteristics of the Hybrid device supplied under this specification shall be as specified in Group A inspection defined in Table 1.

#### 3.3 Quality Assurance

The Quality Assurance Provisions shall be defined in paragraph 4.0.

#### 3.4 Test Methods

Test methods shall be as specified herein.

#### 3.5 Marking

The markings on the devices supplied shall be permanent and legible and shall include the Manufacturer's name or trademark, a Manufacturing Date Code in accordance with MIL-S-19500 and the specific device type number.

#### 3.6 Preparation for Delivery

The Hybrid devices supplied under this specification shall be prepared for delivery in accordance with level C of MIL-S-19491 unless otherwise directed in the specific contract or purchase order.

#### 3.7 Ordering Data

Procurement document should specify the following:

- a. Specific item type number

- b. Number and date of this specification

- c. Quality Assurance Test level required

- d. Any special packaging if required

#### **MECHANICAL SPECIFICATIONS**

Note: Loads may be soldered to within 1/16" of base provided temperature-time exposure is less than 260°C for 10 seconds.

|          | ins.          | mm             |

|----------|---------------|----------------|

| Α        | .875 MAX.     | 22.23 MAX      |

| R        | 136           | 3.43           |

| C        | 250450        | 6.35-11.43     |

| 0 (      | .312 MIN.     | 7.92 MIN.      |

| E        | 205-225       | 5.21-5.72      |

| F        | .420440       | 10.67-11.18    |

| <u> </u> | .145165       | 3.68-4.19      |

| нΤ       | 395405        | 10.03-10.29    |

| J        | .151161 DIA   | 3.84-4.09 DIA. |

| ĸ        | 188 MAX. RAD. | 4.78 MAX. RAD  |

| ı        | 525 MAX. RAD. | 13.34 MAX. RAD |

| м        | .708728       | 17.98-18.49    |

| N        | 1.177-1.197   | 29.90-30.40    |

| Р        | .038043 DIA.  | 97-1.09 DIA    |

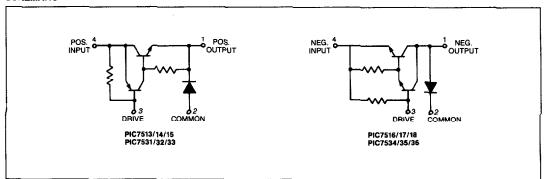

### SCHEMATIC

Figure 2. Physical Dimensions and Biasing Diagrams

#### 4.0 QUALITY ASSURANCE PROVISIONS

#### 4.1 General Provisions

- 4.1.1 Inspection Responsibility The supplier is responsible for the performance of all inspection requirements and acceptability of results as specified herein for the Test Level identified in the contract or purchase order.

- 4.1.2 Controlled Manufacture The devices supplied under this specification shall be manufactured under controlled conditions using formally defined quality assurance methods and systems.

- 4.1.3 Manufacturing Traceability Each device supplied under this specification shall be traceable to a specific process group, to permit tracing of its full manufacturing history. Process group records shall indicate the exact date that each manufacturing operation was performed and identify materials and process procedures which were used. The manufacturer shall keep these records on file for at least five years.

#### 4.1.4 Definitions

- 4.1.4.1 Inspection Lot An "inspection lot" is a collection of devices from which a sample is withdrawn and inspected to determine compliance with the acceptability criterion. It shall consist of one or more "inspection sublots" of the device types defined in this specification. The maximum inspection lot size shall be 5000 units.

- 4.1.4.2 Inspection Sublot An "inspection sublot" snall consist of a collection of devices of a single type which have been manufactured under the same conditions and with the same materials

- 4.1.4.3 Shipment Lot A "shipment lot" shall consist of devices taken from an accepted inspection lot for the purpose of shipment on a specific contract or order.

- 4.1.4.4 Group A Inspection Group A inspection shall consist of the examinations and tests specified in Table I, and shall be performed on a sublot basis.

- 4.1.4.5 Controlled Inventory The controlled inventory shall consist of lots which have successfully passed the acceptance inspection and are being held in storage prior to actual shipment. A controlled inventory shall have adequate safeguards to insure that no defective or untested devices can be included in it. It shall be accessible only to those individuals who are formally identified as authorized personnel.

#### 4.2 Acceptance Inspection

The acceptance inspection requirements shall be as defined by the applicable test level. The procedures of MIL-S-19500 shall apply to Group A Inspection. Inspection lots which have been inspected and accepted shall be kept in a controlled inventory. Shipment lots shall be formed using devices taken from accepted inspection lots.

- **4.2.1 Test Level T2 Requirements** Test level T2 shall consist of the following requirements.

- 4.2.1.1 The supplier shall perform the Parameter Stability Testing defined in paragraph 4.3 on each device to be supplied. Prior to starting the Blocking Stability test defined in paragraph 4.36, each device shall be sorialized for individual identity. Variables test data for the controlled electrical parameters shall be recorded before and after stressing. The same procedure shall apply for the Power Stress stability test defined in paragraph 4.38.

- 4.2.1.2 The supplier shall perform the Group A inspections in accordance with the defined LTPD requirements on each inspection sublot. Electrical parameter testing as specified shall be performed by variables with test data recorded.

- 4.2.1.3 With each shipment lot, the supplier shall provide a Certificate of Compliance to test level T2 of this specification.

- **4.2.2 Test Level T1 Requirements** Test level T1 shall consist of the following requirements.

- 4.2.2.1 The supplier shall perform the Parameter Stability Testing defined in paragraph 4.3 on each device to be supplied. Electrical parameter testing as specified shall be performed by attributes

- 4.2.2.2 The supplier shall perform the Group A inspections in accordance with the defined LTPD requirements on each inspection sublot. Electrical parameter testing as specified shall be performed by attributes with test data recorded.

- 4.2.2.3 The supplier shall provide a Certificate of Compliance to test level T1 of this specification with each shipment lot.

#### 4.3 Parameter Stability Tests

Each Hybrid device is to be supplied under this specification and shall receive the following tests in addition to other standard testing performed by the manufacturer.

- **4.3.1 Temperature Storage** Each Hybrid device shall be subjected, in a non-operating state, to a temperature of 150°C for a minimum period of 48 hours.

- **4.3.2 Temperature Cycling** Each Hybrid device shall be temperature cycled from  $-55^{\circ}$ C to  $150^{\circ}$ C for a minimum of 10 cycles. Each cycle shall consist of at least 15 minutes at each temperature extreme with a maximum transition time of 5 minutes between each temperature extreme.

- 4.3.3 Hermetic Seal Test Fine Leak Each Hybrid device shall be tested for a case leakage rate of 1 × 10°s cc/sec or smaller using a helium mass spectrometer or equivalent method. Devices with a case leakage rate greater than specified shall be removed from the lot.

- **4.3.4** Hermetic Seal Test Gross Leak Each Hybrid device shall be tested for gross leaks using fluorocarbon gross leak test or equivalent method. Devices with any indication of case leakage shall be removed from the lot.

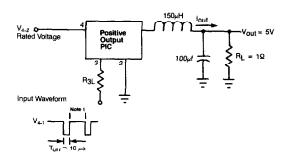

#### 4.3.5 Reverse Bias Clamp Inductive Test -

$V_{4-2}$  = Rated Input Voltage  $I_4$  = 5A., f = 25 kHz, E<sub>out</sub> = 5V

$T_C = 25$ °C, see Figure 4

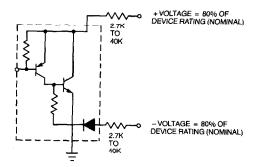

**4.3.6 High Temperature Reverse Bias** — Each Hybrid device will be high temperature reversed biased in the circuit shown in Figure 3. The conditions of this test are as follows:

$$T_A=+125^{\circ}C$$

Time = 16 hours  $^{+8}_{-0}$  hours

Circuit and voltages as shown in Figure 3 for the appropriate device.

Figure 3. High Temperature Reverse Bias Circuit

**4.3.7** The following measurements will be made before and after the high temperature reverse bías test. The unit measurements shall be recorded or the devices will be celled in order to compare and guarantee the delta (Δ) requirements depending on the test level the lot is being prepared to.

Note 1: Adjust Toff to obtain specified lout-

Note 2: Negative output test circuits and waveforms are identical but of opposite polarity.

Note 3:  $R_{3L}=2K\Omega$  for the PIC 7513/16/31/34  $R_{3L}=2.7K\Omega$  for the PIC 7514/17/32/35  $R_{3L}=3.3K\Omega$  for the PIC 7515/18/33/36

Figure 4. Reverse Bias Clamp Inductive Test Circuit

| Type Number            | Test<br>1.1a | Maximum<br>Readings<br>Initial<br>& Final | Delta<br>Change  | Symbol                |

|------------------------|--------------|-------------------------------------------|------------------|-----------------------|

| PIC7513/14/15/31/32/33 | 8            | 1.5V                                      | ± 0.3V           | V <sub>4-1 (on)</sub> |

| PIC7516/17/18/34/35/36 | 8            | - 1.5V                                    | ±0.3V            | V <sub>4-1</sub> (on) |

| PIC7513/14/15/31/32/33 | 10           | 1.25V                                     | +0.3V            | V <sub>2-1 (on)</sub> |

| PIC7516/17/18/34/35/36 | . 10         | -1.25V                                    | ± 0.3V           | V <sub>2-1 (on)</sub> |

| PIC7513/14/15/31/32/33 | 12           | 10μA                                      | ± 1.0 or ± 100%1 | l <sub>4-1</sub>      |

| PIC7516/17/18/34/35/36 | 12           | – 10μA                                    | ± 1.0 or ± 100%1 | I <sub>4-1</sub>      |

| PIC7513/14/15/31/32/33 | 14           | 10μΛ                                      | ± 2.0 or ± 100%1 | I <sub>1-2</sub>      |

| PIC7516/17/18/34/35/36 | 14           | 10μΑ                                      | ± 2.0 or ± 100%1 | l <sub>1-2</sub>      |

Whichever is greater.

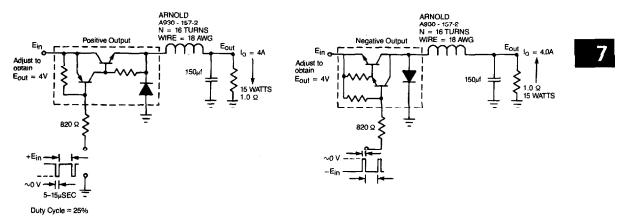

**4.3.8 Power Stress** — Each Hybrid device shall be burned-in using the circuit shown in Figure 5. The conditions are as follows:

$T_A = +25$ °C

Time = 40 hours minimum

Circuit and conditions as shown in Figure 5.

# **4.3.9** The readings before and after burn-in shall be as specified in paragraph 4.3.7.

Figure 5. Burn in Circuite

Table I. Group A Inspection

| Examination or Test                                                                                                                         | Symbol                                                                                                                           | Electrical<br>Spec Test<br>Number | Sample<br>Size<br>(LTPD) | Max.<br>Acc.<br>No. |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|---------------------|

| Subgroup 1<br>Visual and Mechanical                                                                                                         | _                                                                                                                                | _                                 | 22<br>(10)               | 0                   |

| Subgroup 2 25°C Tests On-State Voltage On-State Voltage Diode Forward Voltage Diode Forward Voltage Off-State Current Diode Reverse Current | V <sub>4-1</sub> on<br>V <sub>4-1</sub> on<br>V <sub>2-1</sub> on<br>V <sub>2-1</sub> on<br>I <sub>4-1</sub><br>I <sub>1-2</sub> | 8<br>9<br>10<br>11<br>12          | 45<br>(5)                | 0                   |

| Subgroup 3 T <sub>A</sub> = +100°C Tests<br>Off-State Current<br>Off-State Current                                                          | I <sub>4-1</sub>                                                                                                                 | 13<br>15                          | 45<br>(5)                | 0                   |

| Subgroup 4 25°C Tests Current Delay Time Current Rise Time Voltage Rise Time Voltage Fall Time Current Fall Time                            | t <sub>dl</sub><br>t <sub>rl</sub><br>t <sub>rv</sub><br>t <sub>fv</sub>                                                         | 1<br>2<br>3<br>5<br>6             | 45<br>(5)                | 0                   |