# **User Manual**

# **AIMB-215 B1**

Intel® Celeron J1900/N2930/ N2807 Mini-ITX with VGA/LVDS/ DP++ (eDP), 6 COM, Dual LAN, 8 USB, 2 Mini-PCle, and PCle x1

# Copyright

The documentation and the software included with this product are copyrighted 2016 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to improve the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without prior written permission from Advantech Co., Ltd. The information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

# **Acknowledgements**

IBM and PC are trademarks of International Business Machines Corporation.

Intel<sup>®</sup> Celeron™ J1900/N2930/N2807 is trademark of Intel Corporation WinBond is a trademark of Winbond Corporation.

All other product names or trademarks are the property of their respective owners.

Part No. 2006021542 Printed in China Edition 3 July 2016

## **Message to the Customer**

#### **Advantech Customer Services**

Every Advantech product is built with the most exact specifications to ensure reliable performance in the harsh and demanding conditions typical of industrial environments. Whether your new Advantech equipment is destined for a laboratory or factory floor, be assured that your product can provide the reliability and ease of operation for which the name Advantech is renowned.

Your satisfaction is our primary concern. A guide to Advantech's customer services is provided below. To ensure that you receive the full benefit of our services, please follow the instructions below.

#### **Technical Support**

We want you to get the maximum performance from your products. Should you encounter any technical difficulties, we are available to provide assistance. Answers to the most frequently asked questions are provided in the product documentation. These answers are typically a lot more detailed than the ones provided over the phone.

So please consult this manual first. If you still cannot find the answer, gather all relevant information or questions that apply to your problem, and with the product close to hand, call your dealer. Our dealers are well trained and ready to provide the support required for you to experience the most from your Advantech products. Most of the problems reported are minor and can be easily solved over the phone.

In addition, free technical support from Advantech engineers is available every business day. We are always willing to give advice on application requirements or specific information regarding the installation and operation of any of our products.

# **Declaration of Conformity**

#### **FCC Class B**

This device complies with the requirements in Part 15 of the FCC regulations: Operation is subject to the following two conditions:

- This device may not cause harmful interference.

- This device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Regulations. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this device in a residential area is likely to cause harmful interference, in which case users are required to correct the interference at their own expense. The user is advised that any equipment changes or modifications not expressly approved by the party responsible for compliance would void compliance with the FCC regulations and, therefore, the user's authorization to operate the equipment.

**Caution!** There is a risk of a new battery exploding if incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

# **Memory Compatibility**

### **AIMB-215 B1 Memory Compatibility List**

| Brand          | Size | Speed        | Туре           | ECC | Vendor PN      | Memory                                 | Advantech PN             | Result |

|----------------|------|--------------|----------------|-----|----------------|----------------------------------------|--------------------------|--------|

| Tran-<br>scend | 2GB  | DDR3<br>1333 | SODIMM<br>DDR3 | N   | TS256MSK64W3N  | SEC 234 HYK0<br>K4B2G0846D             |                          | PASS   |

| Apacer         | 4GB  | DDR3<br>1333 | SODIMM<br>DDR3 | N   | 78.B2GCY.AT00C | MICRON2XE22D9QBJ<br>MICRON 4JE77 D9QBJ | 96SD3L-<br>4G1333NN-AP   | PASS   |

| Apacer         | 2GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | 78.A2GCR.AT00C | MICRON IYM22 D9PFJ<br>(256x8)          |                          | PASS   |

| Apacer         | 4GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | 78.B2GCR.AF10C | HYNIX H5TC2G83EFR                      |                          | PASS   |

| Apacer         | 4GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | 78.B2GCZ.AT00C | MICRON 2QE22<br>D9QBJ                  |                          | PASS   |

| Tran-<br>scend | 4GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | TS512MSK64W6H  | SEC 231 HYK0<br>K4B4G0846B             | 96SD3L-<br>4G1600NN-TR   | PASS   |

| AQD            | 4GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | 653555-0007    | SEC 316 XYK0<br>K4B4G0846B             | AQD-<br>SD3L4GN16-SG     | PASS   |

| AQD            | 2GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | 665205-0397    | SEC 310 XYKO<br>K4B2G084GD             | AQD-<br>SD3L2GN16-SQ     | PASS   |

| AQD            | 2GB  | DDR3<br>1600 | SODIMM<br>DDR3 | N   | 201403504691   | HYNIX H5TC2G83EFR                      | AQD-<br>SD3L2GN16-<br>HQ | PASS   |

# **Ordering Information**

| P/N                                          | CPU   |   | DP++/<br>eDP | CRT | LVDS | GbE<br>LAN | сом | SATA<br>II | USB3.0/<br>2.0 | MiniPCle                                                    | TPM | AMP         | PClex1                             | Thermal solution |

|----------------------------------------------|-------|---|--------------|-----|------|------------|-----|------------|----------------|-------------------------------------------------------------|-----|-------------|------------------------------------|------------------|

| AIMB-215D-<br>S6B1E                          | J1900 | 2 | 1 /(1)       | 1   | 1    | 2          | 6   | 2          |                | 2 (1 x F/S; 1<br>x H/S); H/S<br>miniPCle<br>colay<br>PClex1 | (1) | (2 x<br>6W) | 1; PClex1<br>colay H/S<br>miniPCle | Passive          |

| AIMB-215N-<br>S6B1E                          | N2930 | 2 | 1 /(1)       | 1   | 1    | 2          | 6   | 2          |                | 2 (1 x F/S; 1<br>x H/S); H/S<br>miniPCle<br>colay<br>PClex1 | (1) | (2 x<br>6W) | 1; PClex1<br>colay H/S<br>miniPCle | Passive          |

| AIMB-215U-<br>S6B1E (w/o<br>SUSI-<br>Access) | N2807 | 1 | 1 /(1)       | 1   | 0    | 1          | 2   | 1          | 1/3            | 1 x F/S                                                     | (1) | (2 x<br>6W) | 1                                  | Passive          |

| AIMB-215L-<br>S6B1E (w/o<br>SUSI-<br>Access) | J1900 | 2 | 1 /(1)       | 1   | 0    | 1          | 2   | 1          | 1/3            | 1 x F/S                                                     | (1) | (2 x<br>6W) | 1                                  | Passive          |

<sup>\* ( )</sup> is not populated when MP

## **Product Warranty (2 years)**

Advantech warrants the original purchaser that its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products that have been repaired or altered by persons other than repair personnel authorized by Advantech, or products that have been subject to misuse, abuse, accident, or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, users will be billed according to the cost of replacement materials, service time, and freight. Please consult your dealer for more details.

If you believe your product is defective, please follow the steps listed below.

- 1. Collect all information about the problem encountered (for example, CPU speed, Advantech products used, other hardware and software used, etc.). Note anything abnormal and list any onscreen messages encountered when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any relevant information readily available.

- If your product is diagnosed as defective, obtain a return merchandise authorization (RMA) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a completed Repair and Replacement Order Card, and proof of the purchase date (such as a photocopy of your sales receipt) in a shippable container. Products returned without a proof of purchase date are not eligible for our warranty service.

- 5. Write the RMA number clearly on the outside of the package and ship the product prepaid to your dealer.

## **Initial Inspection**

Before installing the motherboard, please ensure that the following items are included in your shipment:

- 1x AIMB-215 B1 Intel® Celeron™ J1900/N2930/N2807 Mini-ITX motherboard

- 1 x SATA HDD cable

- 1 x SATA power cable

- 1 x Serial port cable (1 to 4), for AIMB-215 B1 D/N SKU only

- 2 x Serial port cable (1 to 1)

- 1 x I/O port bracket

- 1 x startup manual

- 1 x driver CD

- 1 x warranty card

- 1 x on-board CPU heat sink

If any of these items are missing or damaged, contact your distributor or sales representative immediately. All AIMB-215 B1 devices are mechanically and electrically inspected before shipment. Thus, your product should be free of marks and scratches and in perfect working order upon receipt. While unpacking AIMB-215 B1, check the product for signs of shipping damage (for example, a damaged box, scratches, dents, etc.). If the device is damaged or fails to meet the specifications, notify our service department or your local sales representative immediately. Please also notify the carrier. Retain the shipping carton and packing material for inspection by the carrier. After this inspection, we will make arrangements to repair or replace the unit.

# **Contents**

| Chapter | 1          | General Information1                                                                            |

|---------|------------|-------------------------------------------------------------------------------------------------|

|         | 1.1<br>1.2 | Introduction                                                                                    |

|         | 1.2        | OS and BIOS Compatibility 2                                                                     |

|         | 1.4        | Specifications                                                                                  |

|         | 1.7        | 1.4.1 System                                                                                    |

|         |            | 1.4.2 Memory                                                                                    |

|         |            | 1.4.3 Input/Output                                                                              |

|         |            | 1.4.4 Graphics                                                                                  |

|         |            | 1.4.5 Ethernet LAN                                                                              |

|         |            | 1.4.6 Industrial Features4                                                                      |

|         |            | 1.4.7 Mechanical and Environmental Specifications4                                              |

|         | 1.5        | Jumpers and Connectors4                                                                         |

|         |            | Table 1.1: Connector/Header List4                                                               |

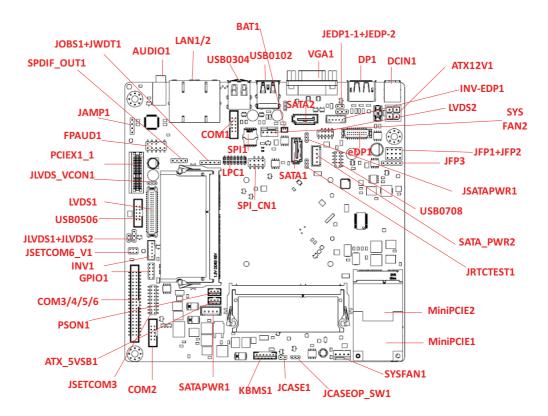

|         | 1.6        | Board Layout: Jumper and Connector Locations                                                    |

|         |            | Figure 1.1 Jumper and Connector Locations6                                                      |

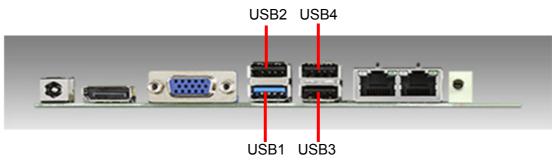

|         |            | Figure 1.2 I/O Connectors6                                                                      |

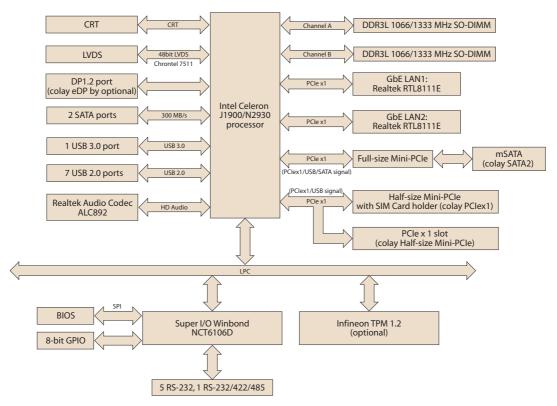

|         | 1.7        | AIMB-215 B1 Board Diagram7                                                                      |

|         |            | Figure 1.3 AIMB-215 B1 Board Diagram7                                                           |

|         | 1.8        | Safety Precautions                                                                              |

|         | 1.9        | Jumper Options                                                                                  |

|         |            | 1.9.1 Setting Jumpers                                                                           |

|         |            | 1.9.2 CMOS Mode Selection (JRTCTEST1)                                                           |

|         |            | Table 1.2: CMOS Mode Selection (JRTCTEST1)                                                      |

|         |            | 1.9.3 COM2 RS-232/422/485 Mode Selector (JSETCOM3)                                              |

|         |            | 10                                                                                              |

|         |            | Table 1.4: COM3 RS-232/422/485 Mode Selector (JSETCOM3).                                        |

|         |            | 10                                                                                              |

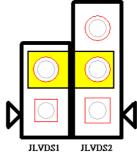

|         |            | 1.9.4 LVDS Panel Voltage Selection (JLVDS1 + JLVDS2)11                                          |

|         |            | Table 1.5: LVDS Panel Voltage Selection (JLVDS1 + JLVDS2)11                                     |

|         |            | 1.9.5 PSON1: ATX and AT Mode Selector11                                                         |

|         |            | Table 1.6: PSON1: ATX and AT Mode Selector11                                                    |

|         |            | 1.9.6 JOBS1 + JWDT1: OBS Beep and Watchdog Timer Output 12                                      |

|         |            | Table 1.7: JOBS1 + JWDT1: OBS Beep and Watchdog Timer                                           |

|         |            | Output12                                                                                        |

|         |            | 1.9.7 Case Open Pin Header Selection (JCASEOP_SW1)12                                            |

|         |            | Table 1.8: Case Open Pin Header Selection (JCASEOP_SW1) 12                                      |

|         |            | 1.9.8 Power Switch/HDD LED/SMBus/Speaker Pin Header (JFP1 +                                     |

|         |            | JFP2)12                                                                                         |

|         |            | Table 1.9: Power Switch/HDD LED/SMBus/Speaker Pin Header (JFP1 + JFP2)                          |

|         |            | <ul><li>1.9.9 EDP Panel Voltage Selection (JEDP1 + JEDP2) (BOM Optional) .</li><li>13</li></ul> |

|         |            | Table 1.10: EDP Panel Voltage Selection (JEDP1 + JEDP2) (optional)13                            |

|         |            | 1.9.10 JEIDA/VESA Selection (JLVDS_VCON1)                                                       |

|         |            | Table 1.11: JEIDA/VESA Selection (JLVDS_VCON1)13                                                |

|         |            | 1.9.11 RS-485/422 Terminal Resistor Jumper (SW_422_1)14                                         |

|         |            | Table 1.12: RS-485/422 Terminal Resistor Jumper (SW_422_1)14                                    |

| Chapter | 2          | Connecting Peripherals15                                                                        |

|         | 2.1<br>2.2 | IntroductionLAN and USB Ports (LAN1/2, USB0102/USB0304/USB0506/USB070 |           |

|---------|------------|-----------------------------------------------------------------------|-----------|

|         |            | 16 Table 2.1: LAN LED Indicators                                      | 16        |

|         | 2.3        | VGA Connector (VGA1)                                                  |           |

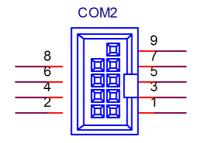

|         | 2.4        | Serial Ports (COM1 ~ COM6)                                            |           |

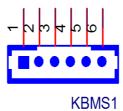

|         | 2.5        | PS/2 Keyboard and Mouse Connector (KBMS1)                             |           |

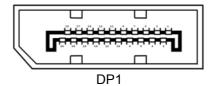

|         | 2.6        | Display Port Connector (DP1)                                          |           |

|         | 2.7        | System FAN Connector (SYSFAN1/2)                                      |           |

|         | 2.8        | Front Panel Connectors (JFP3/JFP1 + JFP2)                             | 20        |

|         |            | 2.8.1 ATX Soft Power Switch (JFP1 + JFP2/PWR_SW)                      | 21        |

|         |            | 2.8.2 Reset (JFP1 + JFP2/RESET)                                       |           |

|         |            | 2.8.3 HDD LED (JFP1 + JFP2/HDDLED)                                    |           |

|         |            | 2.8.4 External Speaker (JFP1 + JFP2/SPEAKER)                          |           |

|         |            | 2.8.5 Power LED and Keyboard Lock Connector (JFP3/PWR_LED a           |           |

|         |            | KEY LOCK)                                                             |           |

|         |            | Table 2.2: ATX Power Supply LED Status (AT power not supp             |           |

|         | 0.0        | ed)                                                                   |           |

|         | 2.9        | Line-Out Connector (AUDIO1)                                           | 22        |

|         | 2.10       | Serial ATA Interface (SATA1/2) & SATADOM Power Pin Header             | 22        |

|         |            | (JSATAPWR1) Table 2.3: SATADOM Power Pin Header (JSATAPWR1)           |           |

|         | 2.11       | PCI-Express x1 Slot (PCIEX1_1)                                        |           |

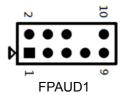

|         | 2.11       | Front Panel Audio Connector (FPAUD1)                                  |           |

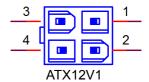

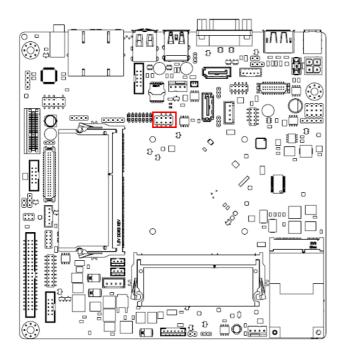

|         | 2.12       | ATX 12V Power Connector (ATX12V1)                                     |           |

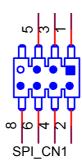

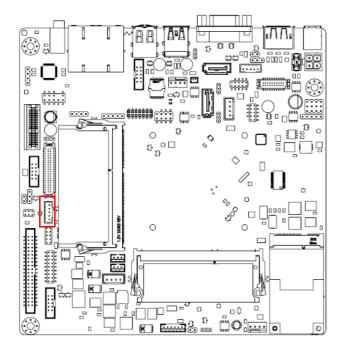

|         | 2.13       | SPI Flash Connector(SPI_CN1)                                          |           |

|         | 2.15       | LVDS Backlight Inverter Power Connector (INV1)                        |           |

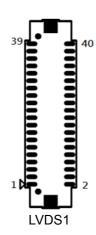

|         | 2.16       | LVDS Connector (LVDS1)                                                |           |

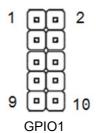

|         | 2.17       | General Purpose I/O Connector (GPIO1)                                 |           |

|         | 2.18       | CMOS Battery Wafer Box (BAT1)                                         |           |

|         | 2.19       | SPI BIOS Socket (SPI1)                                                |           |

|         | 2.20       | SPDIF Interface Pin Header (SPDIF_OUT1)                               |           |

|         | 2.21       | Audio Amplifier Output Pin Header (JAMP1) (BOM Optional)              |           |

|         | 2.22       | ATX Power Supply (5VSB) Connector (ATX_5VSB1)                         |           |

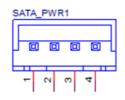

|         | 2.23       | SATA Power Connector (SATA_PWR1/2)                                    | 30        |

|         | 2.24       | Case Open Pin Header (JCASE1)                                         | 30        |

|         | 2.25       | DDR3L SODIMM Socket (DIMMA1/B1)                                       |           |

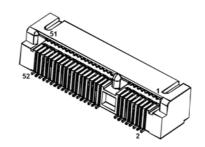

|         | 2.26       | Mini-PCIe and mSATA Connector (MINIPCIE1)                             |           |

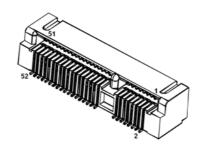

|         | 2.27       | Mini-PCle Connector (MINIPCIE2)                                       |           |

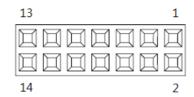

|         | 2.28       | Low Pin Count Interface Header (LPC1)                                 |           |

|         | 2.29       | RTC Reset Pin Header (JRTCTEST1)                                      |           |

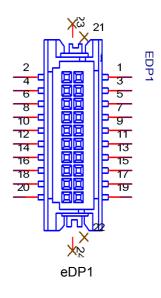

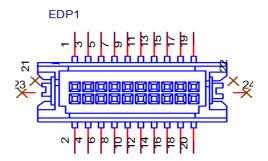

|         | 2.30       | eDP Connector (eDP1) (BOM Optional)                                   |           |

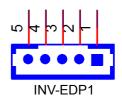

|         | 2.31       | eDP Backlight Inverter Power Connector (INV-EDP1) (BOM Optional)      |           |

|         | 2.32       | SIM Card Holder (SIM2)                                                | 35        |

| Chapter | 2          | PIOS Operation                                                        | 27        |

| Chapter | 3          | BIOS Operation                                                        | <i>31</i> |

|         | 3.1        | Introduction                                                          | 38        |

|         | 3.2        | BIOS Setup                                                            |           |

|         |            | 3.2.1 Main Menu                                                       |           |

|         |            | 3.2.2 Advanced BIOS Features                                          |           |

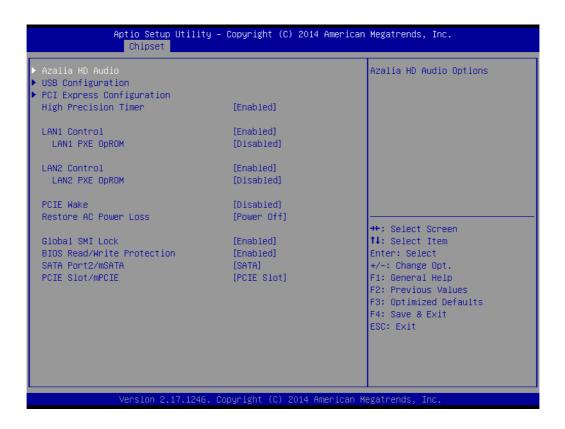

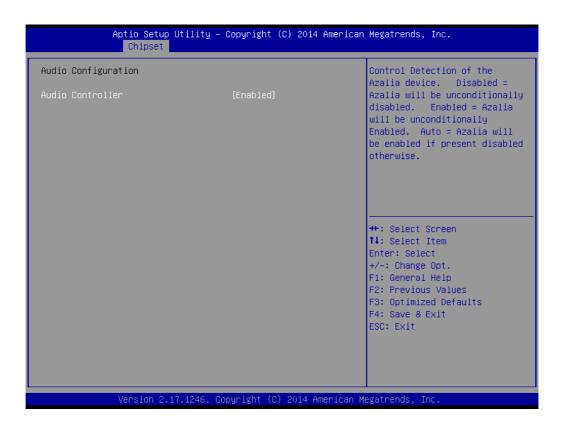

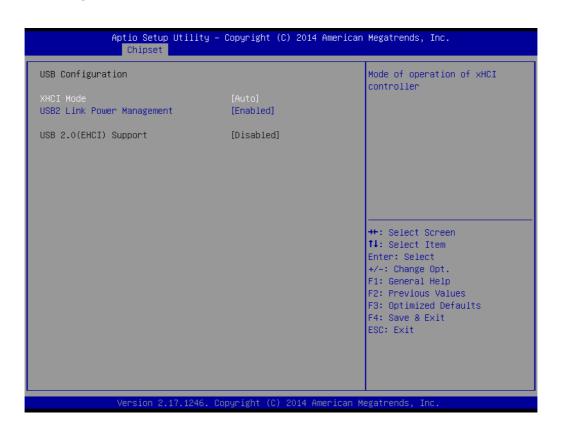

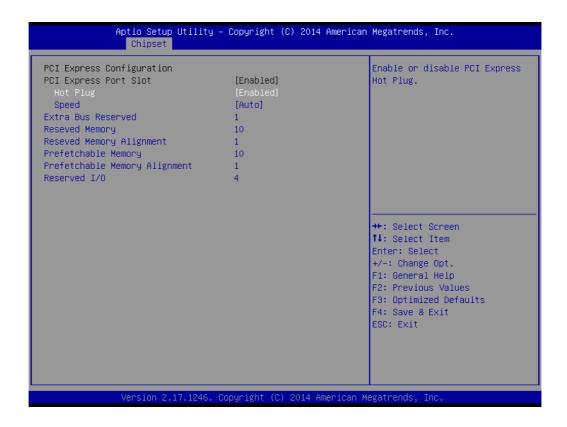

|         |            | 3.2.3 Chipset                                                         | 63        |

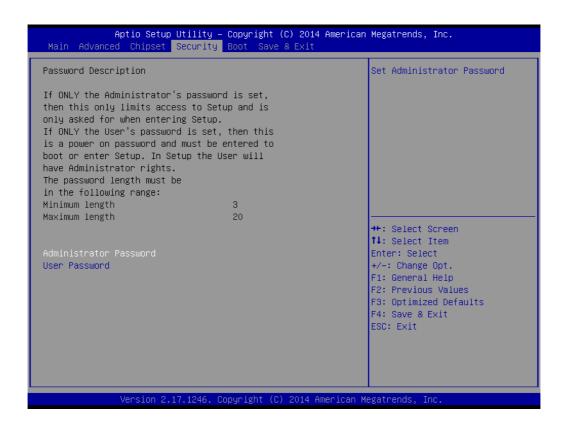

|         |            | 3.2.4 Security                                                        | 71        |

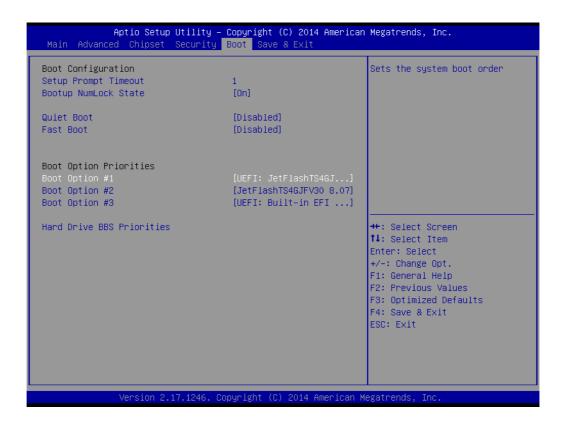

|         |            | 3.2.5 Boot                                                            |           |

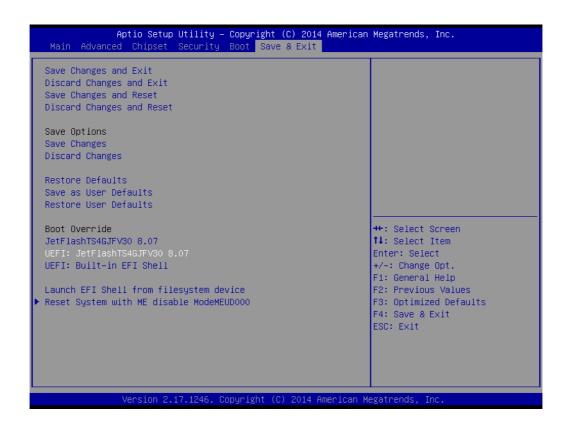

|         |            | 3.2.6 Save and Exit                                                   | 73        |

| Chapter | 4          | Software and Service Introduction                                     | 75        |

|         | 4.1        | Introduction                                                          | 76        |

|         |            |                                                                       |           |

|          | 4.2          | Value-Added Software Services                                                                                                           |                |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

|          |              | 4.2.1 Software API                                                                                                                      |                |

|          |              | 4.2.2 Software Utility                                                                                                                  | 78             |

| Chapter  | 5            | Chipset Software Install Utility                                                                                                        | 79             |

|          | 5.1          | Before Installation                                                                                                                     | 80             |

|          | 5.2          | Introduction                                                                                                                            |                |

| Chapter  | 6            | VGA Setup                                                                                                                               | 81             |

|          | 6.1          | Introduction                                                                                                                            | 82             |

|          | 6.2          | Windows 7/8.1                                                                                                                           | 82             |

| Chapter  | 7            | LAN Configuration                                                                                                                       | 83             |

|          | 7.1          | Introduction                                                                                                                            | 84             |

|          | 7.2          | Features                                                                                                                                | 84             |

|          | 7.3          | Installation                                                                                                                            |                |

|          | 7.4          | Windows 7/8.1 Driver Setup (Realtek 8111E)                                                                                              | 84             |

| Chapter  | 8            | XHCI Driver Installation                                                                                                                | 85             |

|          | 8.1          | Introduction                                                                                                                            | 86             |

|          | 8.2          | Installation                                                                                                                            | 87             |

| Appendix | A.1          | Programming the Watchdog Timer.  Programming the Watchdog Timer.  A.1.1 Watchdog Timer Overview.  A.1.2 Programming the Watchdog Timer. | 90<br>90<br>90 |

|          |              | Table A.1: Watchdog Timer Registers                                                                                                     |                |

| Annondiv | , D          |                                                                                                                                         |                |

| Appendix | K D          | I/O Pin Assignments                                                                                                                     | 91             |

|          | B.1          | DC-IN Adaptor Connector (DCIN1)                                                                                                         |                |

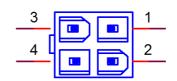

|          | B.2<br>B.3   | Display Port Connector (DP1)eDP Panel Voltage Selection (JEDP-1 + JEDP-2) (BOM Optional)                                                |                |

|          | в.з<br>В.4   | VGA Connector (VGA1)                                                                                                                    |                |

|          | B.5          | Serial ATA Interface Connector (SATA2)                                                                                                  |                |

|          | B.6          | SATADOM Power Pin Header (JSATAPWR1)                                                                                                    | 100            |

|          | B.7          | Serial ATA Interface Connector (SATA1)                                                                                                  |                |

|          | B.8          | CMOS Battery Wafer Box (BAT1)                                                                                                           |                |

|          | B.9          | System Fan Connector (SYSFAN2)                                                                                                          |                |

|          | B.10<br>B.11 | USB3.0 + USB2.0 Stack Connector (USB0102)SPI BIOS Socket (SPI1)                                                                         |                |

|          | B.12         | USB2.0 * 2 Stack Connector (USB0304)                                                                                                    |                |

|          | B.13         | COM1 Box Header (COM1)                                                                                                                  |                |

|          | B.14         | Watchdog Timer Output and OBS Beep (JOBS1 + JWDT1)                                                                                      |                |

|          | B.15         | RJ45 (LAN1 + LAN2) Connector (LAN12)                                                                                                    |                |

|          | B.16         | SPDIF Interface Pin Header (SPDIF_OUT1)                                                                                                 |                |

|          | B.17         | HD Analog Audio Interface (AUDIO1)                                                                                                      |                |

|          | B.18         | Front Panel Audio Pin Header (FPAUD1)                                                                                                   |                |

|          | B.19         | Audio Amplifier Output Pin Header (JAMP1) (BOM Optional)                                                                                | 105            |

| B.20 | LVDS VESA and JEIDA Format Pin Header                           | . 106 |

|------|-----------------------------------------------------------------|-------|

| B.21 | LVDS Panel Connector (LVDS1)                                    |       |

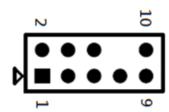

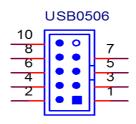

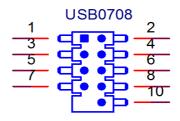

| B.22 | Dual-Port USB2.0 Box Header (USB0506)                           | . 107 |

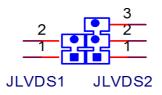

| B.23 | LVDS Panel Voltage Selection (JLVDS1 + JLVDS2)                  |       |

| B.24 | COM6 RI# Selection Pin Header (JSETCOM6_V1)                     | . 108 |

| B.25 | LVDS Backlight Inverter Power Connector (INV1)                  | . 108 |

| B.26 | 8-bit General Purpose I/O Pin Header (GPIO1)                    | 108   |

| B.27 | COM3 ~ COM6 Box Header (COM3456)                                | . 109 |

| B.28 | AT/ATX Mode Selection (PSON1)                                   | 110   |

| B.29 | ATX Power Supply(5VSB) Connector (ATX_5VSB1)                    | 110   |

| B.30 | COM3 RS232, RS422, and RS485 Selection Pin Header (JSETCOM      | l3)   |

|      | 111                                                             |       |

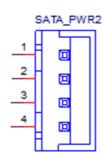

| B.31 | SATA Power Connector (SATA_PWR1)                                | 111   |

| B.32 | COM2 Pin Header (COM2)                                          |       |

| B.33 | System Fan Connector (SYSFAN1)                                  | . 112 |

| B.34 | Case Open Selection Pin Header (JCASEOP_SW1)                    | 112   |

| B.35 | Case Open Pin Header (JCASE1)                                   | 113   |

| B.36 | PS/2 Keyboard and PS/2 Mouse Connector (KBMS1)                  | . 113 |

| B.37 | Mini-PCIe Connector (MINIPCIE2)                                 | 114   |

| B.38 | Mini-PCIe and mSATA Connector (MINIPCIE1)                       |       |

| B.39 | Low Pin Count Interface Header (LPC1)                           | . 116 |

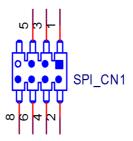

| B.40 | BIOS Flash Pin Header (SPI_CN1)                                 | 117   |

| B.41 | RTC Reset Pin Header (JRTCTEST1)                                | 117   |

| B.42 | SATA Power Connector (SATA_PWR2)                                |       |

| B.43 | Dual-Port USB2.0 Pin Header (USB0708)                           | . 118 |

| B.44 | eDP Connector (eDP1) (BOM Optional)                             |       |

| B.45 | Power LED and Keyboard Lock Pin Header (JFP3)                   |       |

| B.46 | Power Switch/HDD LED/SMBus/Speaker Pin Header (JFP1 + JFP2)     |       |

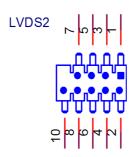

| B.47 | LVDS2 Control Signal Pin Header (LVDS2) (BOM Optional)          | . 119 |

| B.48 | eDP Backlight Inverter Power Connector (INV-EDP1) (BOM Optional | 120   |

| B.49 | ATX 12 V Power Supply Connector (ATX12V1)                       | . 120 |

| B.50 | SIM Card Holder (SIM2)                                          |       |

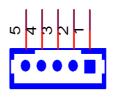

| B.51 | RS-485/422 Terminal Resistor Jumper (SW_422_1)                  | . 121 |

Chapter

**General Information**

### 1.1 Introduction

The AIMB-215 B1 with Intel® Celeron™ J1900/N2930/N2807 processor is designed for industrial applications that require enhanced computing performance and power management capabilities. The motherboard features an onboard Intel® Celeron™ J1900/N2930/N2807 quad-core 2.0/1.83 and dual-core 1.58 GHz CPU with DDR3L 1333MHz of up to 8 GB.

The AIMB-215 B1 offers rich I/O connectivity with one USB 3.0 and nine USB 2.0 ports, as well as six COM ports integrated in a standard 170 x 170 mm form factor. The system also supports dual display for LVDS, DP++ and VGA. AIMB-215 B1 also features numerous connectivity and expansion options, including PCIe x1, 8-bit GPIO, two SATA II 3GB/s connectors, an optional TPM security feature, and two Mini-PCIe expansion slots for easy integration. A dual Intel® chipset and 10/100/1000 Mbps Ethernet port are also provided to deliver high-speed networking.

AIMB-215 B1 is powered by the newest Intel® Celeron™ processor, which is built on 22nm process technology. The thermal design power rating for the Intel N2807 dual-core architecture is only 4.3 W, and that for the quad-core N2930/J1900 design is only 7.5 W/10 W, allowing additional power reductions, system compressions, and performance improvements to be implemented in the future. All the features described above are incorporated into a space-saving, power-efficient, and cost-effective Mini-ITX form factor.

#### 1.2 Features

- Supports Intel® Celeron™ J1900, N2930, and N2807 processors

- Two 204-pin SODIMM, up to 8 GB DDR3L, and 1333 MHz SDRAM

- Supports 1 PCle x1 and two Mini-PCle expansion ports, six serial ports, 8 USB ports, and two SATA II ports

- Lower total ownership costs with DC12-V functionality; supports 24-bit dualchannel LVDS

- Onboard TPM 1.2 support (optional)

- Supports a dual-channel 6 W amplifier (optional)

- Supports embedded software APIs and utilities

### 1.3 OS and BIOS Compatibility

The AIMB-215 B1 BIOS supports OS in legacy mode for 32 and 64 bit, and supports OS in UEFI mode for 64-bit.

# 1.4 Specifications

# 1.4.1 **System**

- **CPU**: Intel® Celeron<sup>™</sup> J1900/N2930/N2807

- **BIOS**: SPI 16-Mbit BIOS

- SATA hard disk drive interface: Two onboard SATA connectors with a data transmission rate of up to 300 MB

Note!

mSATA support is only available when SATA 2 is not in use; mSATA and SATA2 cannot be used concurrently.

### **1.4.2 Memory**

■ RAM: Up to 8 GB in two-slot 204-pin SODIMM sockets. Supports dual-channel DDR3L (low voltage) SODIMM 1.35 V modules of up to 1333 MHz

Note!

AIMB-215 B1 supports 1.35 V memory only. Users must install the memory modules on the DIMMA 1 socket first.

#### 1.4.3 Input/Output

- PCI bus: One PCIe x1 slot, one full size MiniPCIe and one half size MiniPCIe socket

- Serial ports: Six serial ports; COM3 comprises RS-232/422/485 and five RS-232 serial ports

- **Keyboard and PS/2 mouse connector:** Supports one standard PS/2 keyboard and one standard PS/2 mouse (onboard six-pin wafer box)

- **USB port:** Supports one USB 3.0 port with a transmission rate of up to 5Gbps and seven USB 2.0 ports with transmission rates of up to 480 Mbps

- **GPIO connector:** One 8-bit general purpose input/output

Note!

Half size MiniPCle support is only available when PCle x1 is not in use; Half size MiniPCle and PCle x1 cannot be used concurrently.

#### 1.4.4 Graphics

- Controller: Embedded Gen7, Gfx frequency 688/313/313 MHz for J1900 / N2930/N2807

- **Display memory**: Dynamically shared system memory of up to 224 MB

- VGA: Supports a display resolution of up to 2560 x 1600 @ 60 Hz

- LVDS: Supports a display resolution of up to 1920 x 1200 @ 60 Hz

- **DisplayPort 1.2:** Supports up to 2560 x 1600 @ 60 Hz

#### 1.4.5 Ethernet LAN

- Supports dual 10/100/1000 Mbps Ethernet port (s) via PCI Express x1 bus, which provides a data transmission rate of 500 MB/s

- Controller: LAN1: Realtek 8111E; LAN2: Realtek 8111E

#### 1.4.6 Industrial Features

■ **Watchdog timer:** Can generate a system reset. The watchdog timer is programmable, with each unit equal to one second or one minute (255 levels)

#### 1.4.7 Mechanical and Environmental Specifications

■ Operating temperature: 0 ~ 60 °C (32 ~ 140 °F, depending on the CPU)

■ Storage temperature: -40 ~ 85 °C (-40 ~ 185 °F)

■ **Humidity:** 5 ~ 95% non-condensing

Power supply voltage: +12 V

■ Power consumption:+12 V @ 2.03 A (Intel J1900 2.0 GHz processor/DDR3L

1333 MHz 4 GB x 2)

■ Board size: 170 x 170 mm (6.69 x 6.69")

■ Board weight: 0.365 kg

## 1.5 Jumpers and Connectors

The AIMB-215 B1 motherboard is equipped with connectors for linking the board to external devices such as hard disk drives and a keyboard. The board also features several jumpers for configuring the system according to specific applications.

The function of each board jumper and connector is listed in the table below. The procedure for setting jumpers is explained in subsequent sections of this chapter. Instructions for connecting external devices to the motherboard are provided in Chapter 2.

| Table 1.1 | : Connector/Header List                      |                |

|-----------|----------------------------------------------|----------------|

|           | Description                                  | Part Reference |

| 1         | DC-IN adaptor connector                      | DCIN1          |

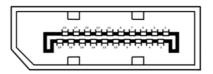

| 2         | Display Port connector                       | DP1            |

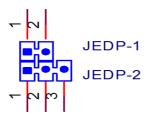

| 3         | eDP panel voltage selection                  | JEDP-1+JEDP-2  |

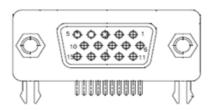

| 4         | VGA connector                                | VGA1           |

| 5         | Serial ATA interface connector               | SATA2          |

| 6         | SATADOM power pin header                     | JSATAPWR1      |

| 7         | Serial ATA interface connector               | SATA1          |

| 8         | CMOS battery wafer box                       | BAT1           |

| 9         | System fan connector                         | SYSFAN2        |

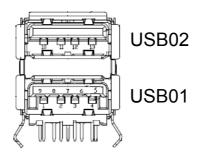

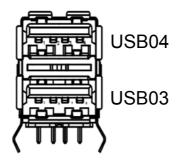

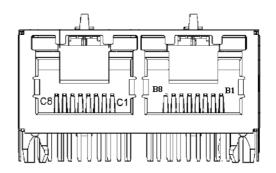

| 10        | USB 3.0 + USB 2.0 stack connector            | USB0102        |

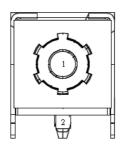

| 11        | SPI BIOS socket                              | SPI1           |

| 12        | USB 2.0 * 2 stack connector                  | USB0304        |

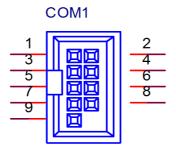

| 13        | COM1 box header                              | COM1           |

| 14        | Watchdog timer output and OBS beep           | JOBS1+JWDT1    |

| 15        | RJ45(LAN 1+ LAN 2) connector                 | LAN12          |

| 16        | SPDIF interface pin header                   | SPDIF_OUT1     |

| 17        | HD analog audio interface                    | AUDIO1         |

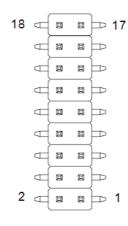

| 18        | Front-panel audio pin header                 | FPAUD1         |

| 19        | Audio amplifier output pin header            | JAMP1          |

| 20        | PCI-Express x1 slot                          | PCIEX1_1       |

| 21        | LVDS VESA, JEIDA format selection pin header | JLVDS_VCON1    |

| <b>Table 1.1: C</b> | onnector/Header List                          |                                       |

|---------------------|-----------------------------------------------|---------------------------------------|

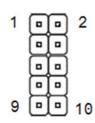

| 22                  | LVDS panel connector                          | LVDS1                                 |

| 23                  | Dual-port USB2.0 pin header                   | USB0506                               |

| 24                  | DDR3L SODIMM socket                           | DIMMB1                                |

| 25                  | LVDS panel voltage selection                  | JLVDS1+JLVDS2                         |

| 26                  | COM6 RI# selection pin header                 | JSETCOM6_V1                           |

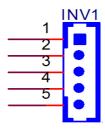

| 27                  | LVDS backlight inverter power connector       | INV1                                  |

| 28                  | 8-bit general purpose I/O pin header          | GPIO1                                 |

| 29                  | COM 3 ~ COM 6 box header                      | COM3456                               |

| 30                  | AT/ATX mode selection                         | PSON1                                 |

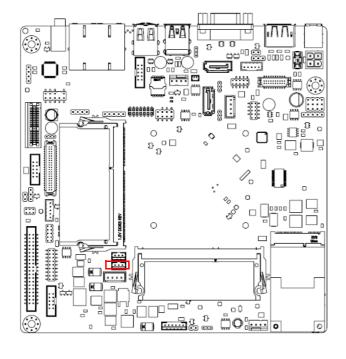

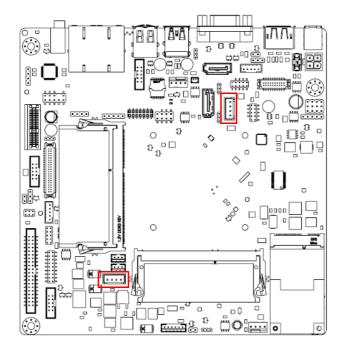

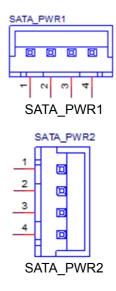

| 31                  | ATX power supply (5VSB) connector             | ATX_5VSB1                             |

| 32                  | COM3 RS232,RS422,RS485 selection pin header   | JSETCOM3                              |

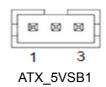

| 33                  | SATA power connector                          | SATA_PWR1                             |

| 34                  | COM2 box header                               | COM2                                  |

| 35                  | System fan connector                          | SYSFAN1                               |

| 36                  | Case open selection pin header                | JCASEOP_SW1                           |

| 37                  | Case open pin header                          | JCASE1                                |

| 38                  | PS/2 keyboard and PS/2 mouse connector        | KBMS1                                 |

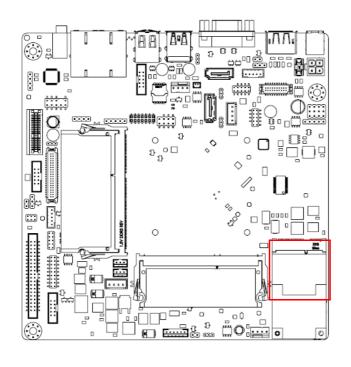

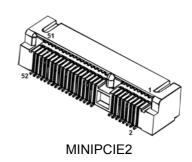

| 39                  | Mini-PCle connector                           | MINIPCIE2                             |

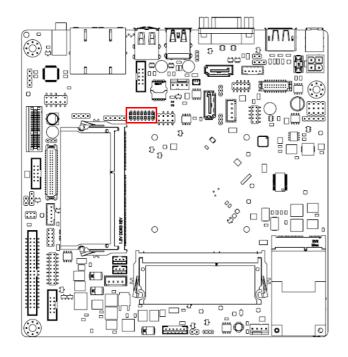

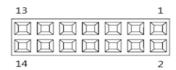

| 40                  | Mini-PCIe, mSATA connector                    | MINIPCIE1                             |

| 41                  | DDR3L SODIMM socket                           | DIMMA1                                |

| 42                  | Low pin count interface header                | LPC1                                  |

| 43                  | BIOS flash pin header                         | SPI_CN1                               |

| 44                  | RTC reset pin header                          | JRTCTEST1                             |

| 45                  | SATA power connector                          | SATA_PWR2                             |

| 46                  | Dual-port USB2.0 pin header                   | USB0708                               |

| 47                  | eDP connector                                 | eDP1                                  |

| 48                  | Power LED and keyboard lock pin header        | JFP3                                  |

| 49                  | Power switch/HDD LED/SMBus/Speaker pin header | JFP1+JFP2                             |

| 50                  | LVDS2 control signal pin header               | LVDS2                                 |

| 51                  | eDP backlight inverter power connector        | INV-EDP1                              |

| 52                  | ATX 12-V power supply connector               | ATX12V1                               |

| 53                  | SIM card holder                               | SIM2                                  |

| 54                  | RS-485/422 terminal resistor jumper           | SW_422_1                              |

|                     | -                                             | · · · · · · · · · · · · · · · · · · · |

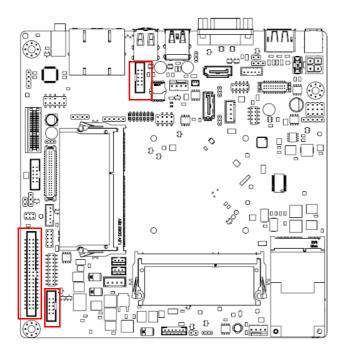

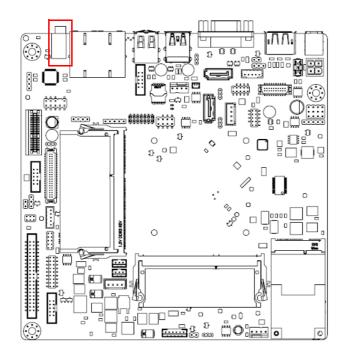

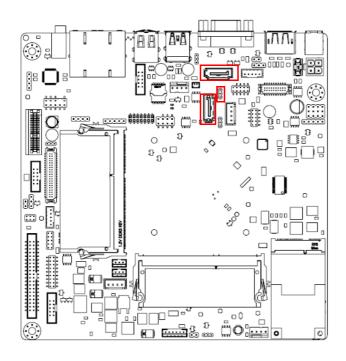

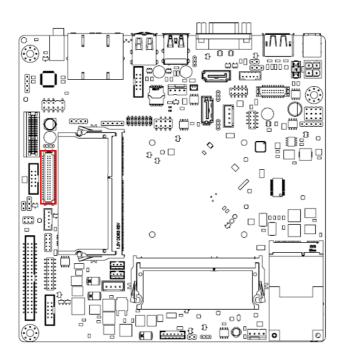

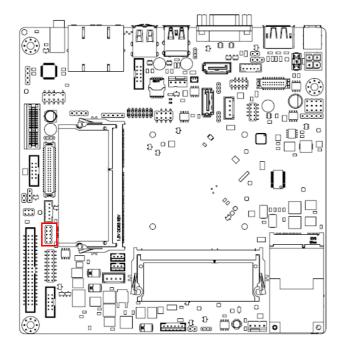

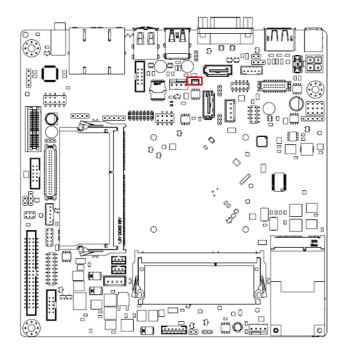

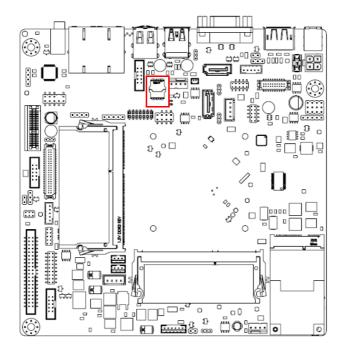

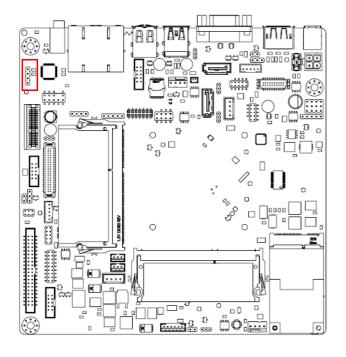

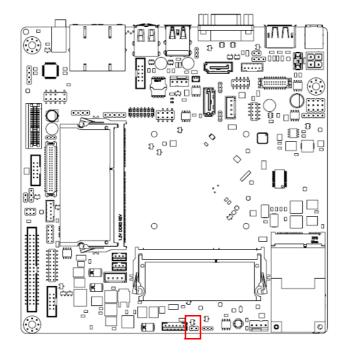

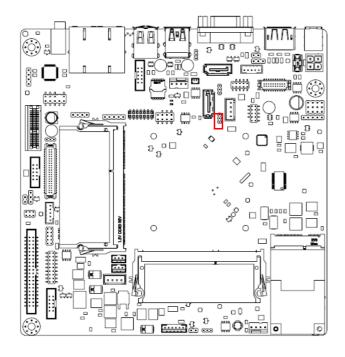

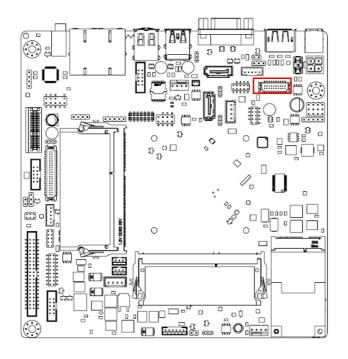

# 1.6 Board Layout: Jumper and Connector Locations

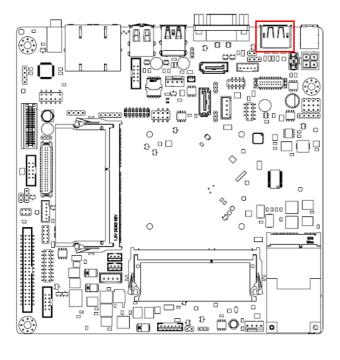

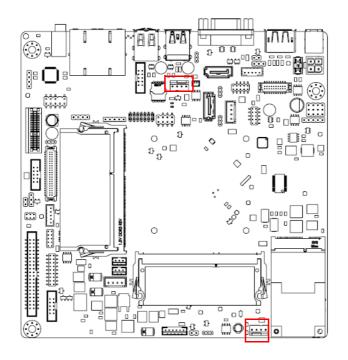

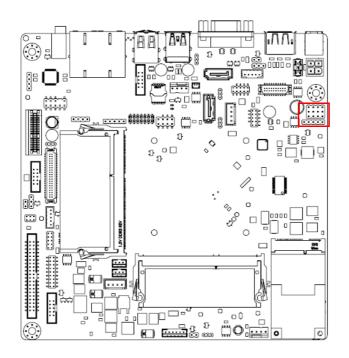

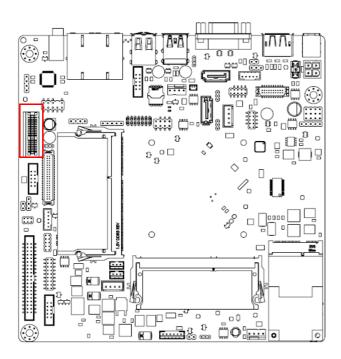

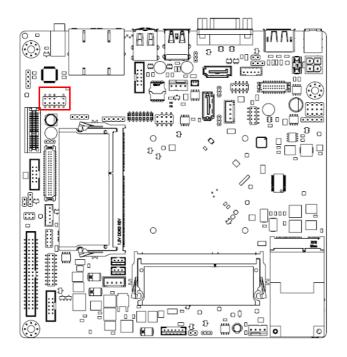

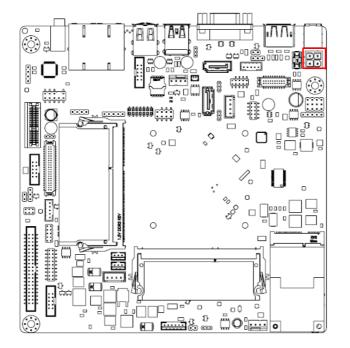

**Figure 1.1 Jumper and Connector Locations**

Figure 1.2 I/O Connectors

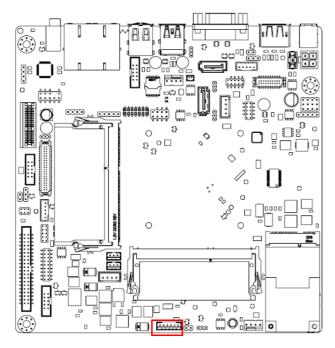

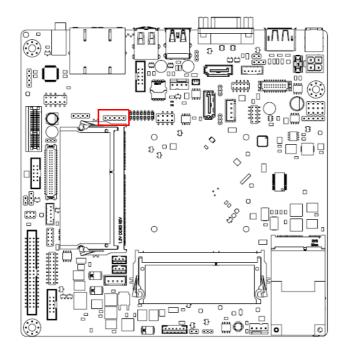

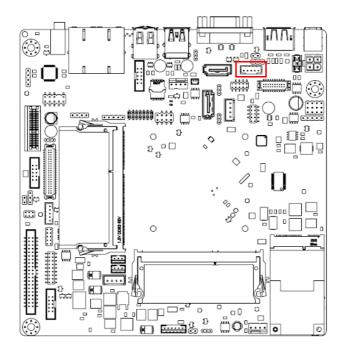

# 1.7 AIMB-215 B1 Board Diagram

Figure 1.3 AIMB-215 B1 Board Diagram

#### **Safety Precautions** 1.8

Warning! Always completely disconnect the power cord from the chassis when working with the hardware. Do not connect devices while the power is on. Sensitive electronic components can be damaged by sudden power surges. Only experienced electronics personnel should open the PC chassis.

Caution! Always ground yourself to remove any static charge before touching the motherboard. Modern electronic devices are very sensitive to electrostatic discharges. As a safety precaution, use a grounding wrist strap at all times. Place all electronic components on a static-dissipative surface or in a static-shielded bag when not in the chassis.

Caution! The computer is provided with a battery-powered real-time clock circuit. There is a danger of explosion if the battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

Caution! There is a danger of a new battery exploding if incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

## 1.9 Jumper Options

This section provides instructions on how to configure the motherboard by setting jumpers, and also outlines the default motherboard settings and options for each jumper.

#### 1.9.1 Setting Jumpers

The motherboard can be configured according to the application requirements with the setting of jumpers. A jumper is a metal bridge used to close an electrical circuit. Jumpers typically consist of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" (or turn ON) a jumper, connect the pins with the clip. To "open" (or turn OFF) a jumper, simply remove the clip. Some jumpers comprise a set of three pins, labeled 1, 2, and 3. With these jumpers, simply connect either Pins 1 and 2, or Pins 2 and 3. A pair of needlenose pliers may be necessary for setting jumpers.

#### 1.9.2 CMOS Mode Selection (JRTCTEST1)

The AIMB-215 B1 motherboard contains a jumper that can erase CMOS data and reset the system BIOS information. This jumper is typically set with Pins 1 and 2 being closed. To reset the CMOS data, set J1 to Pins 2 and 3 as closed for a few seconds before moving the jumper back to Pins 1 and 2 as closed. This procedure resets the CMOS to its default settings.

| Table 1.2: CMOS N | Table 1.2: CMOS Mode Selection (JRTCTEST1) |  |  |  |  |

|-------------------|--------------------------------------------|--|--|--|--|

| Function          | Setting                                    |  |  |  |  |

| Normal (Default)  |                                            |  |  |  |  |

| Clear CMOS        |                                            |  |  |  |  |

### 1.9.3 COM2 RS-232/422/485 Mode Selector (JSETCOM3)

Users can select between the RS-232/422/485 modes for COM3 using JSETCOM3. The default setting is "RS-232".

| Table 1.4: CO | Table 1.4: COM3 RS-232/422/485 Mode Selector (JSETCOM3) |  |  |  |  |

|---------------|---------------------------------------------------------|--|--|--|--|

| Function      | Jumper Settings                                         |  |  |  |  |

| RS-232*       | (5-6) + (7-9) + (8-10) + (13-15) + (14-16) closed       |  |  |  |  |

| RS-422        | (3-4) + (9-11) + (10-12) + (15-17) + (16-18) closed     |  |  |  |  |

| RS-485        | (1-2) + (9-11) + (10-12) + (15-17) + (16-18) closed     |  |  |  |  |

| *default      |                                                         |  |  |  |  |

### 1.9.4 LVDS Panel Voltage Selection (JLVDS1 + JLVDS2)

#### Table 1.5: LVDS Panel Voltage Selection (JLVDS1 + JLVDS2)

**Function Settings** Set the LVDS panel as +5 V Set LVDS panel as +3.3 V (default) JLVDS1 Set the LVDS panel as +12 V

#### 1.9.5 PSON1: ATX and AT Mode Selector

| Table 1.6: PSON1: ATX and AT Mode Selector |          |  |  |  |

|--------------------------------------------|----------|--|--|--|

| Closed Pins                                | Result   |  |  |  |

| 1-2                                        | AT Mode  |  |  |  |

| 2-3*                                       | ATX Mode |  |  |  |

<sup>\*</sup>Default

### 1.9.6 JOBS1 + JWDT1: OBS Beep and Watchdog Timer Output

| S1 + JWDT1: OBS Beep and Watchdog Timer Output |

|------------------------------------------------|

| Result                                         |

| Watchdog reset                                 |

| OBS alarm                                      |

|                                                |

<sup>\*</sup>default

| Function                                                       | Settings  |

|----------------------------------------------------------------|-----------|

|                                                                | 1 2 3 4 5 |

| Watchdog Timer Output (2-3) (default) OBS BEEP (4-5) (default) |           |

| Material a Transportant (4.0)                                  | 1 2 3 4 5 |

| Watchdog Timer disabled (1-2) OBS BEEP (4-5) (default)         |           |

#### 1.9.7 Case Open Pin Header Selection (JCASEOP\_SW1)

Table 1.8: Case Open Pin Header Selection (JCASEOP\_SW1)

Function

Settings

1 2 3

Normal Close (default)

1 2 3

Normal Open

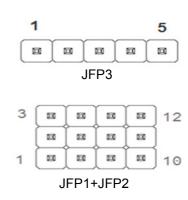

# 1.9.8 Power Switch/HDD LED/SMBus/Speaker Pin Header (JFP1 + JFP2)

Table 1.9: Power Switch/HDD LED/SMBus/Speaker Pin Header (JFP1 + JFP2)

| Function              | Settings                        |

|-----------------------|---------------------------------|

| JFP1 (7-10) (default) | 3 1                             |

|                       | HDD_LED SM_BUS  SPEAKER SPEAKER |

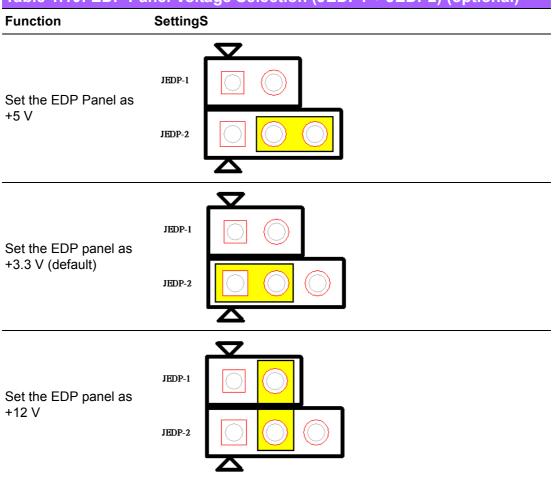

### 1.9.9 EDP Panel Voltage Selection (JEDP1 + JEDP2) (BOM Optional)

#### Table 1.10: EDP Panel Voltage Selection (JEDP1 + JEDP2) (optional)

### 1.9.10 JEIDA/VESA Selection (JLVDS\_VCON1)

# Table 1.11: JEIDA/VESA Selection (JLVDS\_VCON1)

| Function                                                            | Settings |

|---------------------------------------------------------------------|----------|

| Pull high to +V5.<br>(JEIDA or VESA base<br>on panel definition)    |          |

| Pull down to GND (default) (JEIDA or VESA base on panel definition) |          |

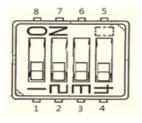

# 1.9.11 RS-485/422 Terminal Resistor Jumper (SW\_422\_1)

| Table 1.12: RS-485/422 Terminal Resistor Jumper (SW_422_1) |          |  |

|------------------------------------------------------------|----------|--|

| Function                                                   | Settings |  |

| Default                                                    | 8 7 6 5  |  |

| Add RS-485 terminator                                      | 8 7 6 5  |  |

| Add RS-422 terminator                                      | 8 7 6 5  |  |

# Chapter

Connecting Peripherals

### 2.1 Introduction

Most of the device connectors can be accessed from the top of the board during installation in the chassis. If the system is installed with several cards or the chassis is packed, partial removal of the card may be necessary to make all connections.

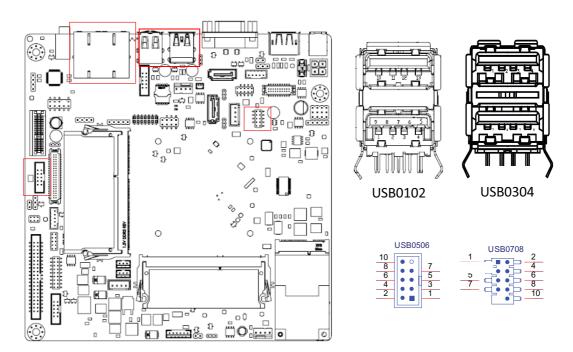

# 2.2 LAN and USB Ports (LAN1/2, USB0102/ USB0304/USB0506/USB0708)

AIMB-215 B1 provides up to seven USB 2.0 and one USB 3.0 ports. One USB 3.0 and three USB 2.0 are located on the rear side. The USB interface complies with the USB specification revision 2.0 that supports transmission rates of up to 480 Mbps, and revision 3.0 that supports transmission rates of up to 5 Gbps, and is also fuse protected. Furthermore, the USB interface can be disabled in the system BIOS setup menu.

The AIMB-215 B1 system is equipped with two high-performance 1000 Mbps Ethernet LAN adapters, both of which are supported by all major network operating systems. The RJ-45 jacks on the rear panel facilitate convenient LAN connection.

| Table 2.1: LAN LED Indicators |                     |  |

|-------------------------------|---------------------|--|

| LAN Mode                      | LAN Indicator       |  |

| 1 Gbps link on                | LED1 Green on       |  |

| 100 Mbps link on              | LED1 Orange on      |  |

| Active                        | LED2 Green flashing |  |

Note!

If Windows 7 is selected as the OS, users must install a USB 3.0 XHCI driver.

Please refer to Chapter 8 for information on XHCI driver installation.

# 2.3 VGA Connector (VGA1)

VGA1 is a standard 15-pin D-SUB connector commonly used for VGA. The pin assignments for VGA are detailed in Appendix B.

# 2.4 Serial Ports (COM1 ~ COM6)

AIMB-215 B1 supports six serial ports. COM3 is RS-232/422/485 and COM1/2/4/5/6 are RS-232. COM6 also supports 5 V/12 V according to jumper selection. Users can employ JSETCOM3 to select between the RS-232/422/485 modes for COM3. Such ports can be connected to serial devices, such as a mouse or printer, or to a communications network.

The IRQ and address ranges for both ports are fixed. However, users can disable the port or change the parameters via the system BIOS setup.

Various devices implement the RS-232/422/485 standards in different manners. Users who experience problems with a serial device are advised check the connector pin assignments.

# 2.5 PS/2 Keyboard and Mouse Connector (KBMS1)

Onboard six-pin wafer box connector, which supports one standard PS/2 keyboard and one standard PS/2 mouse.

# 2.6 Display Port Connector (DP1)

# 2.7 System FAN Connector (SYSFAN1/2)

For devices with a fan installed, this connector supports cooling fans of up to 500 mA (6 W).

# 2.8 Front Panel Connectors (JFP3/JFP1 + JFP2)

Several external switches are provided for monitoring and controlling the AIMB-215 B1.

#### 2.8.1 ATX Soft Power Switch (JFP1 + JFP2/PWR\_SW)

For computer cases equipped with ATX power supply, users should connect the Power On/Off button on the computer case to (JFP1 + JFP2/PWR\_SW) for convenient Power On/Off functionality.

#### 2.8.2 Reset (JFP1 + JFP2/RESET)

System Off

Off

Many computer cases offer the convenience of a specific reset button. Connect the wire for the reset button.

#### 2.8.3 HDD LED (JFP1 + JFP2/HDDLED)

An LED can be linked to the connector (JFP2/HDDLED) to indicate when the HDD is active.

#### 2.8.4 External Speaker (JFP1 + JFP2/SPEAKER)

(JFP1 + JFP2/SPEAKER) is a four-pin connector for an external speaker. If no external speaker is available, the AIMB-215 B1 provides an onboard buzzer as an alternative. To enable the buzzer, set Pins 7-10 as closed.

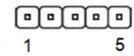

# 2.8.5 Power LED and Keyboard Lock Connector (JFP3/PWR\_LED and KEY LOCK)

(JFP3/PWR\_LED and KEY LOCK) is a five-pin connector for the Power-On LED and Key Lock function. Refer to Appendix B for detailed information regarding the pin assignments. The Power LED cable should be connected to Pins 1-3. The key lock button cable should be connected to Pins 4 and 5.

Three power supply connection modes exist. The first is the ATX power mode, where the system is powered on/off by momentarily pressing the power button. The second is the AT power mode, where the system is powered on/off using the power supply switch. The third is another AT power mode that involves the front panel power switch. The status differences indicated by the power LED are listed in the following table:

| Table 2.2: ATX Power Supply LED Status (AT power not supported) |                                                                        |                                                                                |                                                                               |

|-----------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Power mode                                                      | LED (ATX power mode) (On/off by momentarily pressing the power button) | LED<br>(AT power mode)<br>(Powered on/off using<br>the power supply<br>switch) | LED<br>(AT power mode)<br>(Powered on/off<br>using the front panel<br>switch) |

| PSON1 (on the back plane) jumper setting                        | Pins 2-3 closed                                                        | Pins 1-2 closed                                                                | Connect Pins 1 and 2 to the panel switch via cable                            |

| System On                                                       | On                                                                     | On                                                                             | On                                                                            |

| S3                                                              | Fast flashing                                                          | N/A                                                                            | N/A                                                                           |

| S4                                                              | Slow flashing                                                          | N/A                                                                            | N/A                                                                           |

Off

Off

# 2.9 Line-Out Connector (AUDIO1)

This connector supports line-out, mic-in, and line-in functions.

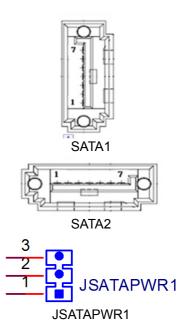

# 2.10 Serial ATA Interface (SATA1/2) & SATADOM Power Pin Header (JSATAPWR1)

AIMB-215 B1 features a high-performance Serial ATA interface (up to 300 MB/s) that allows cabling to hard drives using long, thin cables.

Note!

SATA2 is only supported when mSATA is not in use. SATA2 and mSATA cannot be used concurrently.

| Table 2.3: SATADOM Power Pin Header (JSATAPWR1) |          |

|-------------------------------------------------|----------|

| Pin                                             | Signal   |

| 1                                               | GND      |

| 2                                               | SATA_DOM |

| 3                                               | +V5      |

# 2.11 PCI-Express x1 Slot (PCIEX1\_1)

The AIMB-215 B1 features one PCIe x1 slot.

# 2.12 Front Panel Audio Connector (FPAUD1)

This connector is for a chassis-mounted front-panel audio I/O module that supports HD Audio. This connector is attached using the front panel audio I/O module cable.

## 2.13 ATX 12V Power Connector (ATX12V1)

This connector is for an ATX Micro-Fit power supply. The plugs from the power supply are designed to fit these connectors in only one direction. Determine the correct orientation and press firmly until the connectors mate completely.

# 2.14 SPI Flash Connector(SPI\_CN1)

The SPI flash card pin header may be used to flash the BIOS if the AIMB-215 B1 cannot be powered on.

# 2.15 LVDS Backlight Inverter Power Connector **(INV1)**

Note! ■ Signal Description

**Signal** VR

V

Vadj=0.75 V

Signal Description

(Recommended: 4.7 K $\Omega$ , >1/16 W) LCD backlight ON/OFF control signal

ENBKL

# 2.16 LVDS Connector (LVDS1)

Pin 3: GND  $\rightarrow$  Panel connected NC/3.3 V  $\rightarrow$  No panel

# 2.17 General Purpose I/O Connector (GPIO1)

# 2.18 CMOS Battery Wafer Box (BAT1)

# 2.19 SPI BIOS Socket (SPI1)

# 2.20 SPDIF Interface Pin Header (SPDIF\_OUT1)

# 2.21 Audio Amplifier Output Pin Header (JAMP1) (BOM Optional)

# 2.22 ATX Power Supply (5VSB) Connector (ATX\_5VSB1)

# 2.23 SATA Power Connector (SATA\_PWR1/2)

# 2.24 Case Open Pin Header (JCASE1)

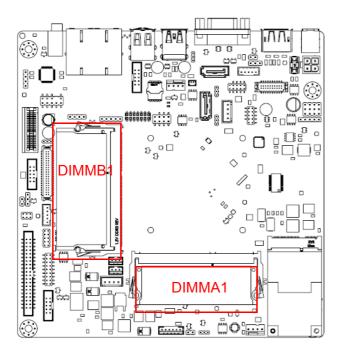

# 2.25 DDR3L SODIMM Socket (DIMMA1/B1)

**Note!** AIMB-215 B1 supports 1.35 V memory only. Users must populate the memory on socket DIMMA1 first.

Users are advised to use memory modules of the same type, speed, and frequency for each motherboard. Memory modules of different types and speeds should not be used.

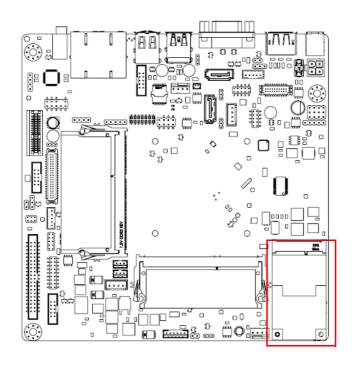

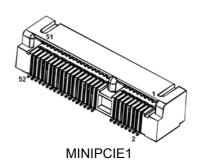

# 2.26 Mini-PCle and mSATA Connector (MINIPCIE1)

# 2.27 Mini-PCle Connector (MINIPCIE2)

# 2.28 Low Pin Count Interface Header (LPC1)

# 2.29 RTC Reset Pin Header (JRTCTEST1)

# 2.30 eDP Connector (eDP1) (BOM Optional)

# 2.31 eDP Backlight Inverter Power Connector (INV-EDP1) (BOM Optional)

# 2.32 SIM Card Holder (SIM2)

Chapter

**BIOS Operation**

# 3.1 Introduction

With the AMI BIOS Setup program, users can modify the BIOS settings and control special system features. The Setup program comprises several menus with options for adjusting or turning special features on or off. This chapter describes the basic navigation of the AIMB-215 B1 BIOS setup menu pages.

# 3.2 BIOS Setup

The AIMB-215 B1 Series is equipped with built-in AMI BIOS and a CMOS Setup Utility that allows users to configure specific settings or activate certain system features.

The CMOS Setup Utility saves the configuration in the CMOS RAM of the mother-board. When the system power is turned off, the battery on the board supplies the necessary power to preserve the CMOS RAM.

When the power is turned on, press the <Del> button during the BIOS power-on self-test (POST) to access the CMOS Setup Utility screen.

| Control Keys               |                                                                                                              |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------|--|

| < ↑ >< ↓ >< ← >< → >       | Move select item                                                                                             |  |

| <enter></enter>            | Select item                                                                                                  |  |

| <esc></esc>                | Main Menu - Quit without saving changes to the CMOS Sub Menu - Exit current page and return to the Main Menu |  |

| <page +="" up=""></page>   | Increase the numeric value or make changes                                                                   |  |

| <page -="" down=""></page> | Decrease the numeric value or make changes                                                                   |  |

| <f1></f1>                  | General help, for Setup Sub Menu                                                                             |  |

| <f2></f2>                  | Item help                                                                                                    |  |

| <f5></f5>                  | Load previous values                                                                                         |  |

| <f7></f7>                  | Load setup defaults                                                                                          |  |

| <f10></f10>                | Save all CMOS changes                                                                                        |  |

Press <Del> to enter the AMI BIOS CMOS Setup Utility, the Main Menu will appear on the screen. Use the arrow keys to select items and press <Enter> to access the submenu.

The Main BIOS Setup page comprises two main frames. The left frame displays all configurable options. Grayed-out options cannot be configured, whereas the options displayed in blue can be. The right frame also displays the key legend.

The area above the key legend is reserved for text messages. When an option is selected in the left frame, the display text changes to white and is often accompanied by a text message.

#### System Time/System Date

Use this option to change the system time and date. Highlight the System Time or System Date using the <Arrow> keys. Enter new values via the keyboard. Press the <Tab> or <Arrow> keys to move between fields. The date must be entered in MM/DD/YY format. The time must be entered in HH:MM:SS format.

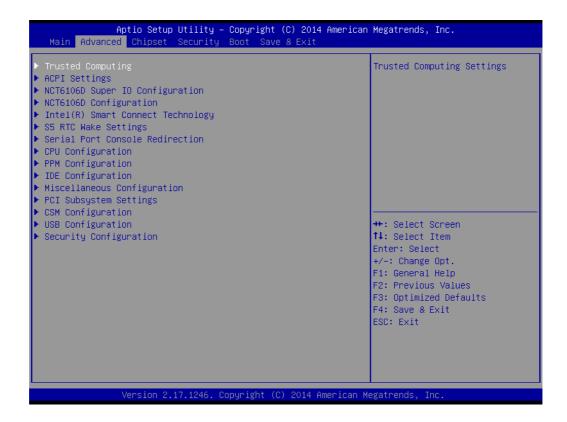

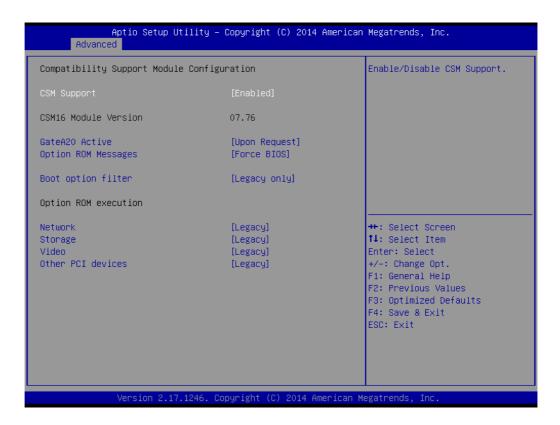

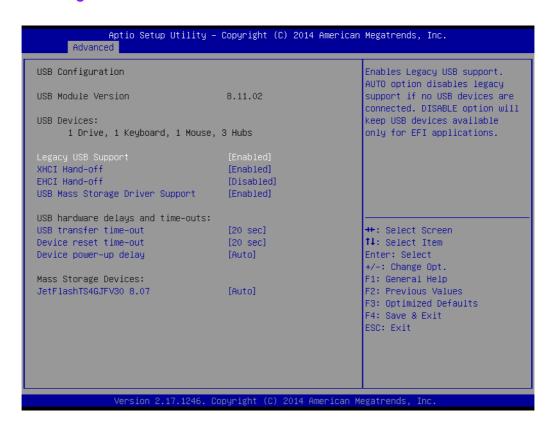

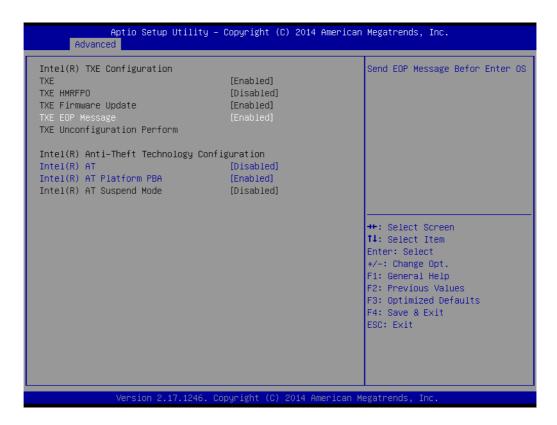

# 3.2.2 Advanced BIOS Features

Select the Advanced tab from the AIMB-215 B1 Setup menu to enter the Advanced BIOS Setup page. Users can select any item in the left frame of the screen, such as CPU Configuration, to access the submenu for that item. Select an Advanced BIOS Setup option by highlighting the text using the <Arrow> keys. All Advanced BIOS Setup options are described in this section. The Advanced BIOS Setup menu screen is shown below. The submenus are described in the following pages.

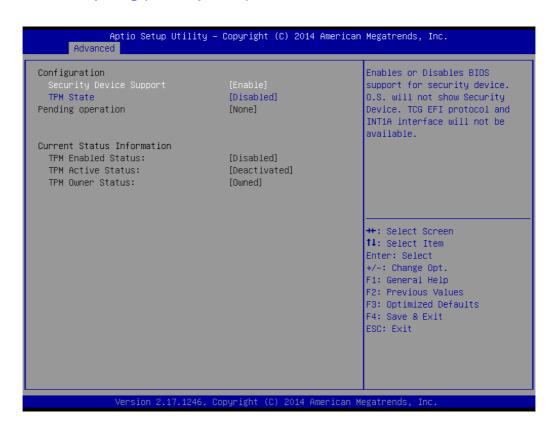

# 3.2.2.1 Trusted Computing (BOM Optional)

# Security Device Support

To enable or disable BIOS support for security device

#### ■ TPM State

To enable or disable security device.

## Pending operation

Schedule an Operation for the Security Device.

# ■ TPM Enabled Status

Provides the current capability state of the security device.

#### ■ TPM Active Status

Provides the current capability state of the security device.

# ■ TPM Owner Status

Provides current Ownership state. ie: Owned or Unowned.

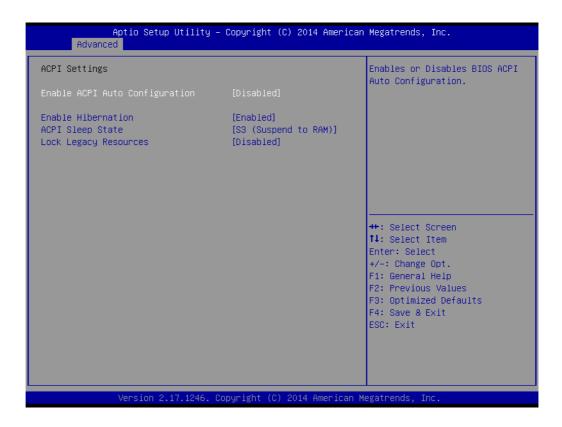

# 3.2.2.2 ACPI Settings

# **■** Enable ACPI Auto Configuration

This item allows users to enable or disable ACPI auto configuration.

#### **■** Enable Hibernation

This item allows users to enable or disable hibernation.

## ACPI Sleep State

This item allows users to set the ACPI sleep state.

## Lock Legacy Resources

This item allows users to lock legacy device resources.

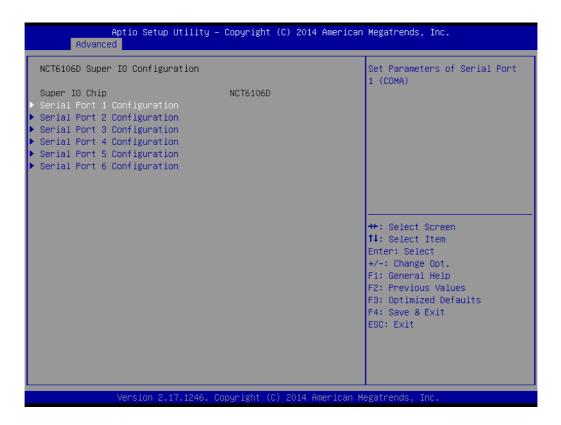

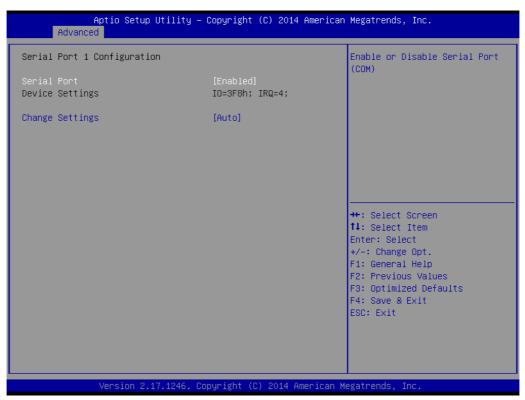

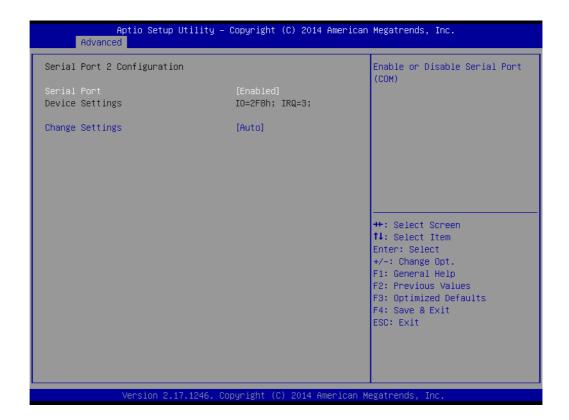

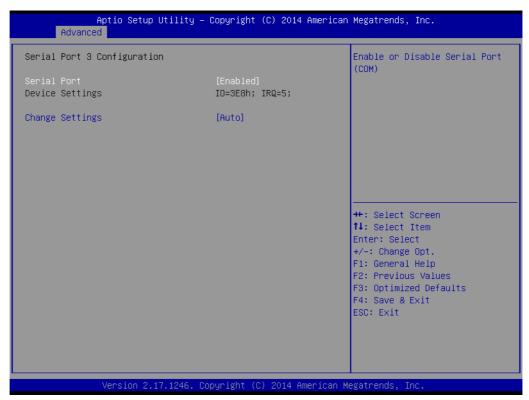

# 3.2.2.3 Super IO Configuration

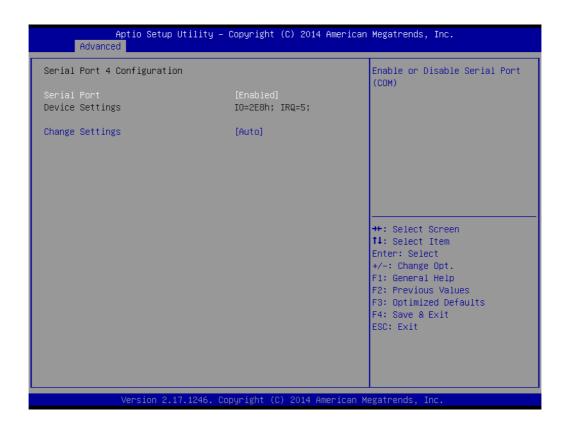

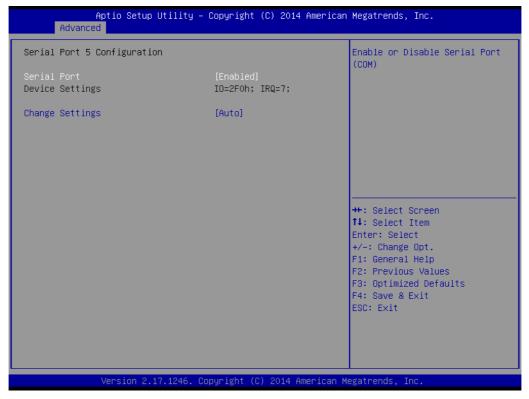

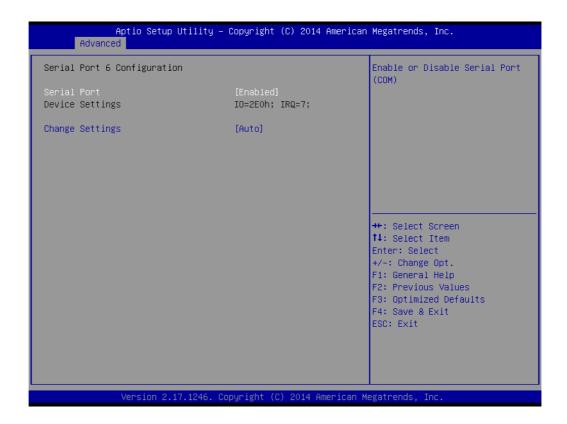

#### Serial Ports 1/2/3/4/5/6

This item allows users to enable or disable serial Ports 1/2/3/4/5/6.

# Change Settings

This item allows users to change the settings for serial Ports 1/2/3/4/5/6.

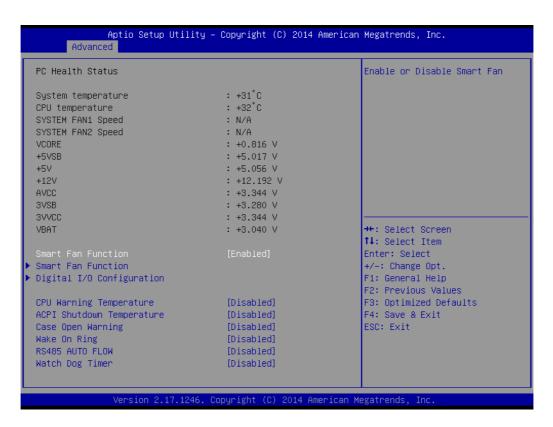

#### 3.2.2.4 PC Health Status

This page shows the AIMB-215 B1 PC health status.

#### Smart Fan Function

This item allows users to enable or disable the System Smart Fan function.

# CPU Warning Temperature

This item allows users to set the CPU temperature threshold. When the system CPU reaches the threshold temperature, a buzzer will emit a warning alert.

# ACPI Shutdown Temperature

This item allows users to set the CPU temperature threshold at which the system automatically shuts down to prevent the CPU from overheating.

# Case Open Warning

This item allows users to enable or disable the Case Open Warning function.

#### Wake On Ring

This item allows users to enable or disable Wake On Ring functionality.

#### RS-485 AUTO FLOW

This item allows users to enable or disable the RS-485 AUTO FLOW function.

#### Watchdog Timer

This item allows users to enable or disable the Watchdog timer.

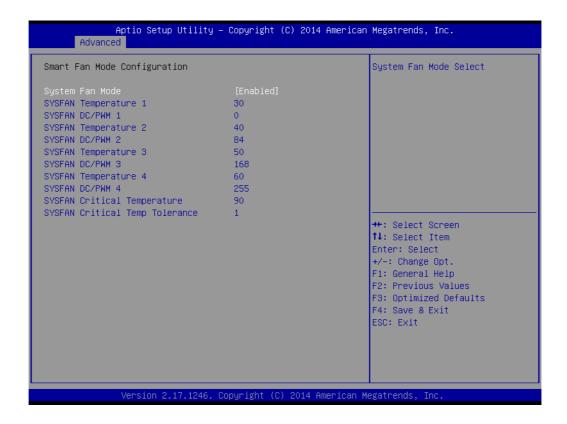

# 3.2.2.5 Smart Fan Mode Configuration

This page shows the Smart Fan Mode items.

#### Smart Fan Mode

This item allows users to enable or disable Smart Fan mode.

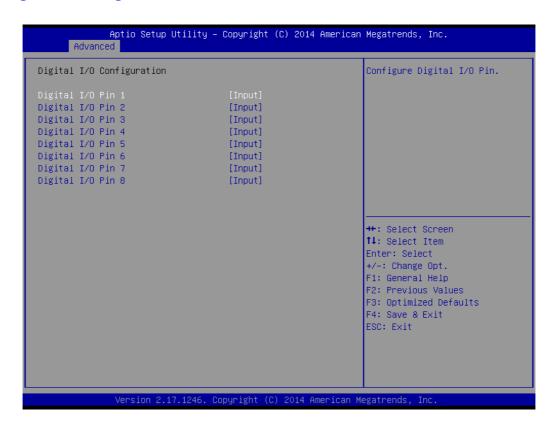

## 3.2.2.6 Digital I/O Configuration

## Digital I/O Configuration

This item allows users to set digital I/O 1 to 8 as inputs or outputs.

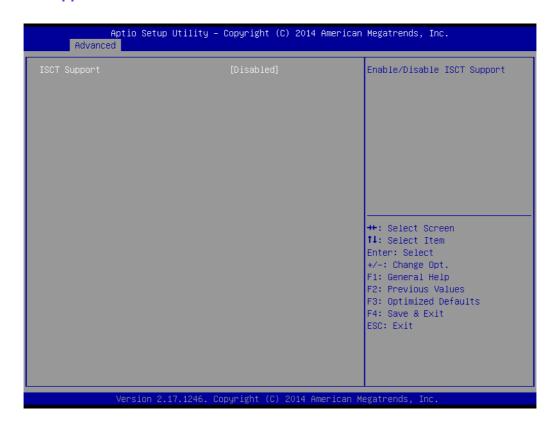

## 3.2.2.7 ISCT Support

# ■ ISCT Support

This item allows users to enable or disable ISCT support.

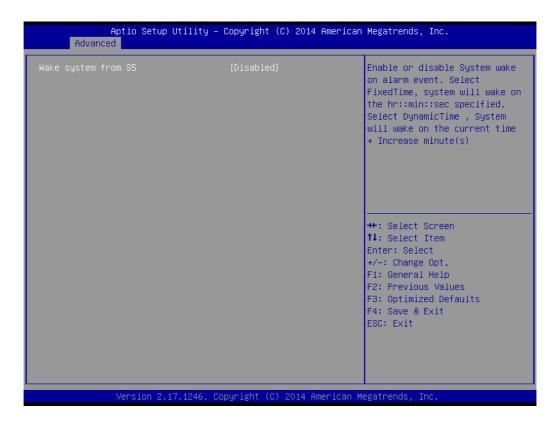

# 3.2.2.8 S5 RTC Wake Settings

# ■ Wake System From S5

This item allows users to enable or disable system wake on alarm event.

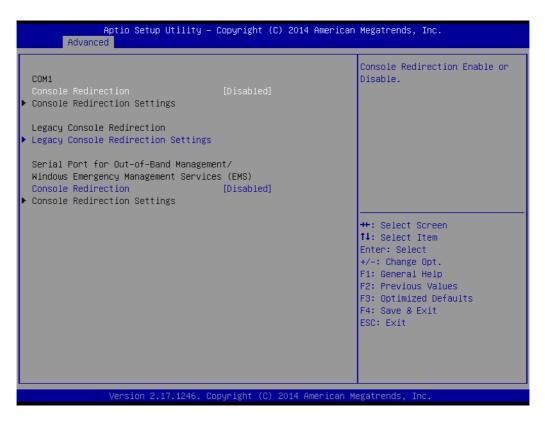

# 3.2.2.9 Serial Port Console Redirection

## Console Redirection

This item allows users to enable or disable console redirection.

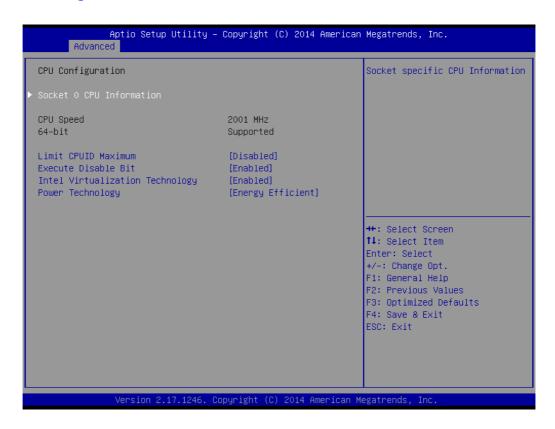

# 3.2.2.10 CPU Configuration

## ■ Limit CPUID Maximum

This item allows users to enable or disable the ability to limit the CPUID maximum.

#### Execute Disable Bit

This item allows users to enable or disable the Execute Disable Bit function.

# Intel Virtualization Technology

This item allows users to enable or disable Intel® Virtualization Technology.

#### Power Technology

Enable power management features.

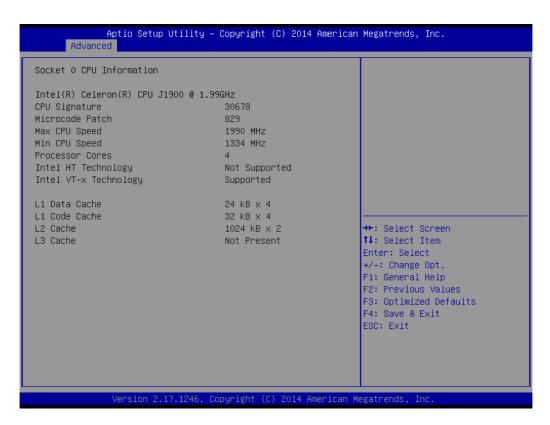

This page shows the CPU information.

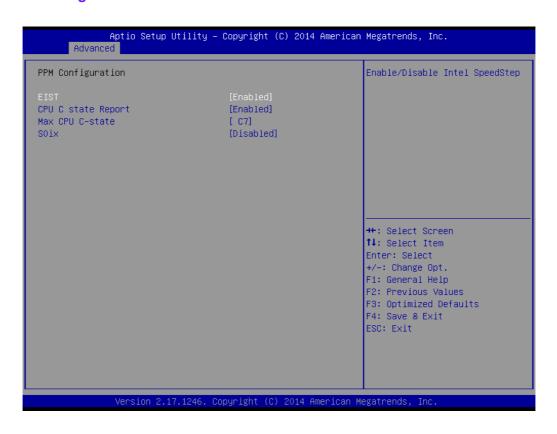

# 3.2.2.11 PPM Configuration

- **EIST**

- To enable or disable Intel SpeedStep.

- **CPU C state Report** To enable or disable CPU C state report to OS.

#### Max CPU C-state

This option controls the Max C state that the processor will support.

#### ■ S0ix

This item allows users to enable or disable the CPU S0ix state.

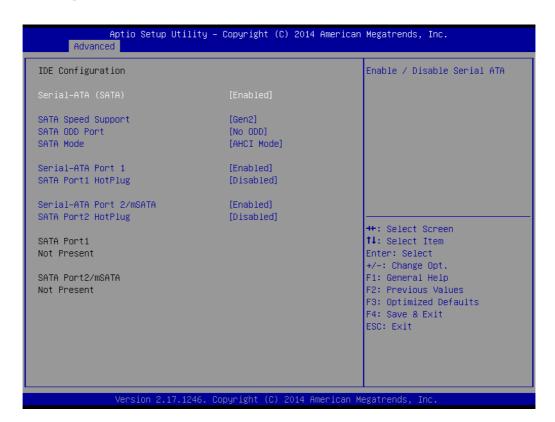

# 3.2.2.12 IDE Configuration

# ■ Serial-ATA (SATA)

This item allows users to enable or disable the SATA device.

# SATA Speed Support

This item allows users to select the SATA speed (Gen1 or Gen2).

#### ■ SATA ODD Port

This item allows users to set Port 1 or 2 to have ODD functionality.

#### SATA Mode

This item allows users to select the mode for SATA controller(s).

#### Serial-ATA Port 1

This item allows users to enable or disable the Serial-ATA Port 1 device.

#### SATA Port 1 Hot Plug

This item allows users to enable or disable the SATA Port 1 hot plug.

#### Serial-ATA Port 2

This item allows users to enable or disable the Serial-ATA Port 2 / mSATA device.

# SATA Port 2 Hot Plug

This item allows users to enable or disable the SATA Port 2 hot plug.

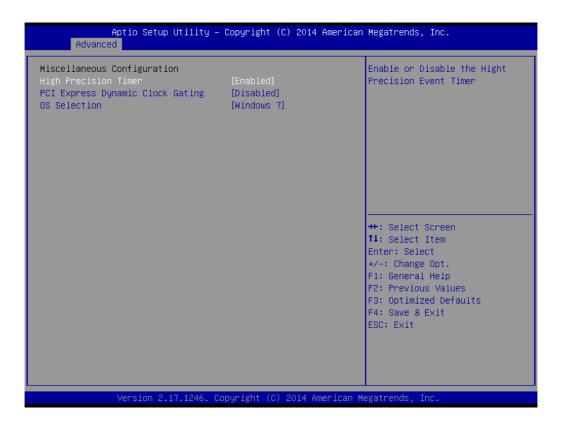

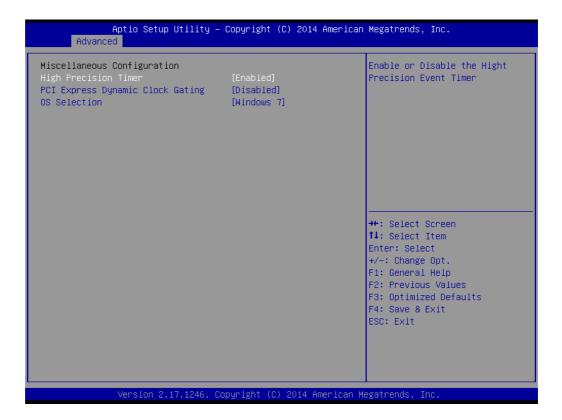

# 3.2.2.13 Miscellaneous Configuration

# High Precision Timer

This item allows users to enable or disable the high-precision timer.

# ■ PCI Express Dynamic Clock Gating

This item allows users to enable or disable the PCI Express Dynamic Clock Gating function.

## OS Selection

This item allows users to set the OS as Windows 7 or Windows 8.x.

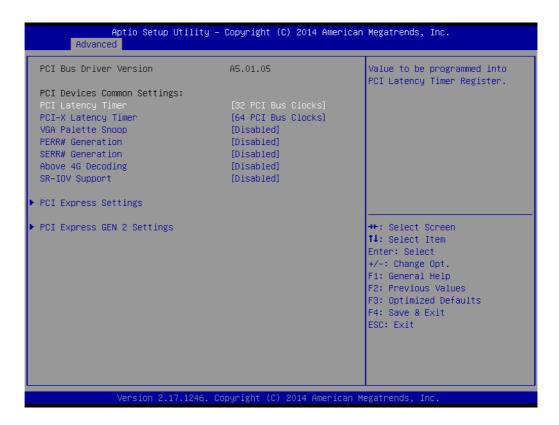

# 3.2.2.14 PCI Subsystem Settings

# **General PCI Device Settings**

#### PCI Latency Timer

This item allows users to program the timer value into the PCI Latency Timer Register.

# ■ PCI-X Latency Timer

Value to be programmed into PCI Latency Timer Register.

#### VGA Palette Snooping

This item allows users to enable or disable VGA palette register snooping.

# ■ PERR# Generation

This item allows users to enable or disable PERR# Generation.

#### ■ SERR# Generation

This item allows users to enable or disable SERR# Generation.

### Above 4G Decoding

This item allows users to enable or disable 64-bit-capable device decoding in above 4G address spaces (if the system supports 64-bit PCI decoding).

#### SR-I0V Support

If the system has SR-IOV-capable PCIe devices, this item allows users to enable or disable single root IO virtualization support.

.

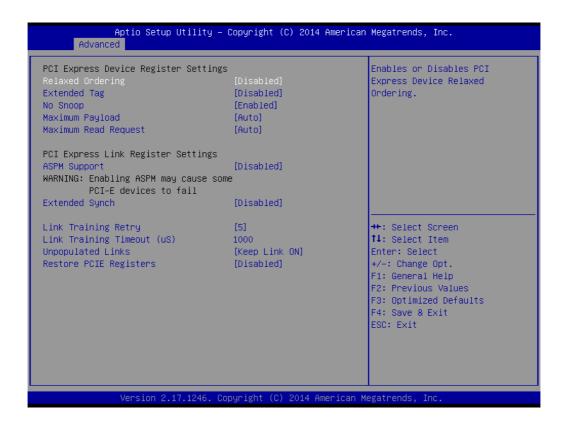

# **PCI Express Device Register Settings**

#### Relaxed Ordering

This item allows users to enable or disable relaxed ordering.

#### Extended Tag

This item allows users to enable or disable extended tags.

### No Snoop

This item allows users to enable or disable the No Snooping function.

#### Maximum Payload

This item allows users to set the maximum payload for PCI Express devices or authorize the system BIOS to select the value.

# Maximum Read Request

This item allows users to set the maximum read request size for PCI Express devices or authorize the system BIOS to select the value.

#### **PCI Express Link Register Settings**

#### ASPM Support

This item allows users to enable or disable ASPM support.

### Extended Synch

This item allows users to enable or disable the Extended Synch function.

#### Link Training Retry

This item allows users to define the number of retry attempts for software link training.

#### ■ Link Training Timeout

This item allows users to define the number of microseconds the software will wait before polling the "Link Training" bit in the link status register. Values range from 10 to 10000 uS.

### Unpopulated Links

To save power, the software will disable unpopulated PCI Express links if this option set as "Disable Link".

# Restore PCIE Registers

On non-PCI Express aware OS (pre-Windows Vista), some devices may not be correctly re initialized after S3. Enabling this item restores PCI Express device configurations upon S3 resume.

**Warning!** Enabling this item can cause issues with other hardware after S3 resume.

| PCI Express GEN2 Device Register        | In device Functions that |                                |

|-----------------------------------------|--------------------------|--------------------------------|

| Completion Timeout                      | [Default]                | support Completion Timeout     |

| ARI Forwarding                          | [Disabled]               | programmability, allows system |

| AtomicOp Requester Enable               | [Disabled]               | software to modify the         |

| AtomicOp Egress Blocking                | [Disabled]               | Completion Timeout value.      |

| IDO Request Enable                      | [Disabled]               | 'Default' 50us to 50ms. If     |

| IDO Completion Enable                   | [Disabled]               | 'Shorter' is selected,         |

| LTR Mechanism Enable                    | [Disabled]               | software will use shorter      |

| End-End TLP Prefix Blocking             | [Disabled]               | timeout ranges supported by    |

|                                         |                          | hardware. If 'Longer' is       |

| PCI Express GEN2 Link Register Settings |                          | selected, software will use    |

| Target Link Speed                       | [Auto]                   |                                |

| Clock Power Management                  | [Disabled]               |                                |

| Compliance SOS                          | [Disabled]               | →+: Select Screen              |

| Hardware Autonomous Width               | [Disabled]               | ↑↓: Select Item                |

| Hardware Autonomous Speed               | [Disabled]               | Enter: Select                  |

|                                         |                          | +/-: Change Opt.               |

|                                         |                          | F1: General Help               |

|                                         |                          | F2: Previous Values            |

|                                         |                          | F3: Optimized Defaults         |

|                                         |                          | F4: Save & Exit                |

|                                         |                          | ESC: Exit                      |

|                                         |                          |                                |

|                                         |                          |                                |

|                                         |                          |                                |

# **PCI Express GEN2 Device Register Settings**

# Completion Timeout

This item is an in-device function that supports Completion Timeout program-mability by allowing the system software to modify the Completion Timeout value. The default value is 50us to 50ms. If the "Shorter" option is selected, the software will use the shorter timeout ranges supported by the hardware. If the "Longer" option is selected, the software will use longer timeout ranges.

#### ARI Forwarding

If supported by the hardware and set to "Enabled", the downstream port prevents the traditional device number field from being 0 enforcement when turning a Type 1 Configuration Request into a Type 0 Configuration Request, thereby permitting access to the extended functions of the ARI device located below the port. The default value is "Disabled".

# AtomicOp Requester Enable

If supported by the hardware and set to "Enabled", this function initiates AtomicOp requests only if the Bus Master Enable bit is in the Command Register Set.

# AtomicOp Egress Blocking

If supported by the hardware and set to "Enabled", outbound AtomicOp requests transmitted via egress ports will be blocked.

# ■ IDO Request Enable

If supported by the hardware and set to "Enabled", this item allows users to set the number of ID-based ordering (IDO) bit (Attribute[2]) requests to be initiated.

#### ■ IDO Completion Enable

If supported by the hardware and set to "Enabled", this item allows users to set the number of IDO bit (Attribute[2]) requests to be initiated.

#### ■ LTR Mechanism Enable

If supported by the hardware and set to "Enabled", the Latency Tolerance Reporting (LTR) mechanism will be activated.

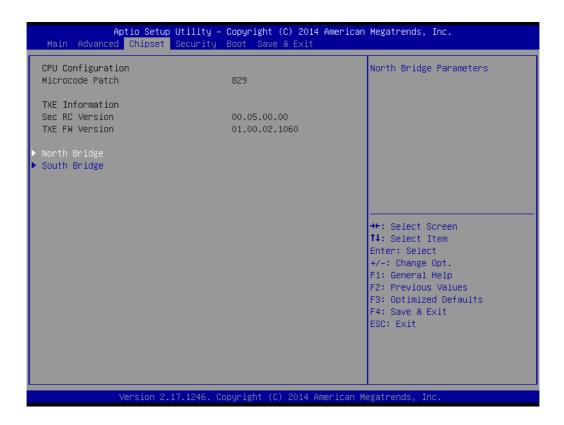

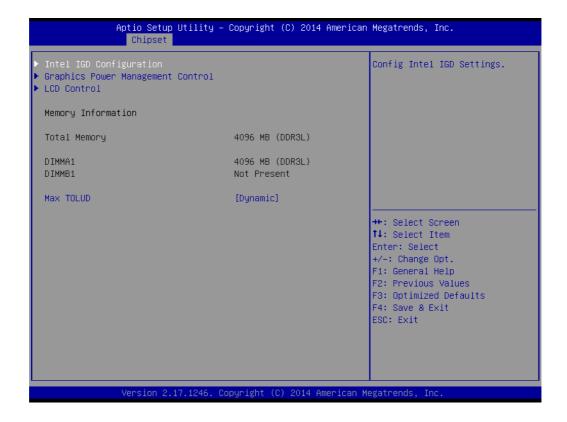

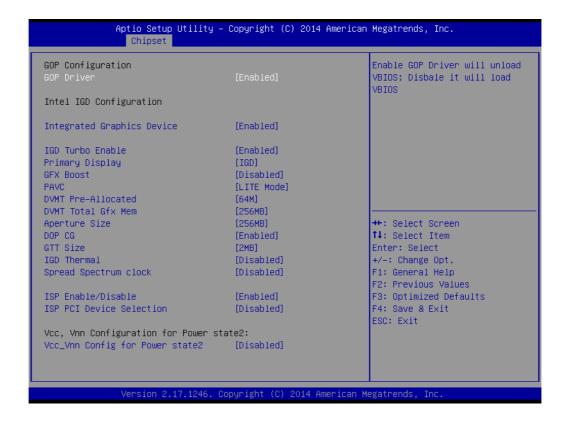

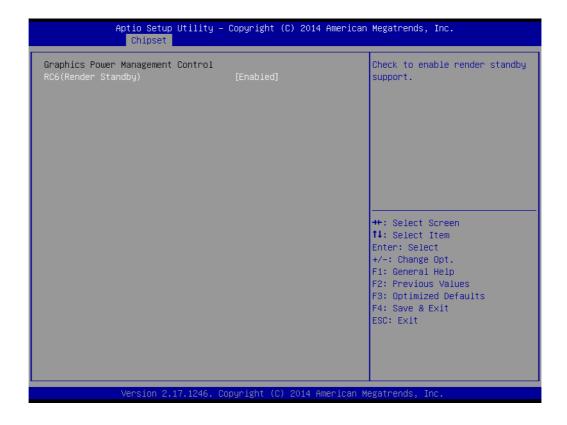

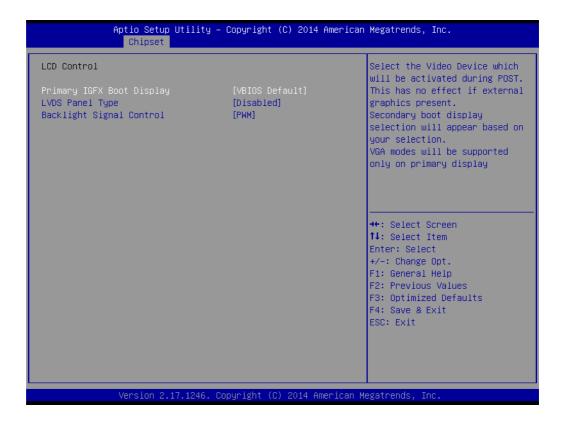

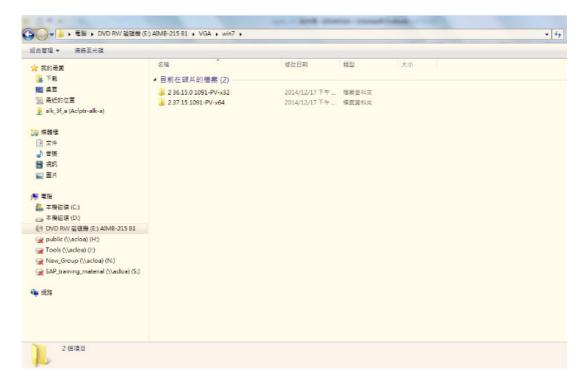

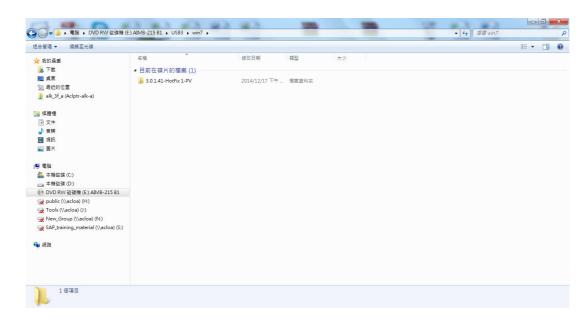

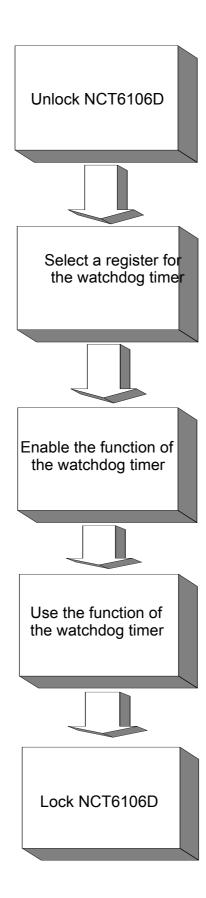

# ■ End-End TLP Prefix Blocking