# **ARM Cortex-A9 + FPGA CPU Module**

**ULTRA** Line

## **HARDWARE MANUAL**

<Page intentionally left blank>

### **Table of Contents**

| 1 | Pre | face                                 | 6  |

|---|-----|--------------------------------------|----|

|   | 1.1 | About this manual                    |    |

|   | 1.2 | Copyrights/Trademarks                |    |

|   | 1.3 | Standards                            |    |

|   | 1.4 | Disclaimers                          |    |

|   | 1.5 | Warranty                             |    |

|   | 1.6 | Technical Support                    |    |

|   | 1.7 | Related documents                    |    |

|   |     | Conventions, Abbreviations, Acronyms |    |

| 2 |     | oduction                             |    |

|   | 2.1 |                                      |    |

|   | 2.2 | Block Diagram                        |    |

|   |     | Feature Summary                      |    |

| 3 |     | sign overview                        |    |

|   | 3 1 | Xilinx Zynq™-7000 SoC                | 19 |

|   | 3.2 |                                      |    |

|   | 3.3 | NOR flash bank                       |    |

|   | 3.4 | NAND flash bank                      |    |

|   | 3.5 | Integrated FPGA                      |    |

|   | 3.6 | Memory Map                           |    |

|   | 3.7 | Power supply unit                    |    |

|   |     | CPU module connectors                |    |

| 4 |     | chanical specifications              |    |

| • | 4.1 | Board Layout                         |    |

|   |     | Connectors                           |    |

| 5 |     | ver, reset and control               |    |

| • | 5.1 | ·                                    |    |

|   |     | Reset                                |    |

|   |     | .2.1 MRST (J2.116)                   |    |

|   |     | .2.2 PORSTn (J2.114)                 |    |

|   |     | .2.3 SYS RSTn (J2.112)               |    |

|   |     | .2.4 PS MIO51 501 (J2.106)           |    |

|   |     | .2.5 PS_MIO50_501 (J2.104)           |    |

|   |     | Voltage monitor                      |    |

|   |     | System boot                          |    |

|   |     | .4.1 Boot modes                      |    |

|   |     | .4.2 Default boot configuration      |    |

|   |     | .4.3 Boot sequence customization     |    |

|   |     | Clock scheme                         |    |

|   |     | Recovery                             |    |

|   |     | 6.1 JTAG Recovery                    | 34 |

|   |     |                                      |    |

|   | 5.   | .6.2 SD/MMC Recovery                   | .35 |

|---|------|----------------------------------------|-----|

|   | 5.7  | Multiplexing                           |     |

|   | 5.8  | RTC                                    | .35 |

|   | 5.9  | Watchdog                               | .36 |

| 6 | Pino | out table                              | .38 |

|   | 6.1  | Carrier board mating connector J1      |     |

|   | 6.2  | Carrier board mating connector J2      |     |

|   |      | Carrier board mating connector J3      |     |

| 7 |      | ipheral interfaces                     |     |

|   |      | Notes on pin assignment                |     |

|   |      | PS interfaces                          |     |

|   |      | .2.1 Gigabit Ethernet                  |     |

|   | 7    | 2.2 USB                                |     |

|   |      | 2.3 Quad-SPI                           |     |

|   |      | .2.4 Static memory controller (NAND)   |     |

|   |      | 2.5 I <sup>2</sup> C0                  |     |

|   |      | 2.6 SD/SDIO                            |     |

|   |      | 2.7 UART1                              |     |

|   |      | 2.8 CAN                                |     |

|   |      | 2.9 JTAG                               |     |

|   |      | PL interfaces                          |     |

|   |      | .3.1 FPGA Bank 34                      |     |

|   |      | 3.2 FPGA Bank 35                       |     |

|   |      | 7.3.2.1Differential pairs              |     |

|   |      | 7.3.2.2Single-ended signals            |     |

|   |      | 7.3.2.3FDDR ADDR class                 |     |

|   |      | 7.3.2.4FDDR CK class                   |     |

|   |      | 7.3.2.5FDDR BYTE0 class                |     |

|   |      | 7.3.2.6FDDR BYTE1 class                |     |

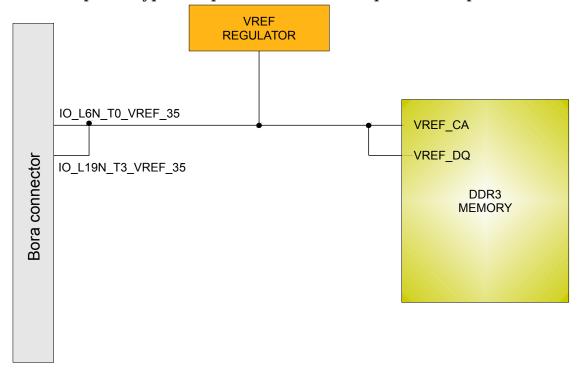

|   |      | 7.3.2.7VREF                            |     |

|   |      | 7.3.2.8Related Xilinx documentation    |     |

|   | 7    | .3.3 FPGA Bank 13 (Zyng 7020 only)     |     |

| 8 |      | rier board design guidelines           |     |

| Ŭ | 8.1  | Suggested PCB specifications           |     |

|   |      | Power rails                            |     |

|   | 8.3  | Main SD/MMC interface                  |     |

|   | 8.4  | Main Gigabit Ethernet interface (ETH0) |     |

|   |      | CAN interface                          |     |

|   |      | XADC interface                         |     |

| 9 |      | erational characteristics              |     |

| J | 9.1  | Maximum ratings                        |     |

|   | 9.2  | Recommended ratings                    |     |

|   |      | Power consumption                      |     |

|   | J.J  | 1 OWG GOLIGATIPHOLL                    | .oo |

| 9.3.1 Set 1                                                     | 81 |

|-----------------------------------------------------------------|----|

| 9.3.2 Set 2                                                     | 81 |

| 9.4 Heat Dissipation                                            | 81 |

| 10 Application notes                                            |    |

|                                                                 |    |

| Index of Tables                                                 |    |

| Tab. 1: Related documents                                       | 8  |

| Tab. 2: Abbreviations and acronyms used in this manual          |    |

| Tab. 3: CPU, Memories, Buses                                    | 17 |

| Tab. 4: Peripherals                                             |    |

| Tab. 5: FPGA specifications                                     | 18 |

| Tab. 6: Electrical, Mechanical and Environmental Specifications | 18 |

| Tab. 7: XC7-Z0x0 comparison                                     | 20 |

| Tab. 8: DDR3 specifications                                     | 21 |

| Tab. 9: NOR flash specifications                                | 21 |

| Tab. 10: NAND flash specifications                              | 22 |

| Illustration Index                                              |    |

|                                                                 | 10 |

| Fig. 1: BORA – Dual ARM Cortex A9 plus FPGA                     |    |

| Fig. 2: BORA – Powered by Zynq processor                        |    |

| Fig. 3: BORA SOM (top view)                                     |    |

| Fig. 4: Board layout - Side view                                |    |

| Fig. 5: Board layout - Top view                                 |    |

| Fig. 6: Connectors layout                                       | 28 |

# 1 Preface

#### 1.1 About this manual

This Hardware Manual describes the BORA CPU module design and functions.

Precise specifications for the Xilinx Zynq processor can be found in the CPU datasheets and/or reference manuals.

### 1.2 Copyrights/Trademarks

Ethernet<sup>®</sup> is a registered trademark of XEROX Corporation. All other products and trademarks mentioned in this manual are property of their respective owners.

All rights reserved. Specifications may change any time without notification.

#### 1.3 Standards

**DAVE Embedded Systems** is certified to ISO 9001 standards.

### 1.4 Disclaimers

**DAVE Embedded Systems** does not assume any responsibility about availability, supplying and support regarding all the products mentioned in this manual that are not strictly part of the BORA CPU module.

BORA CPU Modules are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. **DAVE Embedded Systems** customers who are using or selling these products for use in such applications do so at their own risk and agree to fully indemnify **DAVE Embedded Systems** for any damage resulting from such improper use or sale.

### 1.5 Warranty

BORA is warranted against defects in material and workmanship for the warranty period from the date of shipment. During the warranty period, **DAVE Embedded**

**Systems** will at its discretion decide to repair or replace defective products. Within the warranty period, the repair of products is free of charge as long as warranty conditions are observed.

The warranty does not apply to defects resulting from improper or inadequate maintenance or handling by the buyer, unauthorized modification or misuse, operation outside of the product's environmental specifications or improper installation or maintenance.

**DAVE Embedded Systems** will not be responsible for any defects or damages to other products not supplied by **DAVE Embedded Systems** that are caused by a faulty BORA module.

### 1.6 Technical Support

We are committed to making our product easy to use and will help customers use our CPU modules in their systems. Technical support is delivered through email to our valued customers. Support requests can be sent to <a href="mailto:support-bora@dave.eu">support-bora@dave.eu</a>.

Software upgrades are available for download in the restricted access download area of **DAVE Embedded Systems** web site: <a href="http://www.dave.eu/reserved-area">http://www.dave.eu/reserved-area</a>. An account is required to access this area and is provided to customers who purchase the development kit (please contact <a href="mailto:support-bora@dave.eu">support-bora@dave.eu</a> for account requests).

Please refer to our Web site at

http://www.dave.eu/dave-cpu-module-zynq-bora.html

for the latest product documentation, utilities, drivers, Product

Change Notifications, Board Support Packages, Application

Notes, mechanical drawings and additional tools and software.

### 1.7 Related documents

| Document                                                     | Location                                                                                       |  |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| DAVE<br>Embedded<br>Systems<br>Developers Wiki               | http://wiki.dave.eu/index.php/Main_Page                                                        |  |  |

| Zynq-7000<br>Technical<br>Reference<br>Manual                | http://www.xilinx.com/support/documen<br>tation/user_guides/ug585-Zynq-7000-TR<br>M.pdf        |  |  |

| Zynq-7000 All<br>Programmable<br>SoC Packaging<br>and Pinout | http://www.xilinx.com/support/documen<br>tation/user_guides/ug865-Zynq-7000-Pk<br>g-Pinout.pdf |  |  |

**Tab. 1**: Related documents

# 1.8 Conventions, Abbreviations, Acronyms

| <b>Abbreviation</b> | Definition                       |

|---------------------|----------------------------------|

| BELK                | BORA Embedded Linux Kit          |

| FSBL                | First stage bootloader           |

| GPI                 | General purpose input            |

| GPIO                | General purpose input and output |

| GPO                 | General purpose output           |

| PCB                 | Printed circuit board            |

| PL                  | Zynq Programmable Logic          |

| PS                  | Zynq Processing System           |

| RTC                 | Real time clock                  |

| SOM                 | System on module                 |

| TRM                 | Technical Reference Manual       |

**Tab. 2**: Abbreviations and acronyms used in this manual

### **Revision History**

| Version | Date           | Notes                                                                                                                                                                                                                                |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.9.0   | July 2013      | First Draft                                                                                                                                                                                                                          |

| 1.0.0   | July 2013      | First Release                                                                                                                                                                                                                        |

| 1.0.1   | May 2014       | Updated block diagram Updated pinout table Updated Sections 5.1 and 5.2 Updated Section 7 (MIO mapping, SD/MMC, UART, I <sup>2</sup> C) Added info on differential pairs Added "Carrier board design guidelines" Section Minor fixes |

| 1.0.2   | August 2014    | Fixed PGOOD description<br>Fixed power-up sequence diagram<br>Minor fixes                                                                                                                                                            |

| 1.0.3   | February 2015  | Updated mechanical drawings for Rev. B SOM Updated information on VDDIO_BANK13 pins Minor fixes                                                                                                                                      |

| 1.0.4   | September 2015 | Added info on thermal IC<br>Minor fixes<br>Released with BELK 2.2.0                                                                                                                                                                  |

# 2 Introduction

BORA is the new top-class Dual Cortex-A9 + FPGA CPU module by **DAVE Embedded Systems**, based on the recent Xilinx Zynq XC7Z010/XC7Z020 application processor.

Thanks to BORA, customers are going to save time and resources by using a compact solution that **includes both a CPU and an FPGA**, avoiding complexities on the carrier PCB.

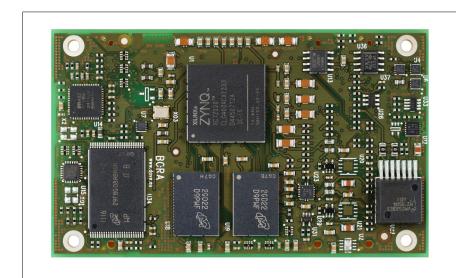

**Fig. 1**: BORA – Powered by Zynq processor

The use of this processor enables extensive system-level differentiation of new applications in many industry fields,

Fig. 2: BORA – Dual ARM Cortex A9 plus FPGA

where high performances and extremely compact form factor (85mm x 50mm) are key factors. Smarter system designs are made possible, following the trends in functionalities and interfaces of the new, state-of-the-art embedded products.

BORA offers great

computational power, thanks to the rich set of peripherals, the Dual Cortex-A9 and the Artix-7 FPGA together with a large set of high-speed I/Os (up to 5GHz).

BORA enables designers to create rugged products suitable for

harsh mechanical and thermal environments, allowing the development of the most advanced and robust products.

Thanks to the tight integration between the ARM-based processing system and the on-chip programmable logic, designers are free to add virtually any peripheral or create custom accelerators that extend system performance and better match specific application requirements.

BORA is designed and manufactured according to **DAVE Embedded Systems ULTRA Line** specifications, in order to guarantee premium quality and technical value for customers who require top performances and flexibility. BORA is suitable for high-end applications such as medical instrumentation, advanced communication systems, critical real-time operations and safety applications.

### 2.1 Product Highlights

- Unmatched performance thanks to dual ARM Cortex-A9 @ 800 MHz

- All memories you need: on-board NOR and NAND Flash

- Enabling smarter system thanks to Artix-7 FPGA integrated on chip

- FPGA banks wide range PSU input from 1.2V to 3.3V

- Highest security and reliability: internal voltage monitoring and power good enable

- Reduced carrier complexity: dual CAN, USB, Ethernet GB and native 3.3V I/O

- Easy to fit thanks to its small form factor

- Precise timing application thanks to on-board 5ppm RTC

Fig. 3: BORA SOM (top view)

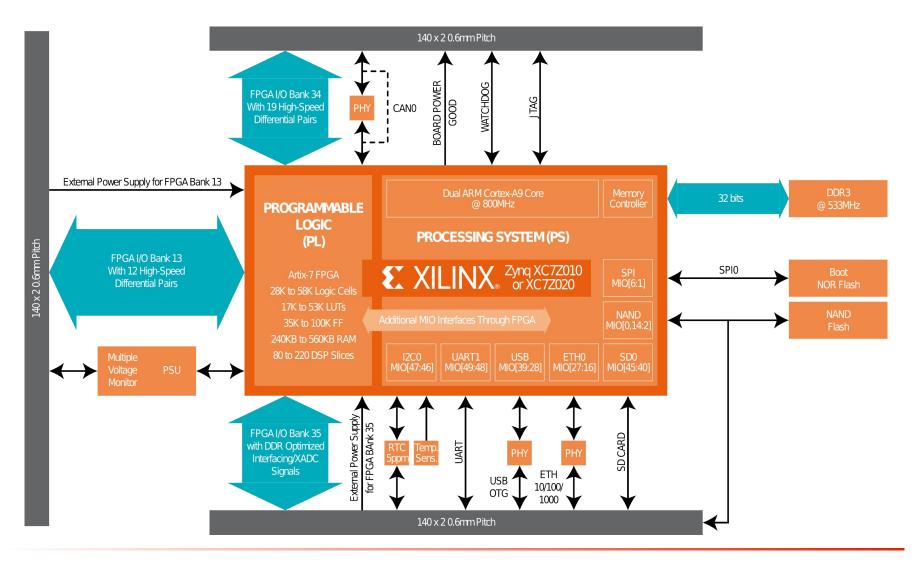

### 2.2 Block Diagram

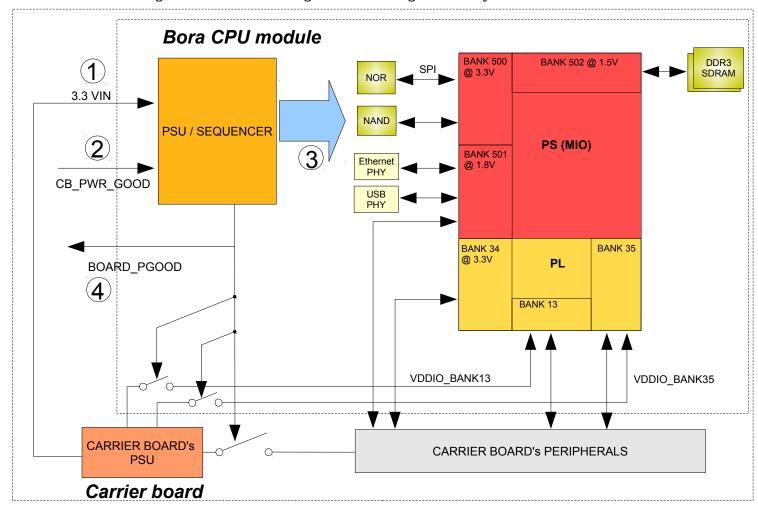

To understand BORA block diagram it is necessary to briefly describe Zynq essential structure and routing scheme. For more details please refer to section 5.7 on page 35 where Xilinx's documentation references are listed.

Zynq is composed by two main blocks: the ARM Cortex-A9 dual-core subsystem – denoted as PS – and the FPGA subsystem – denoted as PL. Besides ARM processors, PS includes some native peripherals such as Gigabit Ethernet MAC controllers, USB controllers etc. PS is fully autonomous, meaning that, no matter if the PL is programmed, it is able to boot as if it was a traditional processor.

From the I/O standpoint, PS has several pads providing flexible multiplexing of native peripherals. These pads are denoted as MIOs and are grouped in some banks denoted as PS 50x.

On the other side, PL subsystem provides a lot of configurable I/Os, grouped in banks denoted as Bank x (eg Bank 9, Bank 13 etc.). Two types of such banks exist: HR<sup>1</sup> and HP<sup>2</sup>.

<sup>1</sup> HR: high range I/O with support for I/O voltage from 1.2V up to 3.3V.

<sup>2</sup> HP: high performance I/O with support for I/O voltage from 1.2V up to 1.8V.

Some of the MIO signals can be routed outside the component via PL subsystem. This technique is called EMIO routing.

The block diagram shows the basic internal interconnections of BORA SoM.

On PS side, the following peripherals and devices are connected to MIO signals:

- Serial NOR flash (MIO [6:1])

- NAND flash (MIO [0], [14:2])

- UART1 (MIO [49:48])

- I2C temperature sensor (MIO [47:46])

- I2C MEMS RTC (MIO [47:46])

- Gigabit Ethernet PHY (MIO [27:16])

- USBOTG PHY (MIO [39:28])

- SD/MMC (MIO [45:40])

Since these devices are considered essential, they have been connected to MIO signals in order to make them always functional, even if PL is not programmed. These peripherals represent the default configuration for the BORA SOM, but other configurations can be implemented changing the pin multiplexing (please refer to section 5.7 on page 35).

Please note that serial NOR flash and NAND flash share some signals. Software drivers need to properly handle this configuration to avoid misuse of these devices.

On PL side, the following devices are connected to I/O signals:

• CAN transceiver (IO\_L6P\_T0\_34, IO\_L19P\_T3\_34).

Any of the CAN controllers of PS subsystem can be connected to CAN transceiver via EMIO routing with no limitations.

## **2.3** Feature Summary

| Feature | Specifications                                                      | Options |

|---------|---------------------------------------------------------------------|---------|

| CPU     | Xilinx Dual ARM Cortex-A9 ZYNQ<br>XC7Z010/XC7Z020 @ 800MHz          |         |

| Cache   | L1: 32Kbyte instruction, 32Kbyte data<br>L2: 512Kbyte for each core |         |

| RAM     | DDR3 SDRAM @ 533 MHz<br>Up to 1 GB                                  |         |

| SRAM    | On-chip RAM, 256 KB                                                 |         |

| Storage | Flash NOR SPI (8, 16, 32 MB)<br>Flash NAND (all sizes, on request)  |         |

**Tab. 3**: CPU, Memories, Buses

| Feature      | Specifications                                                                                             | Options |

|--------------|------------------------------------------------------------------------------------------------------------|---------|

| Coprocessors | NEON™ & Single / Double Precision Floating Point for each processor                                        |         |

| USB          | Up to 2x 2.0 OTG ports                                                                                     |         |

| UARTs        | Up to 2x UART ports                                                                                        |         |

| GPIO         | Up to x lines, shared with other functions (interrupts available)                                          |         |

| Networks     | Gigabit Ethernet 10/100/1000 Mbps<br>Additional GMII/MII interface                                         |         |

| CAN          | 2x full CAN 2.0B compliant interfaces                                                                      |         |

| SD/MMC       | 2x SD/SDIO 2.0/MMC 3.31 compliant controllers                                                              |         |

| Serial buses | 2x full-duplex SPI ports with three peripheral chip selects 2xmaster and slave I <sup>2</sup> C interfaces |         |

| Timers       | 2x triple timers/counters (TTC)                                                                            |         |

| RTC          | On board (DS3232), external battery powered                                                                |         |

| Debug        | JTAG IEEE 1149.1 Test Access Port<br>CoreSight™ and Program Trace<br>Macrocell (PTM)                       |         |

**Tab. 4**: Peripherals

| Feature            | Specifications                                        | Options |

|--------------------|-------------------------------------------------------|---------|

| FPGA model         | Artix™-7                                              |         |

| Logic cells        | 28K to 56K                                            |         |

| LUTs               | 17K to 53K                                            |         |

| Flip flops         | 35K to 100K                                           |         |

| RAM                | 240KB to 560KB                                        |         |

| DSP slices         | 80 to 220                                             |         |

| Differential pairs | Up to 34 differential pairs for high freq. interfaces |         |

**Tab. 5**: FPGA specifications

| Feature                       | Specifications                                       | Options |

|-------------------------------|------------------------------------------------------|---------|

| Supply<br>Voltage             | 3.3V ±5%, on-board voltage regulation                |         |

| Active power consumption      | See section 9.3 - Power consumption                  |         |

| Dimensions                    | 85mm x 50mm                                          |         |

| Weight                        | <tbd></tbd>                                          |         |

| MTBF                          | <tbd></tbd>                                          |         |

| Operating temperature range   | Commercial: 0°C / +70°C<br>Industrial: -40°C / +85°C |         |

| Shock                         | <tbd></tbd>                                          |         |

| Vibration                     | <tbd></tbd>                                          |         |

| Connectors                    | 3 x 140 pins 0.6mm pitch                             |         |

| Connectors insertion/remo val | <tbd></tbd>                                          |         |

Tab. 6: Electrical, Mechanical and Environmental Specifications

# 3 Design overview

The heart of BORA module is composed by the following components:

- Xilinx Zynq Z-7010 (XC7Z010) / Z-7020 (XC7Z020) SoC

- Power supply unit

- DDR memory banks

- NOR and NAND flash banks

- 3x 140 pin connectors with interfaces signals

This chapter shortly describes the main BORA components.

### 3.1 Xilinx Zynq™-7000 SoC

The Zynq<sup>™</sup>-7000 family is based on the Xilinx Extensible Processing Platform (EPP) architecture. These products integrate a feature-rich dual-core ARM® Cortex<sup>™</sup>-A9 based processing system (PS) and 28 nm Xilinx programmable logic (PL) in a single device. The ARM Cortex-A9 CPUs are the heart of the PS and also include on-chip memory, external memory interfaces, and a rich set of peripheral connectivity interfaces.

The Zynq-7000 family offers the flexibility and scalability of an FPGA, while providing performance, power, and ease of use typically associated with ASIC and ASSPs. The range of devices in the Zynq-7000 AP SoC family enables designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. While each device in the Zynq-7000 family contains the same PS, the PL and I/O resources vary between the devices. As a result, the Zynq-7000 AP SoC devices are able to serve a wide range of applications including:

- Automotive driver assistance and driver information

- Infotainment

- Broadcast camera

- Industrial motor control and industrial networking

- Machine vision

- IP and Smart camera

- LTE radio and baseband

- Medical diagnostics and imaging

- Multifunction printers

- Video and night vision equipment

The Zynq-7000 AP SoC is composed of the following major functional blocks:

- Processing System (PS)

- Application processor unit (APU)

- Memory interfaces

- I/O peripherals (IOP)

- Interconnect

- Programmable Logic (PL)

The processors in the PS always boot first, allowing a software centric approach for PL system boot and PL configuration. The PL can be configured as part of the boot process or configured at some point in the future. Additionally, the PL can be completely reconfigured or used with partial, dynamic reconfiguration (PR). PR allows configuration of a portion of the PL. This enables optional design changes such as updating coefficients or time-multiplexing of the PL resources by swapping in new algorithms as needed.

BORA can mount two versions of the Zynq processor. The following table shows a **comparison** between the processor models, highlighting the differences:

| SoC     | Programmab<br>le logic cells | LUTs  | Flip-flo<br>ps | Extensible block RAM |     | Peak DSP performance |

|---------|------------------------------|-------|----------------|----------------------|-----|----------------------|

| XC7Z010 | 28K Logic<br>Cells           | 17600 | 35200          | 240 KB               | 80  | 58 GMACs             |

| XC7Z020 | 85K Logic<br>Cells           | 53200 | 106400         | 560 KB               | 220 | 158 GMACs            |

Tab. 7: XC7-Z0x0 comparison

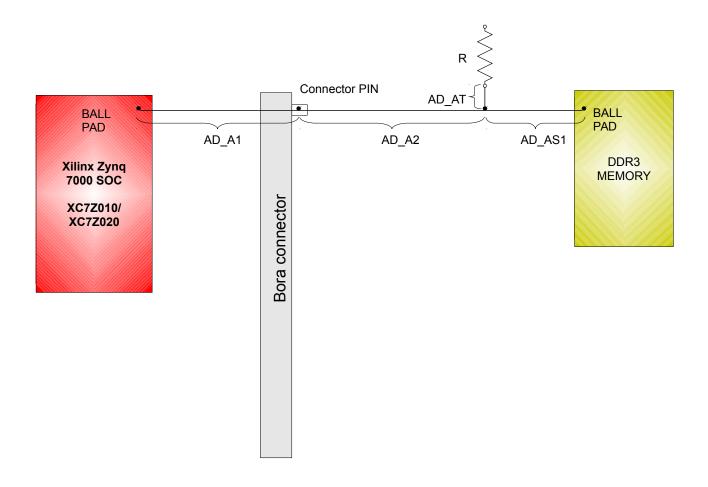

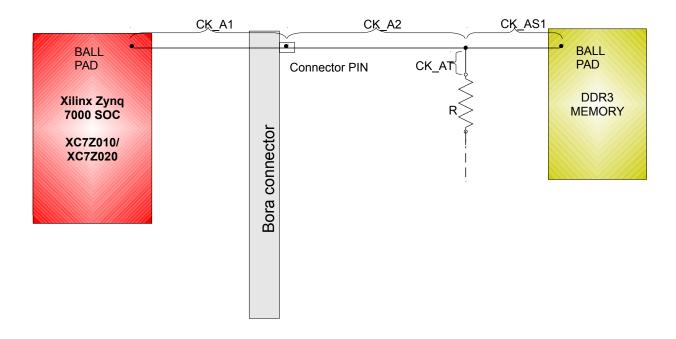

### 3.2 DDR3 memory bank

DDR3 SDRAM memory bank is composed by 2x 16-bit width chips resulting in a 32-bit combined width bank.

The following table reports the SDRAM specifications:

| <b>CPU</b> connection | SDRAM bus |

|-----------------------|-----------|

| Size min              | 512 MB    |

| Size max              | 1 GB      |

| Width                 | 32 bit    |

| Speed                 | 533 MHz   |

Tab. 8: DDR3 specifications

### 3.3 NOR flash bank

NOR flash is a Serial Peripheral Interface (SPI) device. This device is connected to the Quad-SPI channel 0 and by default it acts as boot memory.

The following table reports the NOR flash specifications:

| <b>CPU</b> connection | SPI channel 0 |

|-----------------------|---------------|

| Size min              | 8 MByte       |

| Size max              | 64 MByte      |

| Chip select           | SPI_CS0n      |

| Bootable              | Yes           |

**Tab. 9**: NOR flash specifications

### 3.4 NAND flash bank

On board main storage memory is a 8-bit wide NAND flash connected to the CPU's static memory controller (SMC). Optionally, it can act as boot peripheral.

The following table reports the NAND flash specifications:

| <b>CPU</b> connection | Static memory controller     |

|-----------------------|------------------------------|

| Page size             | 512 byte, 2 kbyte or 4 kbyte |

| Size min              | 128 MByte                    |

| Size max    | 2 GByte  |

|-------------|----------|

| Width       | 8 bit    |

| Chip select | NAND_CS0 |

| Bootable    | Yes      |

**Tab. 10**: NAND flash specifications

### 3.5 Integrated FPGA

The PL is derived from Xilinx's 7 Series FPGA technology (Artix™-7 for the 7z010/7z020). The PL is used to extend the functionality to meet specific application requirements. The PL provides many different types of resources including configurable logic blocks (CLBs), port and width configurable block RAM (BRAM), DSP slices with 25 x 18 multiplier, 48-bit accumulator and pre-adder (DSP48E1), a user configurable analog to digital converter (XADC), clock management tiles (CMT), a configuration block with 256b AES for decryption and SHA for authentication, configurable I/Os (with differential signaling capabilities). BORA customers are able to differentiate their product in hardware by customizing their applications using PL.

### 3.6 Memory Map

For detailed information, please refer to section "4.1 - Address Map" of the Zynq-7000 Technical Reference Manual.

### 3.7 Power supply unit

BORA, as the other ULTRA Line CPU modules, embeds all the elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters. For detailed information, please refer to Section 5.1.

### 3.8 CPU module connectors

All interface signals BORA provides are routed through three

140 pin 0.6mm pitch stacking connectors (named J1, J2 and J3). The dedicated carrier board must mount the mating connectors and connect the desired peripheral interfaces according to BORA pinout specifications.

For mechanical information, please refer to Section 4 (Mechanical specifications). For pinout and peripherals information, please refer to Sections 6 (Pinout table) and 7 (Peripheral interfaces).

# 4 Mechanical specifications

This chapter describes the mechanical characteristics of the BORA module.

Mechanical drawings are available in DXF format from the BORA page on DAVE Embedded Systems website (http://www.dave.eu/products/zyng-bora).

### 4.1 Board Layout

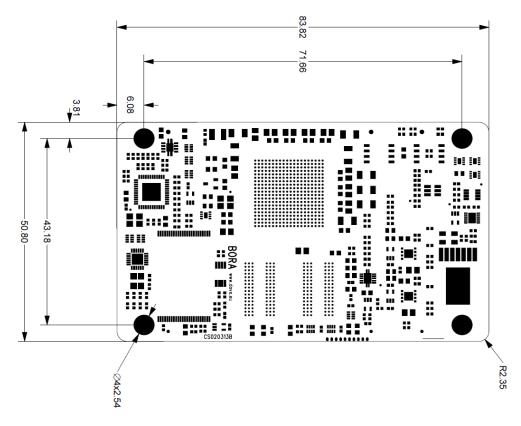

The following figure shows the physical dimensions of the BORA module:

Fig. 4: Board layout - Top view

• Board height: 50.8 mm

• Board width: 83.8 mm

• Maximum components height is less than 4.6 mm.

• PCB thickness is 1.7 mm.

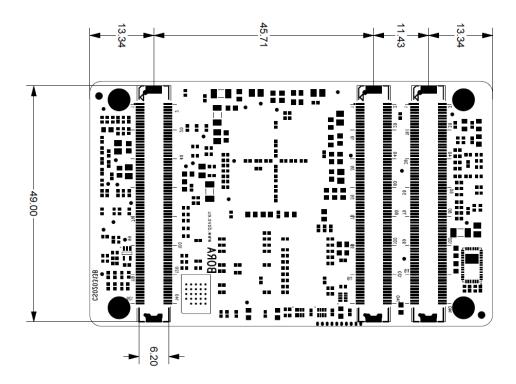

The following figure highlights the maximum components' heights on BORA module:

Fig. 5: Board layout - Side view

### 4.2 Connectors

The following figure shows the BORA connectors layout:

Fig. 6: Connectors layout

The following table reports connectors specifications:

| Part number          | Hirose FX8C-140S-SV                                                                                                                                                                                                                                                   |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Height               | 5.1 mm                                                                                                                                                                                                                                                                |

| Length               | 48.6 mm                                                                                                                                                                                                                                                               |

| Depth                | 4.0 mm                                                                                                                                                                                                                                                                |

| Mating<br>connectors | Hirose FX8C-140P-SV (5 mm board-to-board height)<br>Hirose FX8C-140P-SV1 (6 mm board-to-board height)<br>Hirose FX8C-140P-SV2 (7 mm board-to-board height)<br>Hirose FX8C-140P-SV4 (9 mm board-to-board height)<br>Hirose FX8C-140P-SV6 (11 mm board-to-board height) |

# 5 Power, reset and control

# 5.1 Power Supply Unit (PSU) and recommended power-up sequence

Implementing correct power-up sequence for Zynq-7000 processors is not a trivial task because several power rails are involved. BORA SOM simplifies this task and embeds all the needed circuitry. The following picture shows a simplified block diagram of PSU/voltage monitoring circuitry:

1. main power supply rail (3.3VIN) ramps up

- 2. carrier board circuitry raises CB\_PWR\_GOOD; this indicates 3.3VIN rail is stable<sup>3</sup>

- 3. BORA's PSU enables and sequences DC/DC regulators to turn circuitry on

- 4. BOARD\_PGOOD signal is raised; this active-high signal indicates that SoM's I/O is powered. This signal can be used to manage carrier board power up sequence in order to prevent back powering (from SoM to carrier board or vice versa)

Please note that FPGA Bank 13 and FPGA Bank 35 of the PL must be powered by carrier board even if they are not used to implement any function. Two dedicated power rails are available for this purpose (VDDIO\_BANK35 and VDDIO\_BANK13) and offers the system designer the freedom to select the I/O voltage of these two banks. The power rails of both banks are enabled by the BOARD\_PGOOD signal and are connected to the I/O power supply rail provided by the carrier board.

Bora's PSU is designed to be robust against misbehaving power rails. However, the recommended power-on ramp for core and I/O supplies ranges from 1 to 6 V/ms.

**N.B.**: Regarding power off, it is recommended that I/O supply is turned off before core supply.

September, 2015

This step is not mandatory and CB\_PWR\_GOOD can be left floating. CB\_PWR\_GOOD is provided to prevent, if necessary, BORA's PSU to turn on during ramp of carrier board 3.3VIN rail. Depending on carrier board's PSU design, this may lead to undesired glitches during ramp-up.

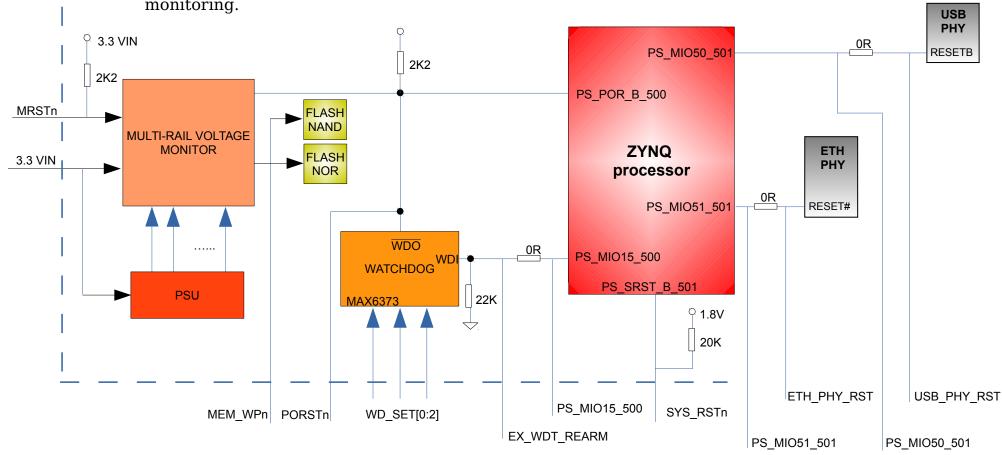

### 5.2 Reset

The following picture shows the simplified block diagram of reset scheme and voltage monitoring.

The available reset signals are described in detail in the following sections.

### 5.2.1 MRST (J2.116)

MRSTn is a de-bounced input for manual reset (for example to connect a push-button). This signal connected to the voltage monitor and is pulled-up to 3.3VIN through a 2.2kOhm resistor.

### 5.2.2 PORSTn (J2.114)

This is a bi-directional open-drain signal that is connected to Zynq's PS\_SRST\_B and can be asserted by the following devices:

- a multi-rail voltage monitor that monitors 3.3VIN power rails and all of the rails generated by BORA's PSU. This monitor:

- in case of a power glitch, asserts MEM\_WPn signal in order to prevent any spurious write operation on flash memories too. MEM\_WPn is 3.3V, push-pull, active low

- has a timeout (set through an on-board capacitor) of about 200 ms

- provides MRSTn de-bounced input for manual reset (for example to connect a push-button). This signal is pulled-up to 3.3VIN through a 2.2kOhm resistor

- a watchdog timer (Maxim MAX6373). For more details please refer to section 5.9 (Watchdog)

PORSTn is pulled-up to 3.3VIN through a 2.2kOhm resistor.

### 5.2.3 SYS\_RSTn (J2.112)

This signal is connected to Zynq's PS\_SRST\_B and is pulled-up to 1.8V through a 20kOhm resistor.

### 5.2.4 PS MIO51 501 (J2.106)

By default, this signal is connected to on-board ETH PHY reset

input. This allows complete software control of PHY reset sequence, even if FPGA is not programmed. In case this signals must be used to implement different functions on carrier board, alternative routing schemes are available on request in order to free this signal. For more details please refer to department sales.

### 5.2.5 PS MIO50 501 (J2.104)

By default, this signal is connected to on-board USB PHY reset input. This allows complete software control of PHY reset sequence, even if FPGA is not programmed. In case this signals must be used to implement different functions on carrier board, alternative routing schemes are available on request in order to free this signal. For more details please refer to department sales.

### **5.3** Voltage monitor

The voltage monitor is a Linear Technology LTC2930 (Configurable Six Supply Monitor with Adjustable Reset Timer, Manual Reset).

### 5.4 System boot

The boot process is multi-stage and minimally includes the Boot ROM and the first-stage boot loader (FSBL). The Zynq-7000 AP SoC includes a factory-programmed Boot ROM that is not user-accessible. The boot ROM:

- determines whether the boot is secure or non-secure

- performs some initialization of the system and clean-ups

- reads the mode pins to determine the primary boot device

- once it is satisfied, it executes the FSBL

After a system reset, the system automatically sequences to initialize the system and process the first stage boot loader from the selected external boot device. The process enables the user to configure the AP SoC platform as needed, including the

PS and the PL. Optionally, the JTAG interface can be enabled to give the design engineer access to the PS and the PL for test and debug purposes.

#### 5.4.1 Boot modes

The boot ROM supports configuration from four different slave interfaces:

- Quad-SPI

- NAND

- NOR flash (not available on BORA)

- SD card

Boot mode is selectable via five mode pins (BOOT\_MODE[4:0]), and two voltage mode signals, (VMODE[1:0]). The BOOT\_MODE pins are MIO[6:2] and the VMODE pins are MIO[8:7]. The pins are used as follows:

| Function              | <b>Boot signals</b>          | Available options                                       |

|-----------------------|------------------------------|---------------------------------------------------------|

| JTAG mode             | BOOT_MODE[3]<br>MIO[2]       | 0: Cascaded JTAG<br>1: Independent JTAG                 |

| Boot mode             | BOOT_MODE[0-2-1]<br>MIO[5:3] | 000: JTAG<br>010: NAND<br>100: Quad-SPI<br>110: SD card |

| PLLs enable           | BOOT_MODE[4]<br>MIO[6]       | 0: PLL used<br>1: PLL bypassed                          |

| MIO Bank 0<br>Voltage | VMODE[0]<br>MIO[7]           | 0: 2.5 V, 3.3 V<br>1: 1.8 V                             |

| MIO Bank 0<br>Voltage | VMODE[1]<br>MIO[8]           | 0: 2.5 V, 3.3 V<br>1: 1.8 V                             |

In order to fully understand how boot works on BORA platform, please refer to chapter 6 ("Boot and configuration") of the Zyng-7000 Technical Reference Manual.

### 5.4.2 Default boot configuration

Default configuration for BORA module is:

- Mode[0..3] = 1000: Quad-SPI mode

- Mode[4] = 0: PLL not bypassed

- VCFG[0] = 0: 2.5V, 3.3V operations for bank 0

- VCFG[1] = 1: 1.8 operations for bank 1

Assuming that:

- default configuration is not changed,

- there's a valid boot code programmed in SPI flash memory

the actual boot sequence performed by ARM core will be:

- 5. Bootrom is executed from internal ROM code memory

- 6. FSBL is copied from on-board NOR flash memory connected to SPI0 port to on-chip SRAM by bootrom

- 7. FSBL is executed from on-chip SRAM

- 8. U-Boot bootloader (2nd stage) is copied by FSBL from NOR flash memory connected to Quad-SPI port to SDRAM

- 9. U-boot (2nd stage) is executed from SDRAM

If no boot code is available in SPI NOR flash, the bootrom tries JTAG peripheral booting.

### 5.4.3 Boot sequence customization

BOOT\_MODE[4:0] are routed to the J1 connector, enabling for the customization of the boot sequence through a simple resistor network that can be implemented on carrier board hosting BORA module.

| <b>Mode signal</b> | J1 pin | Pin name                 |

|--------------------|--------|--------------------------|

| BOOT_MODE[4]       | J1.129 | SPI0_SCLK/MODE4/NAND_IO1 |

| BOOT_MODE[3]       | J1.125 | SPI0_DQ0/MODE3/NAND_ALE  |

| <b>Mode signal</b> | J1 pin | Pin name                |

|--------------------|--------|-------------------------|

| BOOT_MODE[2]       | J1.121 | SPI0_DQ2/MODE2/NAND_IO2 |

| BOOT_MODE[1]       | J1.123 | SPI0_DQ1/MODE1/NAND_WE  |

| BOOT_MODE[0]       | J1.119 | SPI0_DQ3/MODE0/NAND_IO0 |

For each BOOT\_MODE[4:0] pin it is possible to populate upper or lower side resistor in order to change default value that is set on module itself.

### 5.5 Clock scheme

Bora is equipped with three independent active oscillators:

- processor (33.3 MHz)

- ethernet PHY (25 MHz)

- USB PHY (26 MHz)

Generally speaking, no clocks have to be provided by carrier board.

### 5.6 Recovery

For different reason, starting from image corruption due power loss during upgrade or unrecoverable bug while developing a new U-Boot feature, the user will need, sooner or later, to recover (*bare-metal* restore) the BORA SOM without using the bootloader itself. The following paragraphs introduce the available options. For further information, please refer to **DAVE Embedded Systems** Developers Wiki or contact the Technical Support Team.

### 5.6.1 JTAG Recovery

JTAG recovery, though very useful (especially in development or production environment), requires dedicated hardware and software tools. BORA provides the JTAG interface, which, besides the debug purpose, can be used for programming and recovery operations. For further information on how to use the JTAG interface, please contact the Technical Support Team.

### 5.6.2 SD/MMC Recovery

SD/MMC recovery is a valuable options that requires no special hardware at all, apart a properly formatted SD/MMC. The boot sequence must include the SD/MMC option and a way to enable it. When SD/MMC boot option is selected, bootrom looks for a valid FSBL on SD/MMC, which in turn will load the 2nd stage bootloader. Once the board is running after booting from SD, reprogramming the flash memory is straightforward.

### 5.7 Multiplexing

The PS I/O peripherals, including the static/flash memory interfaces share a multiplexed I/O (MIO) of up to 54 MIO pins. Zynq-7000 AP SoC devices also include the capability to use the I/Os that are part of the PL domain for many of the PS I/O Peripherals. This is done through an extended multiplexed I/O interface (EMIO) and is useful to gain access to more device pins (PL pins) and to allow an I/O peripheral controller to interface to user logic in the PL.

The MIO is fundamental to the I/O peripheral connections due to the limited number of MIO pins. Software programs the routing of the I/O signals to the MIO/EMIO pins. Normally, each pin is assigned to one function. One exception to this is the dual use boot mode strapping resistors (MIO [2:8]).

Please refer to the following sections of the Zynq-7000 TRM for further information on MIO/EMIO pin assignment:

- section 2.5.1 "I/O Peripheral (IOP) Interface Routing"

- section 2.5.3 "MIO Pin Assignment Considerations"

- section 2.5.4 "MIO-at-a-Glance Table"

- section 2.5.5 "MIO Signal Routing"

### **5.8** RTC

An on-board Maxim Integrated DS3232 device provides a very accurate, temperature-compensated real-time clock (RTC) resource with:

- Temperature-compensated crystal oscillator

- Date, time and calendar

- Alarm capability

- Backup power from external battery

- ±3.5ppm accuracy from -40°C to +85°C

- 236 Bytes of Battery-Backed SRAM

- I<sup>2</sup>C Interface

Backup power is provided through the RTC\_VBAT (J2.113) signal. If not used, RTC\_VBAT must be externally connected to GND. For a detailed description of RTC characteristics, please refer to the DS3232 datasheet.

### 5.9 Watchdog

An external watchdog (Maxim MAX6373) is connected to the PORSTn signal. During normal operation, the microprocessor should repeatedly toggle the watchdog input WDI before the selected watchdog timeout period elapses to demonstrate that the system is processing code properly. If the  $\mu P$  does not provide a valid watchdog input transition before the timeout period expires, the supervisor asserts a watchdog (WDO) output to signal that the system is not executing the desired instructions within the expected time frame. The watchdog output pulse is used to reset the  $\mu P$ . By default WDI is connected to Zynq's PS\_MIO15\_500 I/O. WDI is available on BORA connectors as EX\_WDT\_REARM. EX\_WDT\_REARM is pulled-down through a 22kOhm resistor.

On request, PS\_MIO15\_500 can be disconnected from WDI (please contact Sales Department for more details). This configuration provides two independent signals (EX\_WDT\_REAM and PS\_MIO15\_500) that allow the implementation of customized solutions on carrier board. For example you may want to use the Zynq's System Watchdog Timer (SWDT) instead of MAX6373 to reset the system through PS\_MIO15\_500 that can be configured as SWDT reset.

The MAX6373 watchdog timer is pin-selectable and the timer

can be configured through the WD\_SET0 (J1.7), WD\_SET1 (J1.9) and WD\_SET2 (J1.11) signals. As a default, the watchdog is configured through a pull-up/pull-down resistors network (WD\_SET[2..0] = 110) that keeps the watchdog timer inactive at startup. Startup delay ends when WDI sees its first level transition. The default watchdog timeout period is 10 s.

The configuration can be changed by optional external circuitry implemented on the carrier board.

#### 5.10 Thermal IC

An on-board thermal IC (Texas Instruments TMP421) connected to the I<sup>2</sup>C0 interface can work as a local temperature sensor, providing the measurement of its internal temperature, but also as a remote temperature sensor, since it is connected to the XADC\_DXP/XADC\_DXN of the Zynq processor, providing the measurement of the Zynq internal temperature.

For a detailed description of the thermal IC characteristics, please refer to the TMP421 datasheet.

## 6 Pinout table

This chapter contains the pinout description of the BORA module, grouped in six tables (two – odd and even pins – for each connector) that report the pin mapping of the three 140-pin BORA connectors.

Each row in the pinout tables contains the following information:

| Pin                     | Reference to the connector pin                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                | Pin (signal) name on the BORA connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Internal<br>Connections | Connections to the BORA components:  CPU. <x>: pin connected to CPU (PS, processing system) pad named <x> FPGA.<x>: pin connected to FPGA (PL, programmable logic) pad named <x> CAN.<x>: pin connected to the CAN transceiver PMIC.<x>: pin connected to the Power Manager IC LAN.<x>: pin connected to the LAN PHY USB.<x>: pin connected to the USB transceiver SV.<x>: pin connected to voltage supervisor MTR: pin connected to voltage monitors</x></x></x></x></x></x></x></x></x> |

| Ball/pin #              | Component ball/pin number connected to signal                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Supply Group</b>     | Power Supply Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Туре                    | Pin type: I = Input, O = Output, D= Differential, Z = High impedance, S = Supply voltage, G = Ground, A = Analog signal                                                                                                                                                                                                                                                                                                                                                                   |

| Voltage                 | I/O voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## **6.1** Carrier board mating connector J1

|       |                         | J1 - ODE                     | [1 - 1         | 39]             |      |         |      |

|-------|-------------------------|------------------------------|----------------|-----------------|------|---------|------|

| Pin   | Pin Name                | Internal Connections         | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note |

| J1.1  | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.3  | IO_L7P_T1_AD2P_35       | FPGA.IO_L7P_T1_AD2P_35       | M19            | BANK35          | I/O  |         |      |

| J1.5  | IO_L10P_T1_AD11P_35     | FPGA.IO_L10P_T1_AD11P_35     | K19            | BANK35          | I/O  |         |      |

| J1.7  | IO_L11P_T1_SRCC_35      | FPGA.IO_L11P_T1_SRCC_35      | L16            | BANK35          | I/O  |         |      |

| J1.9  | IO_L8N_T1_AD10N_35      | FPGA.IO_L8N_T1_AD10N_35      | M18            | BANK35          | I/O  |         |      |

| J1.11 | IO_L7N_T1_AD2N_35       | FPGA.IO_L7N_T1_AD2N_35       | M20            | BANK35          | I/O  |         |      |

| J1.13 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.15 | IO_L9P_T1_DQS_AD3P_35   | FPGA.IO_L9P_T1_DQS_AD3P_35   | L19            | BANK35          | I/O  |         |      |

| J1.17 | IO_L9N_T1_DQS_AD3N_35   | FPGA.IO_L9N_T1_DQS_AD3N_35   | L20            | BANK35          | I/O  |         |      |

| J1.19 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.21 | IO_L20P_T3_AD6P_35      | FPGA.IO_L20P_T3_AD6P_35      | K14            | BANK35          | I/O  |         |      |

| J1.23 | IO_L20N_T3_AD6N_35      | FPGA.IO_L20N_T3_AD6N_35      | J14            | BANK35          | I/O  |         |      |

| J1.25 | IO_L22P_T3_AD7P_35      | FPGA.IO_L22P_T3_AD7P_35      | L14            | BANK35          | I/O  |         |      |

| J1.27 | IO_L12N_T1_MRCC_35      | FPGA.IO_L12N_T1_MRCC_35      | K18            | BANK35          | I/O  |         |      |

| J1.29 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.31 | IO_L21P_T3_DQS_AD14P_35 | FPGA.IO_L21P_T3_DQS_AD14P_35 | N15            | BANK35          | I/O  |         |      |

| J1.33 | IO_L21N_T3_DQS_AD14N_35 | FPGA.IO_L21N_T3_DQS_AD14N_35 | N16            | BANK35          | I/O  |         |      |

| J1.35 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.37 | IO_L17N_T2_AD5N_35      | FPGA.IO_L17N_T2_AD5N_35      | H20            | BANK35          | I/O  |         |      |

| J1.39 | IO_L13N_T2_MRCC_35      | FPGA.IO_L13N_T2_MRCC_35      | H17            | BANK35          | I/O  |         |      |

| J1.41 | IO_L19P_T3_35           | FPGA.IO_L19P_T3_35           | H15            | BANK35          | I/O  |         |      |

| J1.43 | IO_L18P_T2_AD13P_35     | FPGA.IO_L18P_T2_AD13P_35     | G19            | BANK35          | I/O  |         |      |

| J1.45 | IO_L16P_T2_35           | FPGA.IO_L16P_T2_35           | G17            | BANK35          | I/O  |         |      |

| J1.47 | IO_L15N_T2_DQS_AD12N_35 | FPGA.IO_L15N_T2_DQS_AD12N_35 | F20            | BANK35          | I/O  |         |      |

| J1.49 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.51 | IO_L2N_T0_AD8N_35       | FPGA.IO_L2N_T0_AD8N_35       | A20            | BANK35          | I/O  |         |      |

| J1.53 | IO_L1N_T0_AD0N_35       | FPGA.IO_L1N_T0_AD0N_35       | B20            | BANK35          | I/O  |         |      |

| J1.55 | IO_L5N_T0_AD9N_35       | FPGA.IO_L5N_T0_AD9N_35       | E19            | BANK35          | I/O  |         |      |

| J1.57 | IO_L5P_T0_AD9P_35       | FPGA.IO_L5P_T0_AD9P_35       | E18            | BANK35          | I/O  |         |      |

| J1.59 | DGND                    | DGND                         | -              |                 | -    |         |      |

|        |                       | J1 - OD                    | D [1 - 1       | .39]            |      |         |                                      |

|--------|-----------------------|----------------------------|----------------|-----------------|------|---------|--------------------------------------|

| Pin    | Pin Name              | Internal Connections       | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note                                 |

| J1.61  | IO_L3P_T0_DQS_AD1P_35 | FPGA.IO L3P TO DQS AD1P 35 | E17            | BANK35          | I/O  |         |                                      |

| J1.63  | IO L3N TO DQS AD1N 35 | FPGA.IO L3N TO DQS AD1N 35 | D18            | BANK35          | I/O  |         |                                      |

| J1.65  | DGND                  | DGND                       | -              |                 | -    |         |                                      |

| J1.67  | VDDIO_BANK35          | FPGA.VCCO_35               | C19            | BANK35          | VCCO | U.D.    | 1.8V to 3.3V                         |

|        |                       |                            | F18            |                 |      |         | User defined (U.D.)                  |

|        |                       |                            | H14            |                 |      |         |                                      |

|        |                       |                            | J17            |                 |      |         |                                      |

|        |                       |                            | K20            |                 |      |         |                                      |

|        |                       |                            | M16            |                 |      |         |                                      |

| J1.69  | XADC_AGND             | FPGA.GNDADC_0              | J10            |                 | -    |         |                                      |

| J1.71  | XADC_AGND             | FPGA.GNDADC_0              | J10            |                 | -    |         |                                      |

| J1.73  | PS_SD0_DAT3           | CPU.PS_MIO45_501           | B15            | BANK501         | I/O  | 1.8V    |                                      |

| J1.75  | PS_SD0_DAT2           | CPU.PS_MIO44_501           | F13            | BANK501         | I/O  | 1.8V    |                                      |

| J1.77  | PS_SD0_DAT1           | CPU.PS_MIO43_501           | A9             | BANK501         | I/O  | 1.8V    |                                      |

| J1.79  | PS_SD0_DAT0           | CPU.PS_MIO42_501           | E12            | BANK501         | I/O  | 1.8V    |                                      |

| J1.81  | PS_SD0_CMD            | CPU.PS_MIO41_501           | C17            | BANK501         | I/O  | 1.8V    |                                      |

| J1.83  | DGND                  | DGND                       | -              |                 | -    |         |                                      |

| J1.85  | PS_SD0_CLOCK          | CPU.PS_MIO40_501           | D14            | BANK501         | I/O  | 1.8V    |                                      |

| J1.87  | ETH_MDIO              | CPU.PS_MIO53_501           | C11            | BANK501         | I/O  | 1.8V    |                                      |

|        |                       | LAN.MDIO                   | 37             |                 |      |         |                                      |

| J1.89  | ETH_MDC               | CPU.PS_MIO12_501           | C10            | BANK501         |      | 1.8V    |                                      |

| 17.07  | 5711.1504             | LAN.MDC                    | 36             |                 |      |         |                                      |

| J1.91  | ETH_LED1              | LAN.LED1 / PME_N1          | 17             |                 |      |         |                                      |

| J1.93  | ETH_LED2              | LAN.LED2                   | 15             |                 |      |         |                                      |

| J1.95  | DGND                  | DGND                       | -              |                 | -    |         |                                      |

| J1.97  | ETH_TXRX1_M           | LAN.TXRXM_B                | 6              |                 |      |         |                                      |

| J1.99  | ETH_TXRX1_P           | LAN.TXRXP_B                | 5              |                 |      |         |                                      |

| J1.101 | DGND                  | DGND                       | -              |                 |      |         |                                      |

| J1.103 | ETH_TXRXO_M           | LAN.TXRXM_A                | 3              |                 |      |         |                                      |

| J1.105 | ETH_TXRX0_P           | LAN.TXRXP A                | 2              |                 |      | 1.0)/   | 1.01/ 4: -: 1.700 1/0 6.5-1          |

| J1.107 | DVDDH                 | LAN.DVDDH                  | 16             |                 |      | 1.8V    | 1.8V digital VDD_I/O of Ethernet PHY |

|        |                       |                            | 34             |                 |      |         |                                      |

| 11 100 | N.C.                  | Not Composted              | 40             |                 |      |         |                                      |

| J1.109 |                       | Not Connected              | -              |                 |      |         |                                      |

| JI.III | USBOTG_CPEN           | USB.CPEN                   | 7              |                 |      |         |                                      |

|        | J1 - ODD [1 - 139]       |                      |                |                 |      |         |                                                                                               |  |  |  |

|--------|--------------------------|----------------------|----------------|-----------------|------|---------|-----------------------------------------------------------------------------------------------|--|--|--|

| Pin    | Pin Name                 | Internal Connections | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note                                                                                          |  |  |  |

| J1.113 | OTG_VBUS                 | USB.OTG_VBUS         | 2              |                 |      |         |                                                                                               |  |  |  |

| J1.115 | OTG_ID                   | USB.ID               | 1              |                 |      |         |                                                                                               |  |  |  |

| J1.117 | DGND                     | DGND                 | -              |                 |      |         |                                                                                               |  |  |  |

| J1.119 | SPI0_DQ3/MODE0/NAND_IO0  | CPU.PS_MIO5_500      | A6             | BANK500         |      | 3.3V    | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. |  |  |  |

| J1.121 | SPI0_DQ2/MODE2/NAND_IO2  | CPU.PS_MIO4_500      | В7             | BANK500         |      | 3.3V    | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. |  |  |  |

| J1.123 | SPI0_DQ1/MODE1/NAND_WE   | CPU.PS_MIO3_500      | D6             | BANK500         |      | 3.3V    | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. |  |  |  |

| J1.125 | SPI0_DQ0/MODE3/NAND_ALE  | CPU.PS_MIO2_500      | B8             | BANK500         |      | 3.3V    | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. |  |  |  |

| J1.127 | DGND                     | DGND                 | -              |                 |      |         |                                                                                               |  |  |  |

| J1.129 | SPI0_SCLK/MODE4/NAND_IO1 | CPU.PS_MIO6_500      | A5             | BANK500         |      | 3.3V    | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. |  |  |  |

| J1.131 | NAND_BUSY                | CPU.PS_MIO14_500     | C5             | BANK500         |      | 3.3V    |                                                                                               |  |  |  |

| J1.133 | PS_MIO15_500             | CPU.PS_MIO15_500     | C8             | BANK500         |      | 3.3V    |                                                                                               |  |  |  |

|        |                          | WDT.WDI              | 1              | -               |      | 3.3V    |                                                                                               |  |  |  |

| J1.135 | N.C.                     | Not Connected        | -              |                 |      |         |                                                                                               |  |  |  |

| J1.137 | MEM_WPN                  | NAND.WP              | 19             |                 |      |         |                                                                                               |  |  |  |

|        |                          | NOR.WP/IO2           | C4             |                 |      |         |                                                                                               |  |  |  |

| J1.139 | DGND                     | DGND                 | -              |                 |      |         |                                                                                               |  |  |  |

| J1 - EVEN [2 - 140] |              |                      |                |                 |      |         |                                     |  |

|---------------------|--------------|----------------------|----------------|-----------------|------|---------|-------------------------------------|--|

| Pin                 | Pin Name     | Internal Connections | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note                                |  |

| J1.2                | VDDIO_BANK35 | FPGA.VCCO_35         | Č19<br>F18     | BANK35          | VCCO | U.D.    | 1.8V to 3.3V<br>User defined (U.D.) |  |

|       |                         | J1 – EVE                     | N [2 - ]       | 140]            |      |         |      |

|-------|-------------------------|------------------------------|----------------|-----------------|------|---------|------|

| Pin   | Pin Name                | Internal Connections         | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note |

|       |                         |                              | H14            |                 |      |         |      |

|       |                         |                              | J17            |                 |      |         |      |

|       |                         |                              | K20            |                 |      |         |      |

|       |                         |                              | M16            |                 |      |         |      |

| J1.4  | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.6  | IO_L10N_T1_AD11N_35     | FPGA.IO_L10N_T1_AD11N_35     | J19            | BANK35          | I/O  | U.D.    |      |

| J1.8  | IO_L12P_T1_MRCC_35      | FPGA.IO_L12P_T1_MRCC_35      | K17            | BANK35          | I/O  | U.D.    |      |

| J1.10 | IO L11N T1 SRCC 35      | FPGA.IO L11N T1 SRCC 35      | L17            | BANK35          | I/O  | U.D.    |      |

| J1.12 | IO_L8P_T1_AD10P_35      | FPGA.IO_L8P_T1_AD10P_35      | M17            | BANK35          | I/O  | U.D.    |      |

| J1.14 | DGND                    | DGND                         | -              |                 |      |         |      |

| J1.16 | IO L24N T3 AD15N 35     | FPGA.IO L24N T3 AD15N 35     | J16            | BANK35          | I/O  | U.D.    |      |

| ]1.18 | IO 25 35                | FPGA.IO 25 35                | J15            | BANK35          | I/O  | U.D.    |      |

| J1.20 | IO L24P T3 AD15P 35     | FPGA.IO L24P T3 AD15P 35     | K16            | BANK35          | I/O  | U.D.    |      |

| J1.22 | IO L23N T3 35           | FPGA.IO L23N T3 35           | M15            | BANK35          | I/O  | U.D.    |      |

| J1.24 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.26 | IO L22N T3 AD7N 35      | FPGA.IO L22N T3 AD7N 35      | L15            | BANK35          | I/O  | U.D.    |      |

| J1.28 | IO L23P T3 35           | FPGA.IO L23P T3 35           | M14            | BANK35          | I/O  | U.D.    |      |

| J1.30 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.32 | IO L17P T2 AD5P 35      | FPGA.IO L17P T2 AD5P 35      | 120            | BANK35          | I/O  | U.D.    |      |

| J1.34 | IO L14P T2 AD4P SRCC 35 | FPGA.IO L14P T2 AD4P SRCC 35 | 118            | BANK35          | 1/0  | U.D.    |      |

| J1.36 | IO L14N T2 AD4N SRCC 35 | FPGA.IO L14N T2 AD4N SRCC 35 | H18            | BANK35          | 1/0  | U.D.    |      |

| J1.38 | DGND                    | DGND                         | -              |                 | -    |         |      |

| J1.40 | IO L13P T2 MRCC 35      | FPGA.IO L13P T2 MRCC 35      | H16            | BANK35          | 1/0  | U.D.    |      |

| J1.42 | IO L18N T2 AD13N 35     | FPGA.IO L18N T2 AD13N 35     | G20            | BANK35          | 1/0  | U.D.    |      |

| J1.44 | IO L16N T2 35           | FPGA.IO L16N T2 35           | G18            | BANK35          | 1/0  | U.D.    |      |

| J1.46 | IO_L15P_T2_DQS_AD12P_35 | FPGA.IO L15P T2 DQS AD12P 35 | F19            | BANK35          | 1/0  | U.D.    |      |

| J1.48 | DGND                    | DGND                         | 1 -            |                 | -    |         |      |

| J1.50 | IO L1P TO ADOP 35       | FPGA.IO L1P TO ADOP 35       | C20            | BANK35          | I/O  | U.D.    |      |

| J1.52 | IO L2P T0 AD8P 35       | FPGA.IO L2P TO AD8P 35       | B19            | BANK35          | 1/0  | U.D.    |      |

| J1.54 | IO L4N T0 35            | FPGA.IO L4N TO 35            | D20            | BANK35          | I/O  | U.D.    |      |

| J1.56 | IO L4P T0 35            | FPGA.IO L4P TO 35            | D19            | BANK35          | 1/0  | U.D.    |      |

| J1.58 | IO L6P T0 35            | FPGA.IO L6P TO 35            | F16            | BANK35          | 1/0  | U.D.    |      |

| J1.60 | DGND                    | DGND                         | -              |                 | 1-   |         |      |

| 11.62 | IO L6N TO VREF 35       | FPGA.IO L6N T0 VREF 35       | F17            | BANK35          | 1/0  | U.D.    |      |

| J1.64 | IO L19N T3 VREF 35      | FPGA.IO L19N T3 VREF 35      | G15            | BANK35          | I/O  | U.D.    |      |

|        |              | J1 – El              | VEN [2 - 1                             | 140]            |      |         |                                     |

|--------|--------------|----------------------|----------------------------------------|-----------------|------|---------|-------------------------------------|

| Pin    | Pin Name     | Internal Connections | Ball/<br>pin #                         | Supply<br>Group | Туре | Voltage | Note                                |

| J1.66  | VDDIO_BANK35 | FPGA.VCCO_35         | C19<br>F18<br>H14<br>J17<br>K20<br>M16 | BANK35          | VCCO | U.D.    | 1.8V to 3.3V<br>User defined (U.D.) |

| J1.68  | VDDIO_BANK35 | FPGA.VCCO_35         | C19<br>F18<br>H14<br>J17<br>K20<br>M16 | BANK35          | VCCO | U.D.    | 1.8V to 3.3V<br>User defined (U.D.) |

| J1.70  | XADC_AGND    | FPGA.GNDADC_0        | J10                                    |                 |      |         |                                     |

| J1.72  | XADC_AGND    | FPGA.GNDADC_0        | J10                                    |                 |      |         |                                     |

| J1.74  | IO_0_35      | FPGA.IO_0_35         | G14                                    | BANK35          | I/O  | U.D.    |                                     |

| J1.76  | N.C.         | Not Connected        | -                                      | BANK501         | I/O  | 1.8V    |                                     |

| J1.78  | N.C.         | Not Connected        | -                                      | BANK501         | I/O  | 1.8V    |                                     |

| J1.80  | PS_UART1_RX  | CPU.PS_MIO49_501     | C12                                    | BANK501         | I/O  | 1.8V    |                                     |

| J1.82  | PS_UART1_TX  | CPU.PS_MIO48_501     | B12                                    | BANK501         | I/O  | 1.8V    |                                     |

| J1.84  | PS I2C0 DAT  | CPU.PS MIO47 501     | B14                                    | BANK501         | I/O  | 1.8V    |                                     |

| J1.86  | DGND         | DGND                 | -                                      |                 | -    |         |                                     |

| J1.88  | PS I2C0 CK   | CPU.PS MIO46 501     | D16                                    | BANK501         | I/O  | 1.8V    |                                     |

| J1.90  | ETH INTN     | LAN.INT N / PME N2   | 38                                     |                 |      |         |                                     |

| J1.92  | DGND         | DGND                 | -                                      |                 | -    |         |                                     |

| J1.94  | ETH TXRX3 M  | LAN.TXRXM D          | 11                                     |                 |      |         |                                     |

| J1.96  | ETH TXRX3 P  | LAN.TXRXP D          | 10                                     |                 |      |         |                                     |

| J1.98  | DGND         | DGND                 | -                                      |                 |      |         |                                     |

| J1.100 | ETH TXRX2 M  | LAN.TXRXM C          | 8                                      |                 |      |         |                                     |

| J1.102 | ETH TXRX2 P  | LAN.TXRXP C          | 7                                      |                 |      |         |                                     |

| J1.104 | DGND         | DGND                 | -                                      |                 | -    |         |                                     |

| J1.106 | CLK125 NDO   | LAN.CLK125 NDO       | 41                                     |                 |      |         |                                     |

| J1.108 | N.C.         | Not Connected        | -                                      |                 |      |         |                                     |

| J1.110 | N.C.         | Not Connected        | -                                      |                 |      |         |                                     |

| J1.112 | DGND         | DGND                 | -                                      |                 |      |         |                                     |

| J1.114 | USBP1        | USB.DP               | 6                                      |                 |      |         |                                     |

|        | J1 - EVEN [2 - 140] |                      |                |                 |      |         |                                                           |  |  |  |  |

|--------|---------------------|----------------------|----------------|-----------------|------|---------|-----------------------------------------------------------|--|--|--|--|

| Pin    | Pin Name            | Internal Connections | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note                                                      |  |  |  |  |

| J1.116 | USBM1               | USB.DM               | 5              |                 |      |         |                                                           |  |  |  |  |

| J1.118 | DGND                | DGND                 | -              |                 | -    |         |                                                           |  |  |  |  |

| J1.120 | SPIO_CSON           | CPU.PS_MIO1_500      | A7             | BANK500         |      | 3.3V    |                                                           |  |  |  |  |

|        | _                   | NOR.CS#              | C2             |                 |      |         |                                                           |  |  |  |  |

| J1.122 | NAND CS0/SPI0 CS1   | CPU.PS_MIO0_500      | E6             | BANK500         |      | 3.3V    |                                                           |  |  |  |  |

|        |                     | NAND.CE#             | 9              |                 |      |         |                                                           |  |  |  |  |

| J1.124 | NAND IO3            | CPU.PS MIO13 500     | E8             | BANK500         | I/O  | 3.3V    |                                                           |  |  |  |  |